Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, может быть использовано для построения телевизионных систем анализа изображений и является усовершенствованием известного устройства по авт.св. 1116458.

Целью изобретения является сокра- щение аппаратурных затрат при записи фрагментов изображений, разделенных во времени.

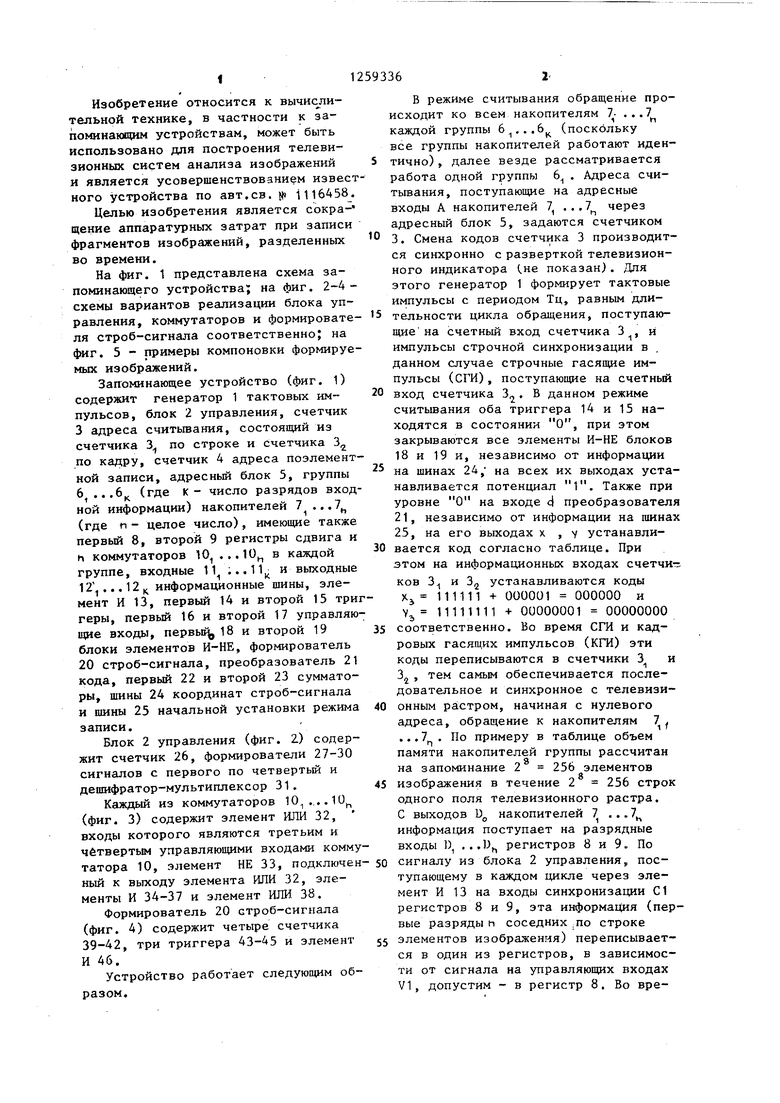

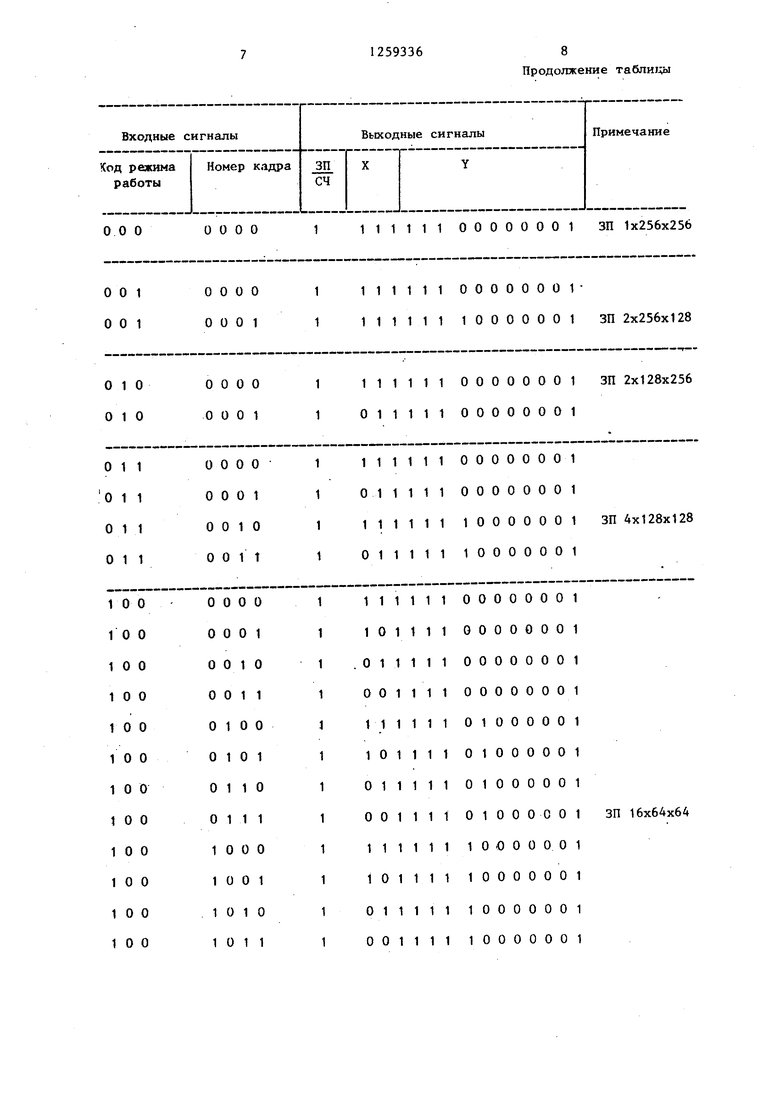

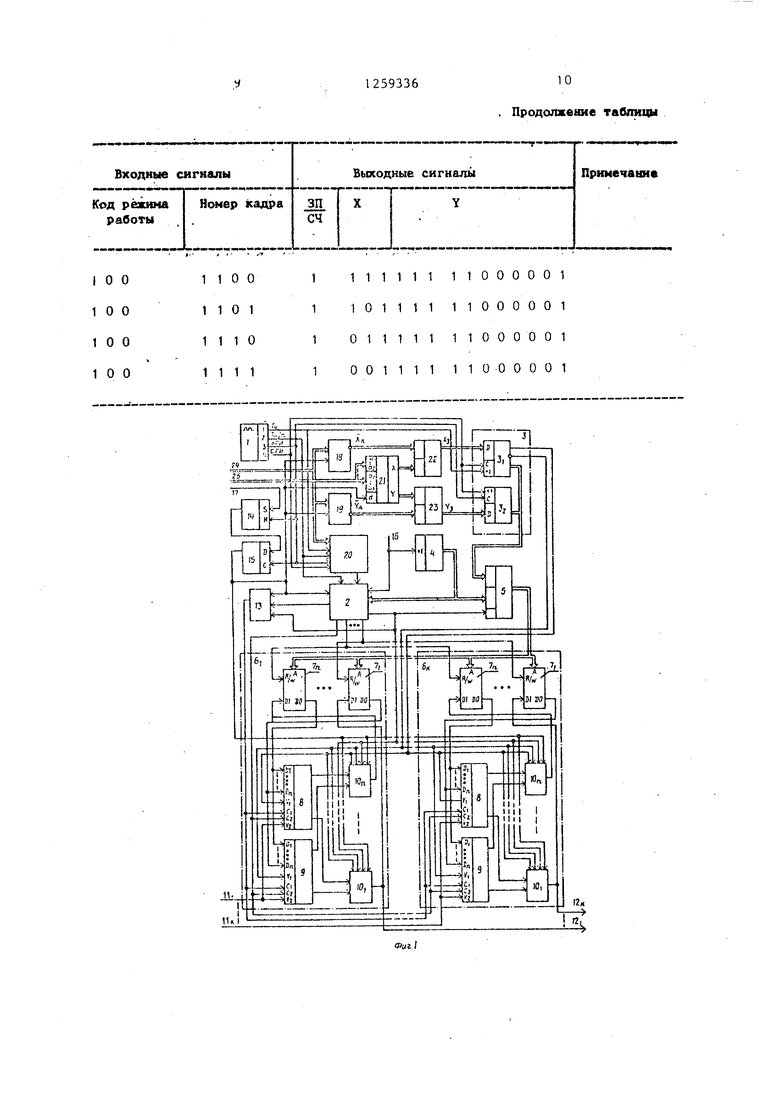

На фиг. 1 представлена схема запоминающего устройства; на фиг. 2-4 - схемы вариантов реализации блока управления, коммутаторов и формировате- ля строб-сигнала соответственно; на 4мг. 5 - примеры компоновки формируемых изображений.

Запоминающее устройство (фиг. 1) содержит генератор 1 тактовых им- пульсов, блок 2 управления, счетчик 3 адреса считьгоания, состоящий из счетчика 3 по строке и счетчика 3 по кадру, счетчик 4 адреса поэлементной записи, адресный блок 5, группы 6. ...6 (где к- число разрядов вход1 PN

ной информации) накопителей 7 ... 7 (где п- целое число), имеющие также первый 8, второй 9 регистры сдвига и h коммутаторов 10, ...10 в каждой группе, входные 11 ;..11 и выходные 12 ... 12 1 информационные шины, элемент И 13, первый 14 и второй 15 тригеры, первый 16 и второй 17 управляю ище входы, первьв 18 и второй 19 блоки элементов И-НЕ, формирователь 20 строб-сигнала, преобразователь 21 кода, первый 22 и второй 23 сумматоры, шины 24 координат строб-сигнала и шины 25 начальной установки режима записи.

Блок 2 управления (фиг. Z) содержит счетчик 26, формирователи 27-30 сигналов с первого по четвертьй и дешифратор-мультиплексор 31.

Каждый из коммутаторов 10....10 (фиг. 3) содержит элемент ИЛИ 32, входы которого являются третьим и четвертым управляющими входами коммутатора 10, элемент НЕ 33, подключен ный к выходу элемента ИЛИ 32, элементы И 34-37 и элемент ИЛИ 38.

Формирователь 20 строб-сигнала (фиг. 4) содержит четыре счетчика 39-42, три триггера 43-45 и элемент И 46.

Устройство работает следующим образом.

В режиме считывания обращение происходит ко всем накопителям «..7 каждой группы 6,..6 (поскольку все группы накопителей работают идентично) , далее везде рассматривается работа одной группы 6 . Адреса считывания, поступающие на адресные входы А накопителей 7 через адресный блок 5, задаются счетчиком 3, Смена кодов счетчика 3 производится синхронно с разверткой телевизионного индикатора (.не показан). Для этого генератор 1 формирует тактовые импульсы с периодом Тц, равным длительности цикла обращения, поступающие на счетный вход счетчика 3 , и импульсы строчной синхронизации в данном случае строчные гасящие импульсы (СГИ), поступающие на счетный вход счетчика 3. В данном режиме считьшания оба триггера 14 и 15 находятся в состоянии О, при этом закрываются все элементы И-НЕ блоков 18 и 19 и, независимо от информации на шинах 24, на всех их выходах устанавливается потенциал 1. Также при уровне О на входе 4 преобразовател 21, независимо от информации на шина 25, на его выходах х , у устанавливается код согласно таблице. При этом на информационных входах счетчи ков 3 и 32 устанавливаются коды Xj 111111 + 000001 000000 и V,, 11111111 00000001 00000000 соответственно. Во время СГИ и кадровых гасящих импульсов (КГИ) эти коды переписываются в счетчики 3 и 3, тем самым обеспечивается последовательное и синхронное с телевизионным растром, начиная с нулевого адреса, обращение к накопителям 7 ...7 . По примеру в таблице объем памяти накопителей группы рассчитан

О

на запоминание 2 256 элементов

о

изображения в течение 2 256 строк одного поля телевизионного растра. С выходов Dp накопителей 7 . 7 информация поступает на разрядные входы 1) .l- f, регистров 8 и 9., По сигналу из блока 2 управления,, поступающему в каждом цикле через элемент И 13 на входы синхронизации С1 регистров 8 и 9, эта информация (первые разряды h соседних .по строке элементов изображения) переписывается в один из регистров, в зависимости от сигнала на управляющих входах VI, допустим - в регистр 8. Во время этого же цикла обращения из другого регистра 9 с выхода п-го разряда через коммутатор 10 информация, записанная в этот регистр 9 в предыдущем цикле обращения, выталкивается на выходную пшну 12, . Продвижение этой информации по регистру 9 осуществляется импульсами, поступающими из блока 2 управления на вход С2 регистра 9 с периодом следования Тц/п, В течение следующего цикла обращения осуп аствляется вывод информации, записанной в регистре 8; и запись из накопителей 7 ...7, в регистр 9. И далее происходит поочередная работа обоих регистров 8 и 9 на запись информации из накопителей 7...7 и считывание ее путем сдвига в регистре и вывода через коммутатор 10 на шину 12,.

Импульсы, осуществляющие параллельную запись в регистры 8 и 9 выходной информации из накопителей и ее сдвиг, формируются блоком 2 следующим образом.

С помощью формирователей 27 и 28 (фиг. 2) по разрядным сигналам f , fj, fj счетчика 26 формируются сигналы f,, поступающие через элемент И 13 на первые входы синхронизации регистров 8 и 9, и сигналы fg, поступающие на вторые входы синхронизации регистров 8 и 9 i Временное расположение сигналов f, f, внутри каждого цикла обращения определяется поляр- костью и фазой управляющих сигналов, требуемых для применяемых в конкрет- ном ЗУ накопителей и регистров. Сами формирователи 27 и 28 выполняются на логических элементах и в дан ном примере реализ уют логические операции f fj, fg f 1 .

Режим поэлементной записи. В каждом случае после окончания вывода информации из регистра (8 или 9) на всех его выходах устанавливается потенциал, соответствующий значению кода на входной информационной щине 11р соединенной с информационными входами регистров. Это обстоятельст- во используется в режиме поэлементной записи информации от медленно сканирующих датчиков. По сигналу f, поступающему по входу 16 на блок 2 и счетный вход счетчика 4, в послед- нем устанавливается очередной адрес. Во время очередного цикла считьшания (первого после сигнала по входу 16)

в блоке 2 с помощью формирователя 30 (фиг. 2) формируется одиночный импульс f длительностью в один цикл. Этим импульсом переключается адресный блок 5 и на адресные входы А накопителей 7| е, выставляется адрес записываемой информации со счетчика 4. Также во время этого сигнала дешифратор-мультиплексор 31 (фиг. 2) формирует импульс f, длительность и фаза которого задается формирователем 29 (fg), поступающий на вход записи R/W одного из накопителей 7 . .. 7 . Выбор накопителя определяется кодом младших разрядов счетчика 4, поступающим на входы дешифратора- мультиплексора 31. В этот же цикл блокируется прохождение через элемент И 13 сигнала С1, вследствие чего запись информации в соответствуюпц1й регистр из накопителей не происходит. Поскольку на всех разрядных выходах этого регистра к моменту начала данного цикла записи установился пдтен- циал, соответствуюЕЦий входной информации на щине 11 , то эта информация и записьшается в соответствующий накопитель. Причем на время записи происходит подключение разрядных выходов данного регистра к выходам коммутаторов 10...10.

Режим записи телевизионного .изображения. В данном режиме информация на входных шинах 11, ... 11 меняется синхронно с телевизионной разверткой через время Тц/п и поступает с вькода аналого-цифрового преобразователя (не показан). По сигналу, поступающему на Вход 17, переключается триггер 14, который возвращается в исходное состояние КГИ, поступающих с третьего выхода генератора 1. От заднего фронта, сформированного триггером 14 импульса, переключается триггер 15, который возвращается в исходное состояние следующими КГИ. Таким )бразом триггер 15 формирует импульс длительностью в один кадр.Этот импульс запира ет элемент И 13 и переводит коммутаторы 10,...10 в режим записи, когда к их выходам подключаются поочередно разрядные выходы регистра 8, если регистр 9 в данном цикле находится в режиме сдвига, или - регистра 9, если в режиме сдвига находится регистр 8. При этом входная видеоинформация с шин 11,.,.11 через регистры 8 и 9 и коммутаторы 10, ...10.,

поступает в виде и отсчетов на информационные входы накопителей 7 ... 7 и меняется на этих входах каждые Тц. Адресация накопителей 7 ... ...7, задается счетчиком 3.

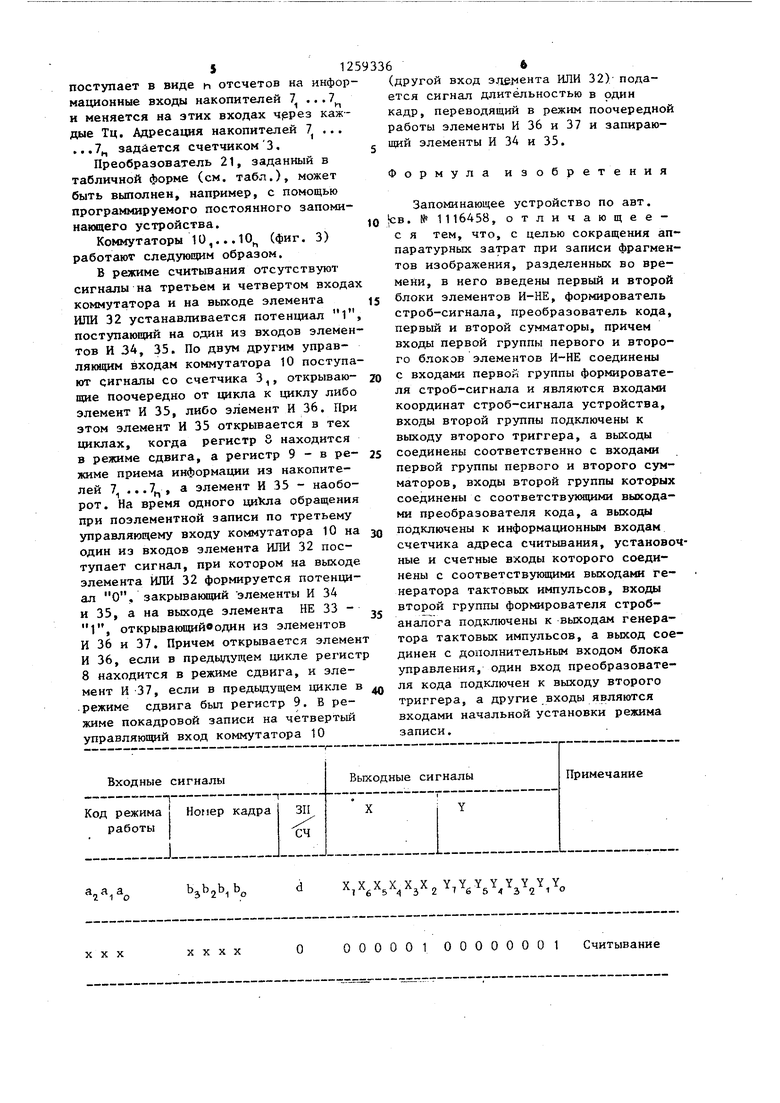

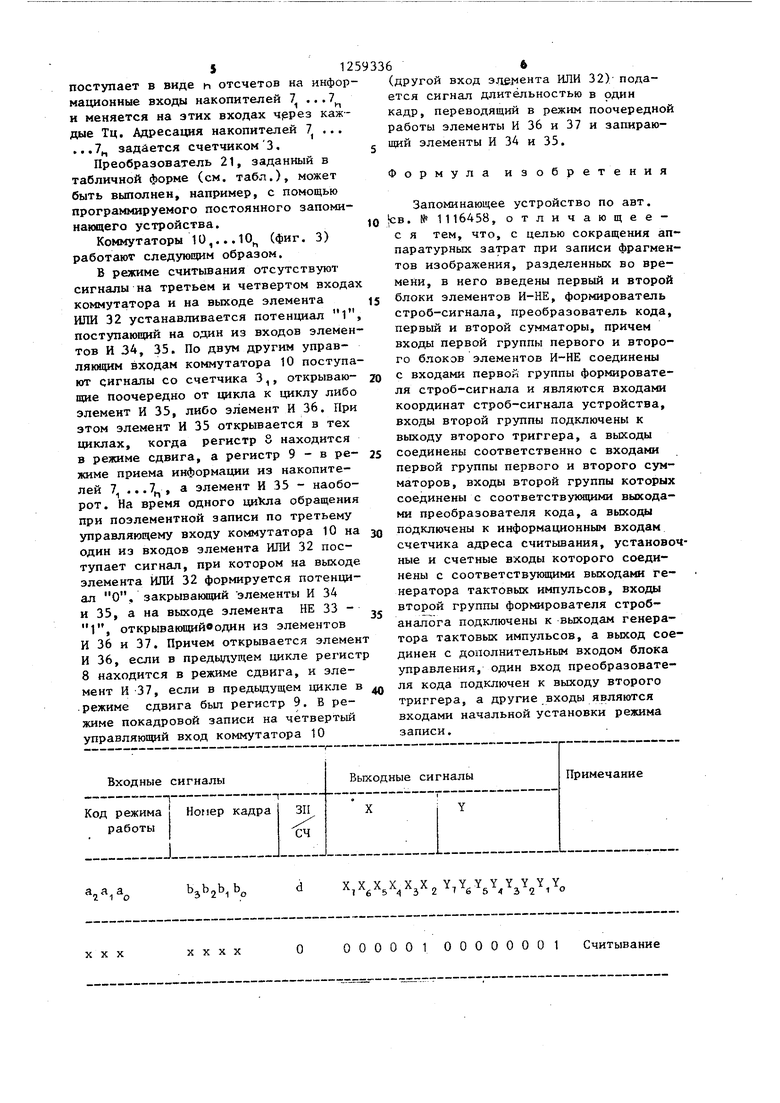

Преобразователь 21, заданный в табличной форме (см. табл.), может быть выполнен, например, с помощью программируемого постоянного запоминающего устройства.

Коммутаторы 10,..,10 (фиг. 3) работают следукнцим образом.

В режиме считывания отсутствуют сигналы на третьем и четвертом входах коммутатора и на выходе элемента ИЛИ 32 устанавливается потенциал 1 поступающий на один из входов элементов И 34, 35. По двум другим управляющим входам коммутатора 10 поступают сигналы со счетчика 3 , открываю- щие поочередно от цикла к циклу либо элемент И 35, либо элемент И 36. При этом элемент И 35 открывается в тех циклах, когда регистр 8 находится в режиме сдвига, а регистр 9 - в ре- жиме приема информации из накопителей 7 ...7, а элемент И 35 - наоборот. На время одного циКла обращения при поэлементной записи по третьему управляющему входу коммутатора 10 на один из входов элемента ИЛИ 32 поступает сигнал, при котором на выходе элемента ИЛИ 32 формируется потенциал О, закрывакяций элементы И 34 и 35, а на выходе элемента НЕ 33 - 1, открывающий один из элементов И 36 и 37. Причем открывается элемен И 36, если в предыдущем цикле регист 8 находится в режиме сдвига, и элемент И 37, если в предыдущем цикле в .режиме сдвига был регистр 9. В режиме покадровой записи на четвертьш управляющий вход коммутатора 10

Но

dX,,Y,,

XXX

X X X X

000001 00000001 Считывание

(другой вход 3jrieJ-ieHTa ИЛИ 32) подается сигнал длительностью в один кадр, переводящий в режим поочередной работы элементы И 36 и 37 и запирающий элементы И ЗА и 35.

Формула изобретения

Запоминающее устройство по авт. св. № 1116458, отличающее- с я тем, что, с целью сокращения аппаратурных затрат при записи фрагментов изображения, разделенных во времени, в него введены первый и второй блоки элементов И-НЕ, формирователь строб-сигнала, преобразователь кода, первый и второй сумматоры, причем входы первой группы первого и второго блоков элементов И-НЕ соединены с входами первой группы формирователя строб-сигнала и являются входами координат строб-сигнала устройства, входы второй группы подключены к выходу второго триггера, а выходы соединены соответственно с входами первой группы первого и второго сумматоров, входы второй группы которых соединены с соответствукяцими выходами преобразователя кода, а выходы подключены к информационным входам счетчика адреса считывания, установоные и счетные входы которого соединены с соответствующими выходами генератора тактовых импульсов, входы второй группы формирователя строб- аналога подключены к выходам генератора тактовых импульсов, а выход соединен с дополнительным входом блока управления, один вход преобразователя кода подключен к выходу второго триггера, а другие входы являются входами начальной установки режима записи.

. Продолжение таблицы

xiS н20 7

f

JTJlJTJlJUlJLrLrLr

K7цф.- Гц

л

JTJTJTJrLrLn rLrLr

JL

Фиг. 2

Фаг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

Изобретение относится к области вычислительной техники и позволяет формировать на экране телевизионного (ТВ) индикатора комбинированное изображение (И), составленное из нескольких кадров выбранного фрагмента И. Фрагмент выбирается с помощью электронной диафрагмы прямоугольной формы, по крайней мере один из размеров которой не более половины линейного размера ТВ растра. Комбинированное И составляется из фрагментов, за ксированных в различные моменты времени - кадры. Это обеспечивается за счет соответств укицего перераспределения памяти запоминающего устройства, которое достигается путем предустановки счетчика адресации при записи ТВ сигнала. Изоб етение позволяет сократить объем аппаратуры, требуемой для анализа И подвижных объектов по методу межкадровой разности, а также упростить визуальный анализ. 5 ил,, 1 табл. кл с to сд ф 00 со О) 14)

Редактор А.Ворович

Составитель О.Исаев

Техред М.Ходанич Корректор И.Муска

Заказ 5128/50 Тираж 543 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-23—Публикация

1985-03-12—Подача