Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при построении накопителей оперативных запоминающих устройств (ОЗУ) с большой частотой выборки и записи информации, например дисплейных ОЗУ, работающих в режиме формирования изображения на экране растрового (телевизионного) монитора и обеспечивающих повышенное быстродействие при записи информации, синтезированной ЭВМ или графическим процессором.

Цель изобретения - повышение быстродействия устройства и расширение области его применения за счет обеспечения доступа к произвольному числу одноразрядных блоков памяти в одном цикле обращения и многократной выборки произвольных групп одноразОд

to

lsЈ

рядных блоков памяти внутри этого цикла.

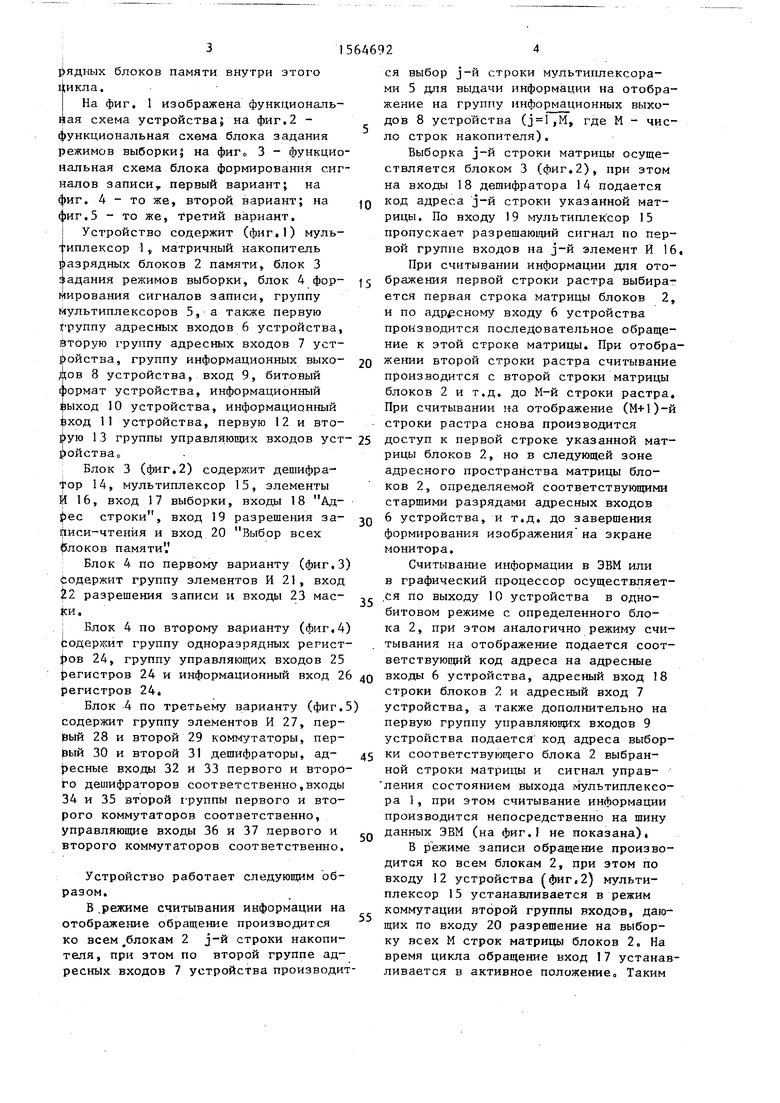

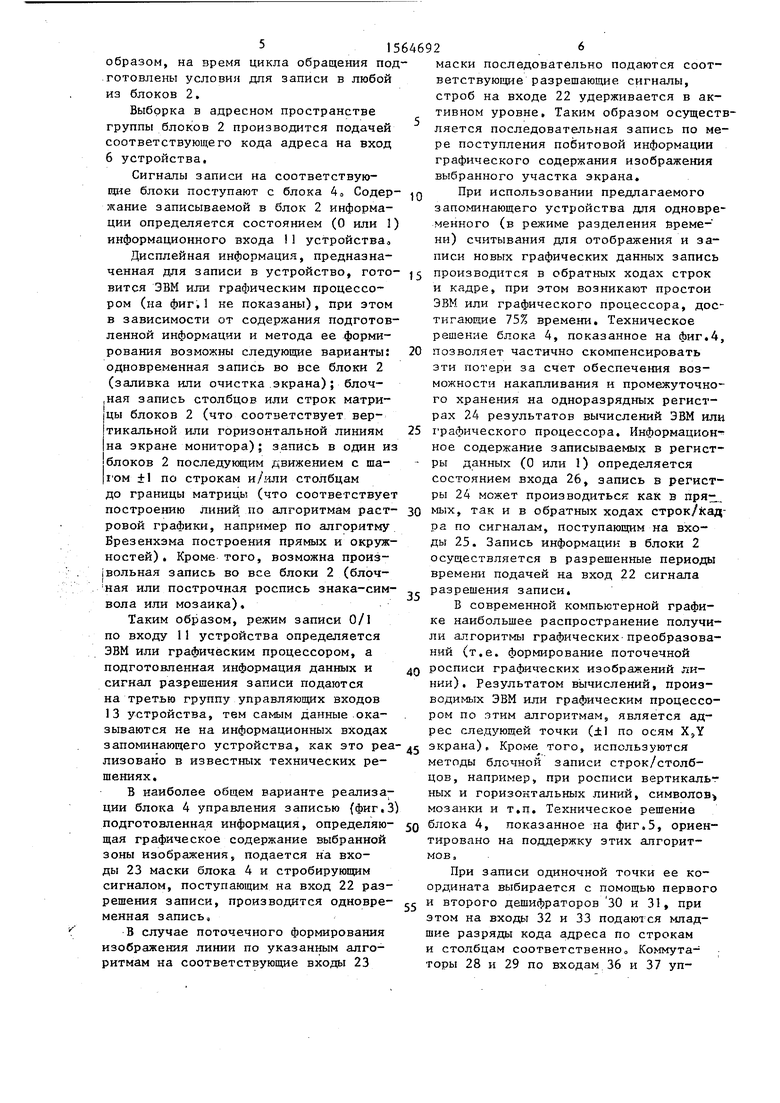

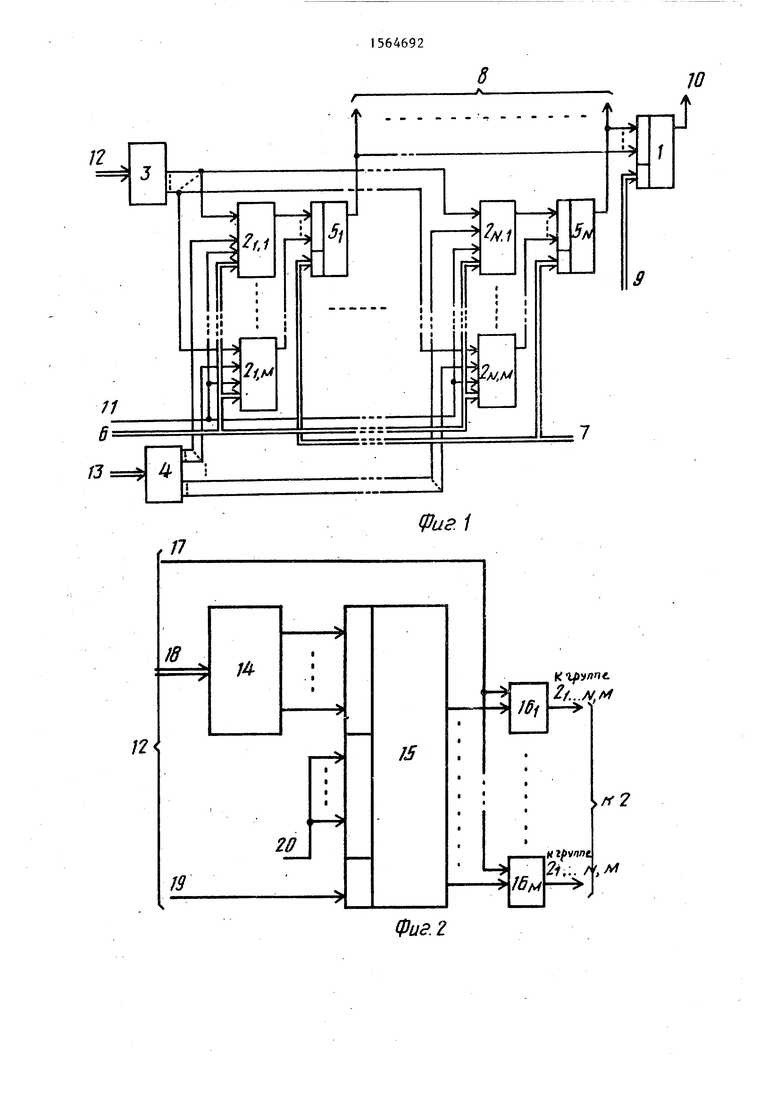

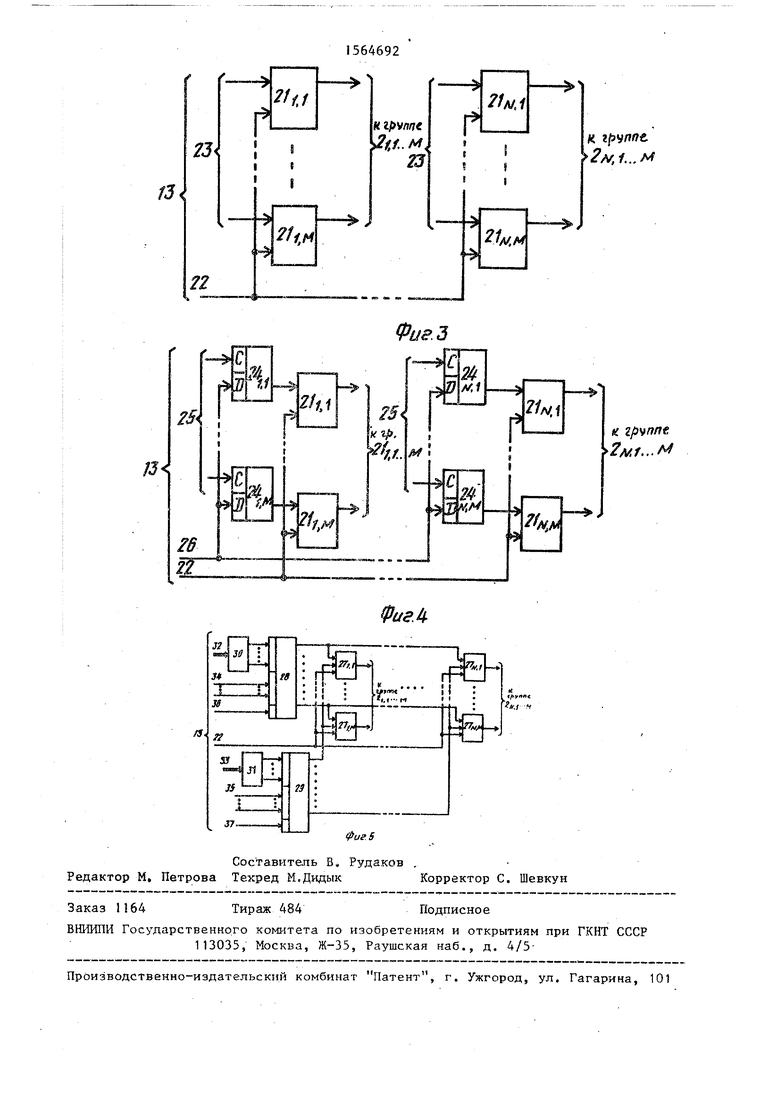

На фиг. 1 изображена функциональная схема устройства} на фиг,2 - функциональная схема блока задания режимов выборки| на фиг 3 - функциональная схема блока формирования сигналов записи, первый вариант; на фиг. 4 - то же, второй вариант; на фиг.5 - то же, третий вариант.

Устройство содержит (фиг«1) муль- иплексор 1, матричный накопитель азрядных блоков 2 памяти, блок 3 здания режимов выборки, блок 4 формирования сигналов записи, группу мультиплексоров 5, а также первую Группу адресных входов 6 устройства, йторую группу адресных входов 7 устройства, группу информационных выхо- ов 8 устройства, вход 9, битовый юрмат устройства, информационный 1ыход 10 устройства, информационный Јход 11 устройства, первую 12 и вторую 13 группы управляющих входов уст- Ьойствао

Блок 3 (фиг.2) содержит дешифра- top 14, мультиплексор 15, элементы И 16, вход 17 выборки, входы 18 Ад- Јec строки, вход 19 разрешения записи-чтения и вход 20 Выбор всех блоков памяти1.1

Блок 4 по первому варианту (фиг.З содержит группу элементов И 21, вход 22 разрешения записи и входы 23 мас Ји.

Блок 4 по второму варианту (фиг,4 Додержит группу одноразрядных регистров 24, группу управляющих входов 25 регистров 24 и информационный вход 2 регистров 24,

Блок 4 по третьему варианту (фиг, содержит группу элементов И 27, первый 28 и второй 29 коммутаторы, первый 30 и второй 31 дешифраторы, адресные входы 32 и 33 первого и второго дешифраторов соответственно,входы 34 и 35 второй группы первого и второго коммутаторов соответственно, управляющие входы 36 и 37 первого и второго коммутаторов соответственно.

Устройство работает следующим образом.

В режиме считывания информации на отображение обращение производится ко всем .блокам 2 j-й строки накопителя, при этом по второй группе адресных входов 7 устройства производи

0

s

0

5

дд

0

35

45

50

ся выбор j-й (.троки мультиплексорами 5 для выдачи информации на отображение на группу информационных выходов 8 устройства (,M, где М - число строк накопителя).

Выборка j-й строки матрицы осуществляется блоком 3 (фиг.2), при этом на входы 18 дешифратора 14 подается код адреса j-й строки указанной матрицы. По входу 19 мультиплексор 15 пропускает разрешающий сигнал по первой группе входов на j-й элемент И 16,

При считывании информации для отображения первой строки растра выбирается первая строка матрицы блоков 2, и по адресному входу 6 устройства производится последовательное обращение к этой строке матрицы. При отображении второй строки растра считывание производится с второй строки матрицы блоков 2 и т.д. до М-й строки растра. При считывании на отображение (М+1)-й строки растра снова производится доступ к первой строке указанной матрицы блоков 2, но в следующей зоне адресного пространства матрицы блоков 2, определяемой соответствующими старшими разрядами адресных входов 6 устройства, и т.д. до завершения формирования изображения на экране монитора.

Считывание информации в ЭВМ или в графический процессор осуществляется по выходу 10 устройства в однобитовом режиме с определенного блока 2, при этом аналогично режиму считывания на отображение подается соответствующий код адреса на адресные входы 6 устройства, адресный вход 18 строки блоков 2 и адресный вход 7 устройства, а также дополнительно на первую группу управляющих входов 9 устройства подается код адреса выборки соответствующего блока 2 выбранной строки матрицы и сигнал управ- ления состоянием выхода мультиплексора 1, при этом считывание информации производится непосредственно на шину данных ЭВМ (на фиг.1 не показана),

В режиме записи обращение производится ко всем блокам 2, при этом по входу 2 устройства (фиг,2} мультиплексор 15 устанавливается в режим коммутации второй группы входов, дающих по входу 20 разрешение на выборку всех М строк матрицы блоков 2. На время цикла обращение вход 17 устанавливается в активное положение„ Таким

образом, на время цикла обращения подготовлены условия для записи в любой из блоков 2.

Выборка в адресном пространстве группы блоков 2 производится подачей соответствующего кода адреса на вход 6 устройства.

Сигналы записи на соответствующие блоки поступают с блока 4а Содер- жание записываемой в блок 2 информации определяется состоянием (0 или 1) информационного входа 1 1 устройства

Дисплейная информация, предназнамаски последовательно подаются соответствующие разрешающие сигналы, строб на входе 22 удерживается в активном уровне. Таким образом осуществляется последовательная запись по мере поступления побитовой информации графического содержания изображения выбранного участка экрана.

При использовании предлагаемого запоминающего устройства для одновременного (в режиме разделения времени) считывания для отображения и записи новых графических данных запись

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1987 |

|

SU1483492A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Запоминающее устройство | 1987 |

|

SU1460740A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

Изобретение относится к вычислительной технике, в частности к дисплейным оперативным запоминающим устройствам, и может быть использовано при построении накопителей ОЗУ с большой частотой выборки и записи информации, работающих в режиме формирования изображения на экране растрового (телевизионного) монитора в составе высокопроизводительных графических терминалов. Целью изобретения является повышение быстродействия устройства и расширение области его применения за счет обеспечения доступа к произвольному числу одноразрядных блоков памяти в одном цикле обращения и многократной выборки произвольных групп одноразрядных блоков памяти внутри этого цикла. Запоминающее устройство содержит мультиплексор, матричный накопитель из блоков памяти, блок задания режимов выборки, блок формирования сигналов записи, группу мультиплексоров. Устройство позволяет производить запись в произвольное число блоков памяти матрицы из этих блоков как параллельно, так и последовательно, за один такт обращения к данной матрице, что сокращает длительность минимального цикла записи и среднее время записи и повышает производительность при заливке/очистке экрана, построении горизонтальных и вертикальных линий, мозаике, строчной росписи символов, а также поддерживает быстрые алгоритмы формирования графических изображений. Кроме того, обеспечение доступа к одному блоку памяти при чтении упрощает взаимодействие ЗУ с ЭВМ. 5 ил.

20

ченная для записи в устройство, гото- j$ производится в обратных ходах строк вится ЭВМ или графическим процессором (на фиг.1 не показаны), при этом в зависимости от содержания подготовленной информации и метода ее формирования возможны следующие варианты: одновременная запись во все блоки 2 (заливка или очистка экрана); блочная запись столбцов или строк матрицы блоков 2 (что соответствует вертикальной или горизонтальной линиям на экране монитора); запись в один из блоков 2 последующим движением с шагом ±1 по строкам и/или столбцам до границы матрицы (что соответствует построению линий по алгоритмам растровой графики, например по алгоритму Брезенхэма построения прямых и окружностей) . Кроме того, возможна произвольная запись во все блоки 2 (блочная или построчная роспись знака-символа или мозаика).

Таким образом, режим записи 0/1 по входу 11 устройства определяется ЭВМ или графическим процессором, а подготовленная информация данных и сигнал разрешения записи подаются на третью группу управляющих входов 13 устройства, тем самым данные оказываются не на информационных входах

и кадре, при этом возникают простои ЭВМ или графического процессора, дос тигающие 75% времени. Техническое решение блока 4, показанное на фиг.4 позволяет частично скомпенсировать эти потери за счет обеспечения возможности накапливания и промежуточно го хранения на одноразрядных регистрах 24 результатов вычислений ЭВМ ил 25 графического процессора. Информацион ное содержание записываемых в регист - ры данных (0 или 1) определяется состоянием входа 26, запись в регист ры 24 может производиться как в прямых, так и в обратных ходах строк/кад ра по сигналам, поступающим на входы 25. Запись информации в блоки 2 осуществляется в разрешенные периоды времени подачей на вход 22 сигнала разрешения записи.

В современной компьютерной графике наибольшее распространение получили алгоритмы графических преобразований (т.е. формирование поточечной росписи графических изображений линии). Результатом вычислений, производимых ЭВМ или графическим процессором по этим алгоритмам, является адрес следующей точки (±1 по осям ХД

30

35

40

запоминающего устройства, как это pea-45 экрана). Кроме того, используются лизовано в известных технических ре- методы блочной записи строк/столбшениях.

В наиболее общем варианте реализации блока 4 управления записью (фиг.З подготовленная информация, определяю- щая графическое содержание выбранной зоны изображения, подается на входы 23 маски блока 4 и стробирующим сигналом, поступающим на вход 22 разрешения записи, производится одновременная запись,

В случае поточечного формирования изображения линии по указанным алгоритмам на соответствующие входы 23

производится в обратных ходах строк

и кадре, при этом возникают простои ЭВМ или графического процессора, достигающие 75% времени. Техническое решение блока 4, показанное на фиг.4, позволяет частично скомпенсировать эти потери за счет обеспечения возможности накапливания и промежуточного хранения на одноразрядных регистрах 24 результатов вычислений ЭВМ или графического процессора. Информационное содержание записываемых в регист- ры данных (0 или 1) определяется состоянием входа 26, запись в регистры 24 может производиться как в пря. мых, так и в обратных ходах строк/кадра по сигналам, поступающим на входы 25. Запись информации в блоки 2 осуществляется в разрешенные периоды времени подачей на вход 22 сигнала разрешения записи.

В современной компьютерной графике наибольшее распространение получили алгоритмы графических преобразований (т.е. формирование поточечной росписи графических изображений линии). Результатом вычислений, производимых ЭВМ или графическим процессором по этим алгоритмам, является адрес следующей точки (±1 по осям ХД

0

5

цов, например, при росписи вертикальных и горизонтальных линий, символов мозаики и т.п. Техническое решение блока 4, показанное на фиг.5, ориентировано на поддержку этих алгоритмов,

При записи одиночной точки ее координата выбирается с помощью первого и второго дешифраторов 30 и 31, при этом на входы 32 и 33 подаются младшие разряды кода адреса по строкам и столбцам соответственно. Коммутаторы 28 и 29 по входам 36 и 37 управления устанавливаются в соответствующий режим, сигналами на выходах оммутаторов 28 и 29 осуществляется | выборка соответствующего элемента И 27, при этом подаваемый на вход 22 блока 4 сигнал строба записи поступает на вход записи соответствующего блока 2.

Блочная запись точек строб/столб- цов производится подачей соответствующего кода на вход 32/33 первого/ |второго дешифратора 30/31 блока 4 с одновременной подачей кода блочной записи на вход 36/35 коммутатора 29/28. При этом осуществляется выборка требуемой строки/столбца матрицы элементов И 27. Запись производится подачей соответствующего сигнала записи на вход 22 разрешения записи. Режим работы коммутаторов 28 и 29 задается по управляющим входам 36 и 37 блока 4.

В случае использования блока 4, выполненного по схеме фиг.5, с ЭВМ |или с графическим процессором, не обладающими возможностью формирования блочных массивов графических данных (т.е. строчной росписью символов, мозаики, целесообразно входы 34 и 35 вторых каналов коммутаторов 28 и 29 подключить к логическому уровню, обеспечивающему прохождение на выход Коммутаторов 28 и 29 разрешающего сигнала. При этом сохраняются функции поточечной записи, блочной записи ли- |ний строк и столбцов и блочной залив- ки/очистки экрана. |

I Таким образом, предпагаемое уст- ройство, обеспечивая одновременный доступ к матрице блоков памяти, позволяет сократить время записи в ОЗУ битового содержания графического изображения за счет того, что запись то- чек в пределах выбранной матрицы осуществляется без потери времени на выбор соответствующего блока памяти по каналам адреса и выборки кристалла.

Возможность одновременной записи в произвольное число блоков памяти из выбранной матрицы блоков памяти обеспечивает повышение производительности при таких режимах графических

преобразований, как заливка/очистка,

построение горизонтальных и вертикаль- I

5 0

5 0 -

Q 5

0

5

ных линий, мозаика, строчная роспись

символов.

Формула изобретения

Оперативное запоминающее устройство для растрового дисплейного терминала, содержащее мультиплексор и матричный накопитель, состоящий из одноразрядных блоков памяти, адресные входы которых соединены поразрядно и являются первой группой адресных входов устройства, отличающееся тем, что, с целью повышения быстродействия устройства и расширения области его применения за счет обеспечения доступа к произвольному числу одноразрядных блоков памяти в одном цикле обращения и многократной выборки произвольных групп одноразрядных блоков памяти внутри этого цикла, в него введены блок задания режимов выборки, блок формирования сигналов записи и группа мультиплексоров, управляющие входы которых соединены поразрядно и являются второй группой адресных входов устройства, информационные входы каждого мультиплексора группы соединены с выходами одноразрядных блоков памяти соответствующего столбца матричного накопителя, выходы мультиплексоров группы соединены с соответствующими информационными входами мультиплексора и являются группой информационных выходов устройства, входы Выборка кристалла одноразрядных блоков памяти каждой строки матричного накопителя, объединены и подключены к соответствующему выходу блока задания режимов выборки,информационные входы одноразрядных блоков памяти объединены и являются информационным входом устройства, входы записи-чтения одноразрядных блоков памяти подключены к соответствующим выходам блока формирования сигналов записи, входы маски и разрешения записи которого являются одноименными входами устройства, входы Адрес строки, вход выборки, вход разрешения записи-чтения, вход Выбор всех блоков памяти блока задания режимов выборки являются одноименными входами устройства, выход мультиплексора является информационным выходом устройства, управляющий вход мультиплексора является входом Битовый формат устройства.

%

и

(h. Я

/ ъпф

г

01

9

0

Ъ

pi

№

134

ZWf

Составитель В. Рудаков . Редактор М, Петрова Техред М.Дидык Корректор С. Шевкун

Заказ 1164

Тираж 484

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

к г/эуляе 2щ...м

ФигЗ

,

r1

«г группе

Zvf/.-A/

гг4

Подписное

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство | 1980 |

|

SU928408A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-05-15—Публикация

1988-05-11—Подача