1

Изобретение отиоеится к радиотехнике и может использоваться в системах радиосвязи и измерительной технике.

Известен цифровой частотно-фазовый детектор, содержащий два основных триггера, иервые выходы которых подключены ко входам узла сброса, выход которого соединен с иервыми входами основных триггеров 1.

Однако известный цифровой частотно-фазовый детектор имеет низкий уровень выходного сигнала.

Цель изобретения - увеличение уровня выходного сигнала.

Для этого в цифровой частотно-фазовый детектор, содержащий два основных триггера, иервые выходы которых подключены ко входам узла сброса, выход которого соединен с первыми входами основных триггеров, введены два ключа, донолнительный триггер и два блока онознавания носледовательности имнульсов, первые входы которых соедипеиы со вторыми входами основных триггеров, а выходы дополнительного триггера подключеиы к управляющим входам ключей, информационные входы которых соединены со вторыми выходами основных триггеров и вторыми входами блоков опознавания последовательности импульсов, выходы которых подключеиы ко входам донолиительпого триггера.

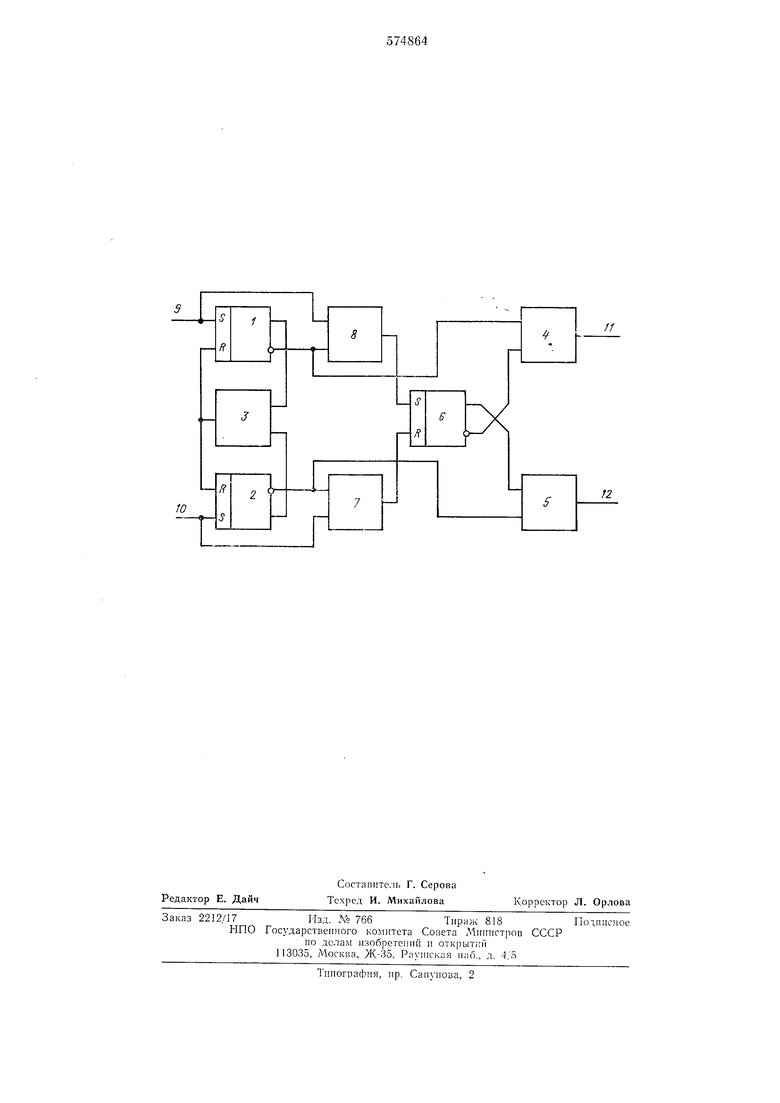

На чертеже изображеиа CTpyi-стуриая электрическая схема иредлагаемого цифрового частотно-фазового детектора.

Цифровой частотно-фазовый детектор содержит два основных трнггсра 1 н 2, нервые выходы которых иодключеиы ко входам узла 3 сброса, выход которого соединен с иервыми входами основных триггеров 1 н 2, два ключа 4 и 5, дополнительный триггер 6 и два блока 1 и 8 опознания последовательности импульсов, первые входы которых соедппены со вторыми входами основиых триггеров 1, 2, а выходы доиолинтельного триггера 6 подключены к управляющим входам ключей 4 и 5,

ииформациоиные входы которых соединены со вторыми выходами осиовиых триггеров и вторыми входами блоков 1 и 8, выходы которых подключены ко входам дополнительпого триггера 6.

Детектор работает следуюи нм образом.

Приходян1,ие на входы 9 п 10 короткне имиульеы вызывают оирокидываиие триггеров 1 и 2, причем в зависимости от знака частотиой расстройки на выходе одиого из триггеров 1

или 2 формируются короткие импульсы, а на выходе другого - импульсы с длительностью, пропорциональной разности фаз. Через ключи 4, 5, поочередно открываемые дополнительным триггером 6, выходные сигналы ocuoBiibix

триггеров поступают иа выходы 11 и 12.

Когда частота повторения импульсов на входе 9 превышает частоту повторения импульсов на входе 10, на пнверсном выходе дополиптельиого триггера 6 устанавливается высокий потенциал, а на прямом выходе -- соответственно низкий нотепцнал. В результате ключ 4 открыт, а ключ 5 закрыт.

Первый импульс, поступающий на вход 9, вызывает онрокндывание основного триггера 1, и на его первом выходе появляется высокий иотенннал. Па входе узла сброса 3, соединеииом с первым выходом основного триггера 2, также возникает высокий потенпиал, поэтому перепад напряжения е основного триггера 1 проходнт через узел сброса 3, воздействуя па входы сброса основных триггеров 1 и 2. Основной триггер 1 возвращается в исходное еостоянне, формируя на евоем втором выходе короткий имиулье, а на втором выходе оеновного триггера 2 устанавливается высокий потенциал. Проходящий иа вход 10 нмнульс оирокидывает основной триггер 2 в исходное состояние, однако, состояние основного трнггера 1 не изменяется, поскольку ирохождение иерепада напряжеиия с основного триггера 2 через узел сброса 3 занрендено низким иотенииалом на первом выходе основного триггера 1. Таким образом, в течение одного нернода импульсов на входе 9 на выходе основного триггера 1 формируются короткие импульсы, а иа выходе основного триггера 2 образуются импзльсы с длительностью, иропорииональной текущей разности фаз входиых сигналов. Через ключ 4 выходной еигиал основного триггера 1 проходнт на выход И, создавая среднее значение напряжения за период входных импульсов, равное максимальному выходному напряжению.

Описанные процессы повтрояются с прпходом каждого входного имнульса до тех пор, пока между двумя импульсами иа входе 10 ие оказываются два имнульса со входа 9. В этом случае импулье па входе 9, приходяи1.нй вслед за импульсом на этом же 15ходе, устанавливает на нивереном выходе основного триггера 1 низкий иотеиииал, сохраияя состояние основного триггера 2 нензмеиным. Очередной импульс на входе 10 онрокндывает основной трнггер 2, и перепад напряжения, ироходя через узел сброса 3, формирует на его втором выходе короткий импульс. Основной триггер 1 устанавливается в состояние, соответствуюи,ее высокому нотенниалу на своем втором выходе. Теперь импульсы с длительностью, пропорциональиой разности фаз, образуются на выходе основного триггера, 2, а оеновиой триггер 1 выдает короткие нмнульсы. Эта последовательность работы основных трнггеров сохраняется, пока ие изменится зиак частотной расстройкн.

Однако нрн следу1он1ем ноявлеиии двух имнульсов на входе 9 в интервале между двумя имиульсамн на входе 10 срабатывает блок 7 оиознавання иоследователглюсти импульсов,

который выдает короткий импульс при совнадеиин имнульса иа входе 9 с отрицательным имиульсом на втором выходе основного триггера 1. Импульс блока 7 опознавания последовательности имнульсов оирокндывает донолинтельный трнггер 6, и ключ 4 закрывается. Одновременно высокий иотенпиал на ирямом выходе доиолиптельного триггера 6 открывает ключ 5. На выход 12 нри этом проходнт сигнал с выхода основного триггера 2, а

на выходе 11 напряжение становится равным нулю. В результате на выходах 11 и 12 иоявляются сигналы, обратные сигналам при отрицательной расстройке. Этн сигналы сохраняются до тех нор, пока знак частотной расстройки ие смеияется иа иротивоположный.

Предложенный цифровой частотно-фазовый детектор по сравнению с нзвестиым имеет больший уровень выходного сигнала.

30

Формула изобретения

Цифровой частотно-фазовый детектор, содержащий два основиых триггера, нервые выходы которых подключены ко входам узла

сброса, выход которого соединен с первымн входами основных триггеров, отличающийся тем, что, с целью увеличения уровня выходного сигнала, введены два ключа, дополнительный триггер и два блока оиозиавания последовательпости импульсов, первые входы которых соединены со вторымп входами основных трнггеров, а выходы доиолинтельиого триггера подключены к уиравляюHUIM входам ключей, н 1формацнон11ые входы

которых соедннены со вторымн выходами основных трнггеров н вторыми входами блоков опозпавапня последовательности имиульсов, выходы которых подключены ко входам допол пительиого триггера.

Источники ннформацнн, прпиятые во внимаиие ири экснертизе

1. Патент США N° 3469198, кл. 329-50, 1969.

//

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1976 |

|

SU621060A1 |

| Устройство для измерения скорости телеграфирования | 1974 |

|

SU547042A1 |

| Цифровой частотно-фазовый детектор | 1977 |

|

SU681574A2 |

| Устройство импульсно-фазовой автоподстройки частоты | 1973 |

|

SU484617A1 |

| Устройство для измерения частоты гетеродина | 1978 |

|

SU744355A1 |

| Корректор межсимвольных искажений | 1975 |

|

SU574856A1 |

| Частотно-фазовый детектор | 1984 |

|

SU1298844A1 |

| Автоматический сигнализатор дефектов | 1975 |

|

SU744319A1 |

| Устройство для оценки частотных искажений | 1974 |

|

SU595870A1 |

| Устройство для измерения частоты перестраиваемого генератора | 1978 |

|

SU744357A1 |

Авторы

Даты

1977-09-30—Публикация

1976-02-16—Подача