1

Изобретение относится к радиоприемным устройствам.

Известно устройство импульсно-фазовой автоподстройки частоты, содержащее последовательно соединенные в кольцо подстраиваемый генератор, первый ключ, фазовый детектор, соединенный через второй ключ с эталонным генератором, и блок памяти, а также две схемы «И и частотный детектор, подключенные к выходам подстраиваемого и эталонного генераторов, причем другие входы схемы «И подсоединепы к соответствующим выходам триггера памяти, подключенного к выходам частотного детектора, а управляющий вход каждого из указанных ключей соединен с выходом соответствующей схемы «И через триггер управления.

Однако известное устройство имеет недостаточное быстродействие.

С целью увеличения быстродействия предлагаемого устройства вторые входы триггеров управления соединены с соответствующими выходами частотного детектора через дополнительные схемы «И, при этом дополнительная схема «И, подключенная к триггеру управления первым ключом, соединена непосредственно и через расширитель импульсов с выходом триггера управления вторым ключом, а дополнительная схема «И, нодключенная к триггеру управления вторым ключом.

соединена непосредственно и через другой расширитель и.мпульсов с выходом триггера управления первым ключом.

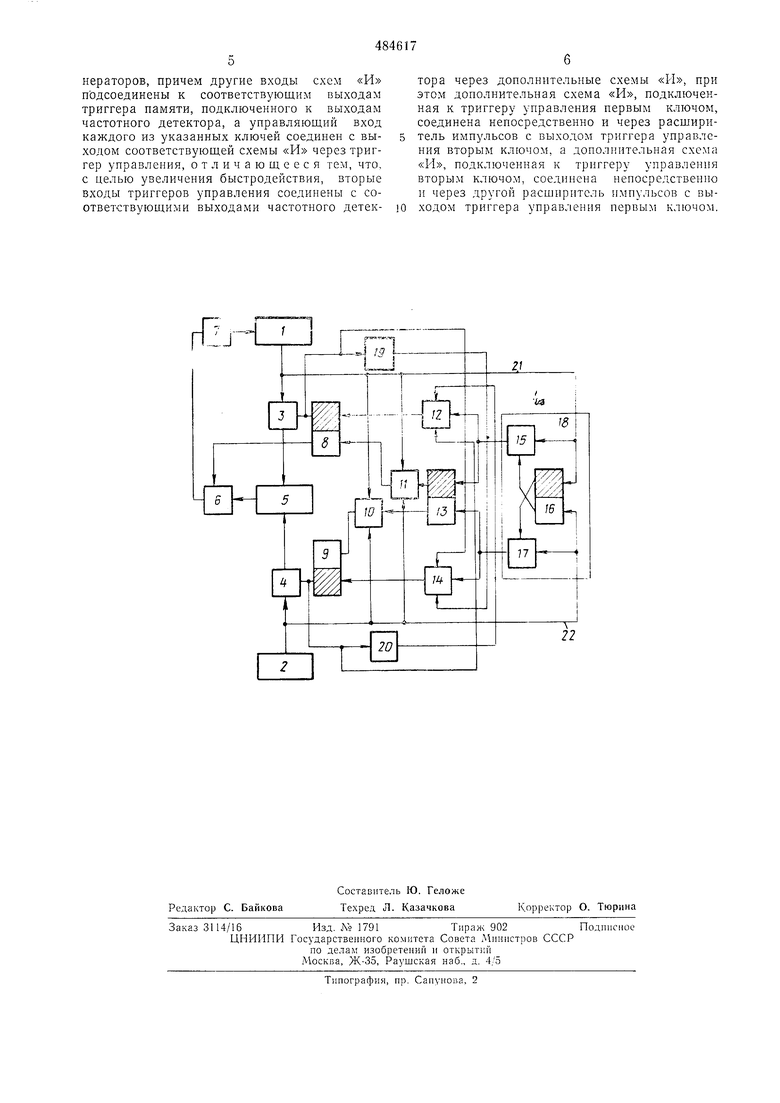

На чертеже дана функциональная схема

предлагаемого устройства.

Устройство содержит подстраиваемый генератор 1, эталонный генератор 2, первый ключ 3, второй ключ 4, фазовый детектор 5, блок 6 памяти, фильтр нижних частот 7, триггеры 8

и 9 управления, схемы «И 10-12, триггер 13 памяти, схемы «И 14 и 15, триггер 16, схема «И 17, частотный детектор 18, расширители импульсов 19 и 20, цепи 21 и 22 сигналов подстраиваемого и эталонного генераторов.

Сигналы подстраиваемого и эталонного генераторов 1 и 2 соответственно подаются через первый и второй ключи 3 и 4 на фазовый детектор 5 и непосредственно на схемы «И

10 и 11, а также на частотный детектор 18. С выхода фазового детектора 5 сигнал через блок 6 памяти и фильтр нижних частот 7 подается на управляющий вход подстраиваемого генератора 1. Частотный детектор 18 состоит из триггера 16, запускаемого по установочным входам сигналами генераторов I и 2, и двух схем «И 15 и 17, одни из входов которых подключены параллельно с установочными входами триггера 16, а другие к соответствующим выходам этого же триггера.

Выходы схем «И 15 и 17 являются одновременно выходами частотного детектора 18 и подключены к установочным входам трнггс)а 13 памяти. Выходы последнего нодключены к третьим входам схем «И 10 и 11, 1я 1ходы которых подключены к установочным входа.м триггеров 9 и 8 управления соответстг еино. Выходы триггеров 8 и 9 унравлення нодключены к управляющим входам первого н второго к. 3 и 4, ко Bxo;iaM расн111р1ггеле1 1 импульсов 19 и 20 и схем «И 14 и 12 соответственно. Выходы расгннрителей нмнульсов 19 и 20 подключены к другим входам схем «И 14 и 12 соответственно. Выходы схем «И 15 и 17 частотного детектора 18 через схемы «И 12 и 14 связаиы со вторыми входами триггеров 8 и 9 управления соответствс1п-о. Второй выход триггера 8 управлсглтя соединен с управляющим входом б.тока G памяти. По этой цепи поступает сигнал па гпунтнрование элемента иамяти, например, накопител)иого конденсатора, входящего в состав блока 6 памяти.

Устройство работает следуюп 1,им образом.

Пусть, например, триггеры 8 и 9 уиравления установлены в иоложение «1, а частота подстраиваемого генератора 1 выше частоты эталонного генератора 2. При этом началь ;ая расстройка больше нолосы захвата, но меньше полосы удержания. В этом е;1учае па выходе схемы «И 15 частотного детектора 18 появятся импу.тьсы, которые проходят че)ез схему «И 12 и опрокидывают триггер 8 управления. В результате перекрывается ключ 3 и шунтируется элемент памяти блока 6 памяти, что вызывает нрекращепис выборок из пилообразного напряжения фазоюго детекюра н устаиовленне мнннмального панряжепия на выходе блока 6 памяти, следствием чего является быстрое уменьшение напряжения на выходе фильтра иижпих частот 7, приводящее к быстрому уменьшению частоты нодстраиваемого генератора 1.

При наличии импульсов на выходе схемы «И 15 триггер 13 памяти устанавливается в положение, при котором разрешающий потенциал прикладывается к управляющему входу схемы «И 10. Поэтому при совпадении импульсов в цепях 21 и 22 иодтверждастся первоначальное положение триггера 9 управления и не прерывается целесообразный процесс сближения частот генераторов 1 н 2. Когда частота подстраиваемого геператора 1 станет несколько меньше частоты эталонного генератора 2, появятся импульсы на выходе схемы «И 17 частотного детектора 18, которые опрокинут триггер 13 памяти в положение, при котором разрешающий потенциал прикладывается к управляющему входу схемы «И 11. При этом триггер 9 управления остается в исходном состоянии, так как триггер 8 находитея в состояиии «О н схема «II 14 закрыта. Когда импульсы в цепях 21 н 22 совпадут, выходной имнульс схемы «И 11 установит триггер 8 управления в исходное

состояние. С этого момента време): включается К.1ЮЧ 3, восстанав,тивае:ся леток 1мнульсов выборок на входе фазового детектора и прекращается шу ггнрова ;не элеме11та памятп блока 6 памяти. В момент установления триггера 8 унравления в исходное сосгоя1;ие заиускае1ся рас1ИИ|)итель имиу/шсов 19. длительность имнульса KOiOpoio неско;:1 ко больше максима. возможного периода подетраиваемого reiiepaTopa 1. Импульс раеширителя 19 удерживает в закрытом состоянии схему «П 14, нск.тючая возможность онрокидывания триггера 9 унравления н отключения цеии иодачи эталонного еигнала на фазовый детектор 5, что необходимо для поддержання сложившнхся благоприятных для устано1 ления синхронизма начальных условий. Действительно, так как в нервый момогг и.мнульсы в цепях 21 и 22 совнада;1Н и частота подст)аиваемого генератора 1 стала меньHie частоты эталонного генерато)а 2. то выборка осун1,ествляется из началыюго этапа формнрования пилообразного напряжения фазового детектора 5. а для комнепсании большого начального нревышення частоты нодстраиваемо|-о геиерато1)а 1 над частотой эталонного i-енератора 2 необходимо малое напряжение па выходе фазового детектора 5. Если частота иодст)аивасмого генератора 1 меньше частоты эталонного генератора 2. устройство работает аналогичио, но нрерывание нотока имну;1ьеов иа входе фазового деTeKTOjJa производится вторым ключом 4. В р-езультате генератор вилообразного напряжения фазового детектора 5 не запускается и иапряжеиие на eio выходе и выходе блока О памяти устанавливается максимальным. Напряжеиие на выходе фильтра частот 7 быстро нарастает, уве.тичивая частоту нодстраиваемого геиератора 1. Когда знак ошибки ио частоте изменится, сработает частотный детскгор 18, онрокинется трнггер 13 памятн н совпадение нмпу.тьсов в ценях 21 и 22 приведет к установлению тригтера 9 управлення в 1сходпое состояние н замыканию второго ключа 4. Контур унравления замыкается при благоприятных условиях, так как выборка производится из конечного этапа формирования инлообраз1:ого наиряжения фазового детектора 5, а д.тя ко.миенсации большоIo начального иревышения частоты эталонного генератора 2 над частотой иодстраиваемого геиератора 1 иеобходимо большое напряжение на выходе фазового детектора 5.

Ире д м е Г и з о б р е т е н и я

Устройство импульсно-фазовой автоподстройки частоты, содержащее носледовательно соедииенные в кольцо иодстраиваемый генератор, нервый ключ, фазовый детектор, соединенный через второй ключ с эталонным генератором, н блок намяти, а также две ехемы «И и частотный детектор, по.тключенные

к выходам подстраиваемого и эталонного генераторов, причем другие входы схем «И подсоединены к соответствующим выходам триггера памяти, подключенного к выходам частотного детектора, а управляющий вход каждого из указанных ключей соединен с выходом соответствующей схемы «И через триггер управления, отличающееся тем, что, с целью увеличения быстродействия, вторые входы триггеров управления соединены с соответствующими выходами частотного детекб

тора через дополнительные схемы «И, при этом дополнительная схема «И, подключенная к триггеру управления первым ключом, соединена непосредственно и через расширитель импульсов с выходом триггера управления вторым ключом, а дополнительная схема «И, подключенная к триггеру управления вторым ключом, соединена непосредственно и через другой расширитель импульсов с выходом триггера управления первым ключом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для частотно-фазовой автоподстройки | 1986 |

|

SU1405107A1 |

| Устройство для измерения скорости телеграфирования | 1974 |

|

SU547042A1 |

| Демодулятор сигналов частотнойТЕлЕгРАфии | 1979 |

|

SU849528A1 |

| Синтезатор частот | 1973 |

|

SU479215A1 |

| Устройство тактовой синхронизации с дискретным управлением | 1979 |

|

SU951739A1 |

| Устройство фазовой автоподстройки частоты | 1982 |

|

SU1117838A1 |

| Цифровой частотный детектор | 1980 |

|

SU919073A2 |

| УСТРОЙСТВО ИМПУЛЬСНО-ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ ГЕНЕРАТОРА | 1967 |

|

SU224608A1 |

| Устройство тактовой синхронизации с дискретным управлением | 1983 |

|

SU1124442A2 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

Авторы

Даты

1975-09-15—Публикация

1973-01-09—Подача