1

Изобретение относится к радиотехнике и может использоваться в ситемах радиосвязи и измерительной техники.

По основному авт. св. 574864 известен цифровой частотно-фазовый детектор, содержащий два основных триггера, первые выходы которых подключены к входам узла сброса, выход которого соединен с первыми входами основных триггеров, два ключа, дополнительный триггер и два блока опознавания последовательности импульсов, первые входы котор соединены с вторыми входами основны триггеров а выходы дополнительного триггера подключены к управлякядим входам ключей, информационные входы которых соединены с вторыми выходами основных триггеров и вторыми входами блоков опознавания последовательности импульсов, выходы которых подключены к входам дополнительного триггера.

Однако этот детектор имеет недостаточное быстродействие.

Целью изобретения является повышение быстродействия.

Для этого в цифровой частотнофазовый детектор, содержащий два

основных триггера, первые выходы которых подключены к входам узла сброса, выход которого соединен с первьи«1и входами основных триггеров, два ключа, дополнительный триггер и два блока опознавания последовательности импульсов, первые входы которых всоединены с вторыми входами основных триггеров, а выходы допол0нительного триггера подключены к управляющим входам ключей, информационные входы которых соединены с вторыми выходами основных триггеров и вторыми входами блоков опознавания пос5ледовательности импульсов, выходы подключены к входам дополнительного триггера, введены четыре элемента И-НЕ, инвертор, два элемента задержки и триггер индикации.

0 Причем входы первого элемента И-НЕ подключены к выходам блоков опознавания последовательности импульсов, первые входы второго и третьего элементов И-НЕ подключены к управ5л;иощим входам ключей, вторые входы второго и третьего элементов И-НЕ объединены и соединены с выходом инвертора, подключенного своим входом к выходу узла сброса, третьи

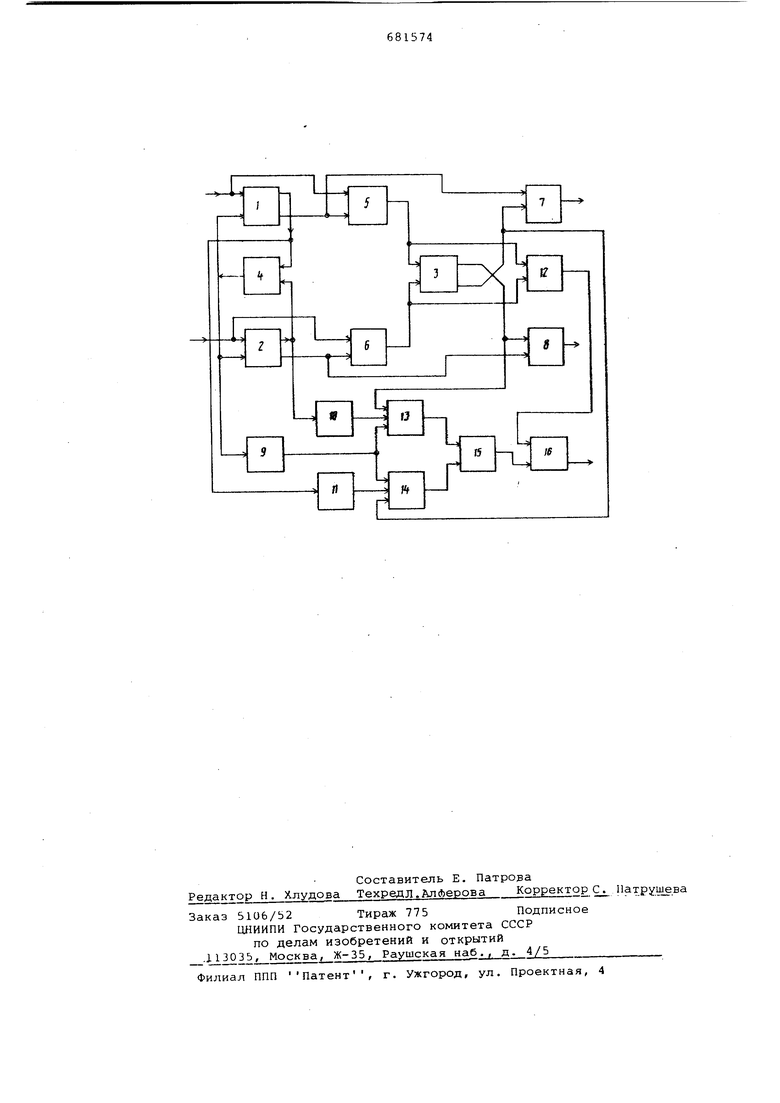

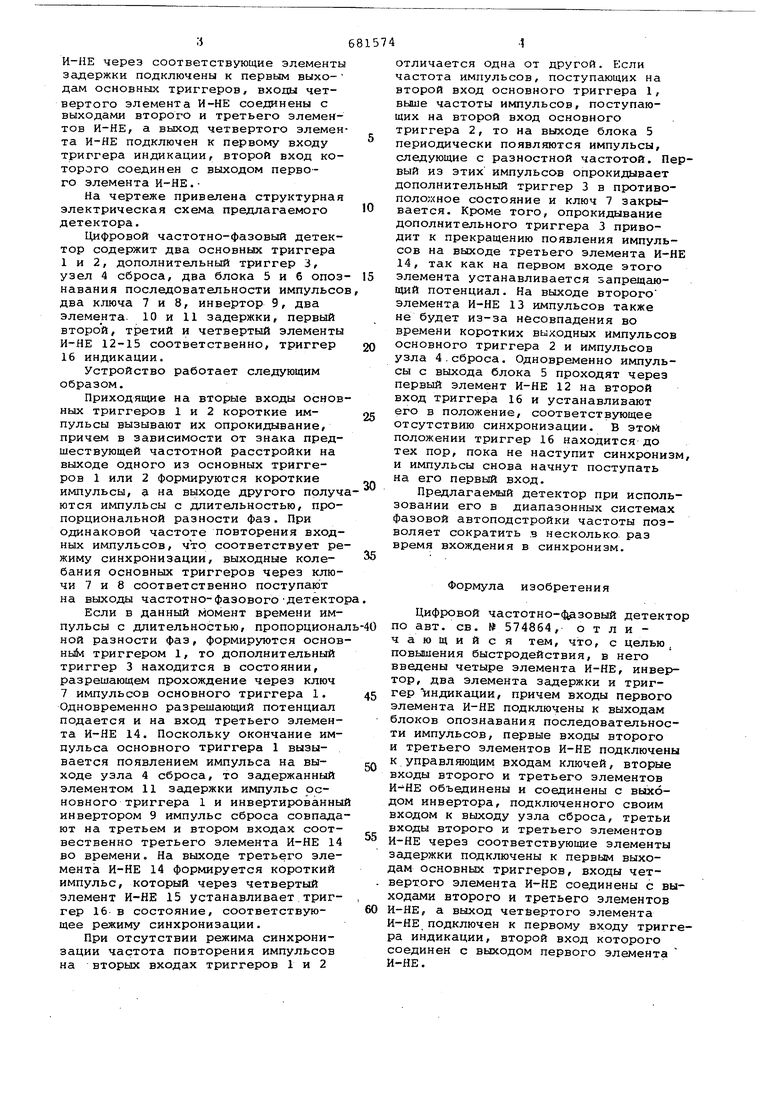

0 входы второго и третьего элементов И-НЕ через соответствующие элементы задержки подключены к первым выходам основных триггеров, входы четвертого элемента И-НЕ соединены с выходами второго и третьего элементов И-НЕ, а выход четвертого элемен та И-НЕ подключен к первому входу триггера индикации, второй вход которого соединен с выходом первого элемента И-НЕ. На чертеже привелена структурная электрическая схема предлагаемого детектора. Цифровой частотно-фаэовый детектор содержит два основных триггера 1 и 2, дополнительный триггер 3, узел 4 сброса, два блока 5 и 6 опоз навания последовательности импульсо два ключа 7 и 8, инвертор 9, два элемента. 10 и 11 задержки, первый второй, третий и четвертьой элементы И-НЕ 12-15 соответственно, триггер 16 индикации. Устройство работает следующим образом. Приходящие на вторые входы основ ньох триггеров 1 и 2 короткие импульсы вызывают их опрокидывание, причем в зависимости от знака предшествующей частотной расстройки на выходе одного из основных триггеров 1 или 2 формируются короткие импульсы, а на выходе другого получ ются импульсы с длительностью, пропорциональной разности фаз. При Одинаковой частоте повторения входных импульсов, что соответствует ре жиму синхронизации, выходные колебания основных триггеров через ключи 7 и 8 соответственно поступают на выходы частотно-фазовогоДетекто Если в данный момент времени импульсы с длительностью, пропорциона ной разности фаз, формируются основ ный триггером 1, то дополнительный триггер 3 находится в состоянии, разрешающем прохождение через ключ 7 импульсов основного триггера 1. Одновременно разрешающий потенциал подается и на вход третьего элемента И-НЕ 14. Поскольку окончание импульса основного триггера 1 вызывается появлением импульса на выходе узла 4 сброса, то задержанный элементом 11 задержки импульс основного триггера 1 и инвертированны инвертором 9 импульс сброса совпада ют на третьем и втором входах соот вественно третьего элемента И-НЕ 1 во времени. На выходе третьего эле мента И-НЕ 14 формируется короткий импульс, который через четвертый элемент И-НЕ 15 устанавливает триг гер 16- в состояние, соответствующее режиму синхронизации. При отсутствии режима синхронизации частота повторения импульсов на вторых входах триггеров 1 и 2 отличается одна от другой. Если частота импульсов, поступающих на второй вход основного триггера 1, вьдпе частоты импульсов, поступающих на второй вход основного триггера 2, то на выходе блока 5 периодически появляются импульсы, следующие с разностной частотой. Первый из этих импульсов опрокидывает дополнительный триггер 3 в противоположное состояние и ключ 7 закрывается. Кроме того, опрокидывание дополнительного триггера 3 приводит к прекращению появления импульсов на выходе третьего элемента И-НЕ 14, так как на первом входе этого элемента устанавливается запрещающий потенциал. На выходе второго элемента И-НЕ 13 импульсов также не будет из-за несовпадения во времени коротких выходных импульсов основного триггера 2 и импульсов узла 4,сброса. Одновременно импульсы с выхода блока 5 проходят через первый элемент И-НЕ 12 на второй вход триггера 16 и устанавливают его в положение, соответствующее отсутствию синхронизации. В этом положении триггер 16 находится до тех пор, пока не наступит синхронизм, и импульсы снова начнут поступать на его первый вход. Предлагаемый детектор при использовании его в диапазонных системах фазовой автоподстройки частоты позволяет сократить в несколько раз время вхождения в синхронизм. Формула изобретения Цифровой частотно-фдзовый детектор по авт. св. № 574864, отличающийся тем, что, с целью, повышения быстродействия, в него введены четыре элемента И-НЕ, инвертор, два элемента задержки и триггер 1ндикации, причем входы первого элемента И-НЕ подключены к выходам блоков опознавания последовательности импульсов, первые входы второго и третьего элементов И-НЕ подключены к управляющим входам ключей, вторые входы второго и третьего элементов И-НБ объединены и соединены с выходом инвертора, подключенного своим входом к выходу узла сброса, третьи входы второго и третьего элементов И-НЕ через соответствующие элементы задержки подключены к первым выходам основных триггеров, входы четвертого элемента И-НЕ соединены с выходами второго и третьего элементов И-НЕ, а выход четвертого элемента И-НЕ подключен к первому входу триггера индикации, второй вход которого соединен с выходом первого элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотно-фазовой детектор | 1976 |

|

SU574864A1 |

| Цифровой периодомер | 1985 |

|

SU1337801A1 |

| Электронно-счетный частотомер | 1981 |

|

SU1041947A1 |

| Устройство цветовой синхронизации телевизионного приемника системы "СЕКАМ | 1980 |

|

SU985975A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Устройство для приема и передачи информации о подвижных объектах | 1989 |

|

SU1605274A2 |

| Устройство для распознавания образов | 1986 |

|

SU1361589A1 |

| УСТРОЙСТВО РАСПОЗНАВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1983 |

|

SU1841012A1 |

| Устройство синхронизации видеомагнитофона | 1981 |

|

SU965015A1 |

| Устройство сопряжения с двухпроводной абонентской линией | 1989 |

|

SU1713118A1 |

Авторы

Даты

1979-08-25—Публикация

1977-09-14—Подача