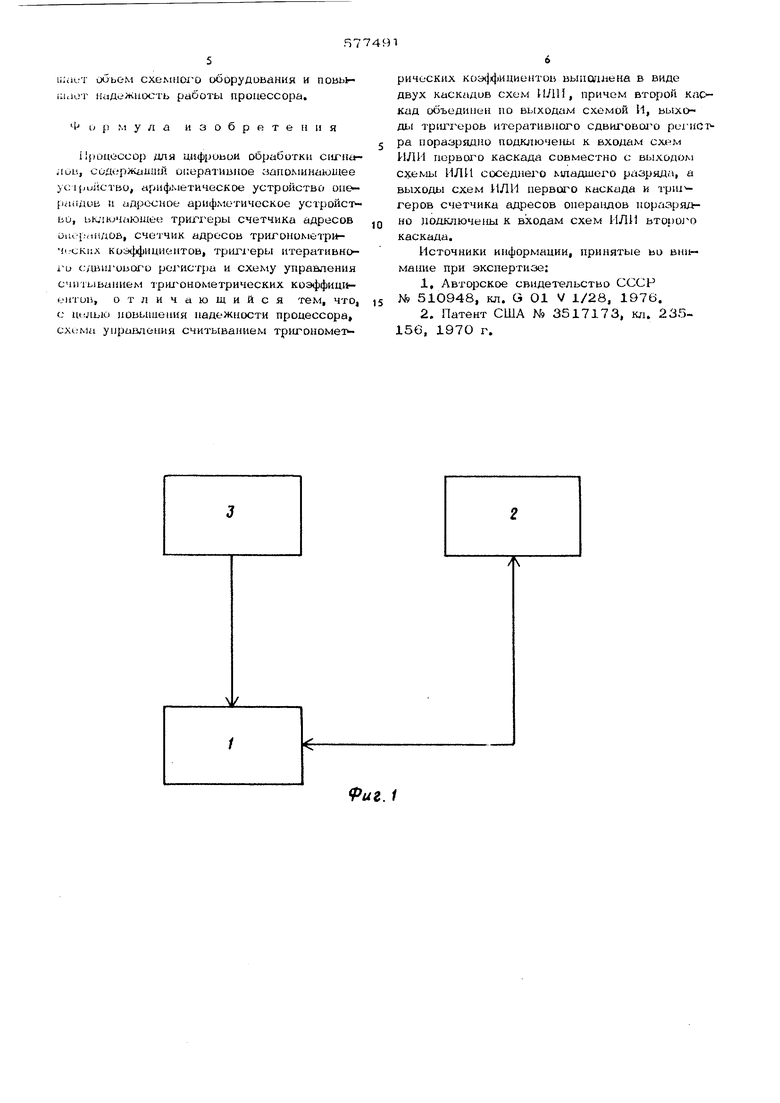

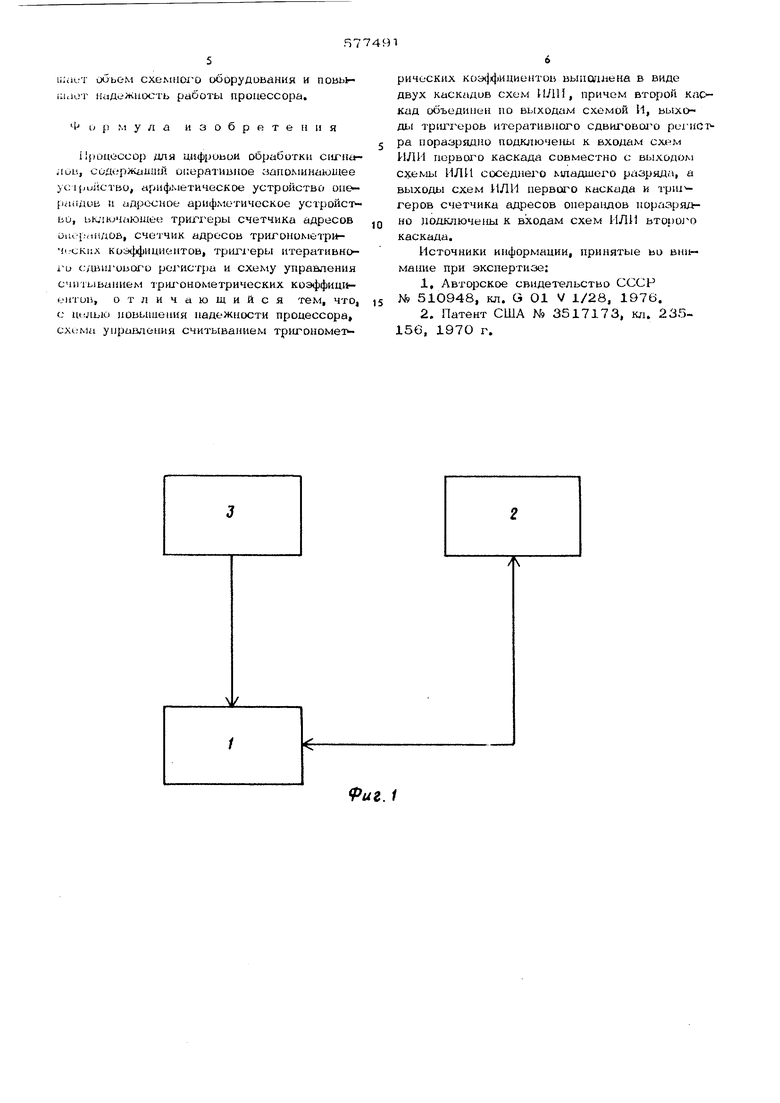

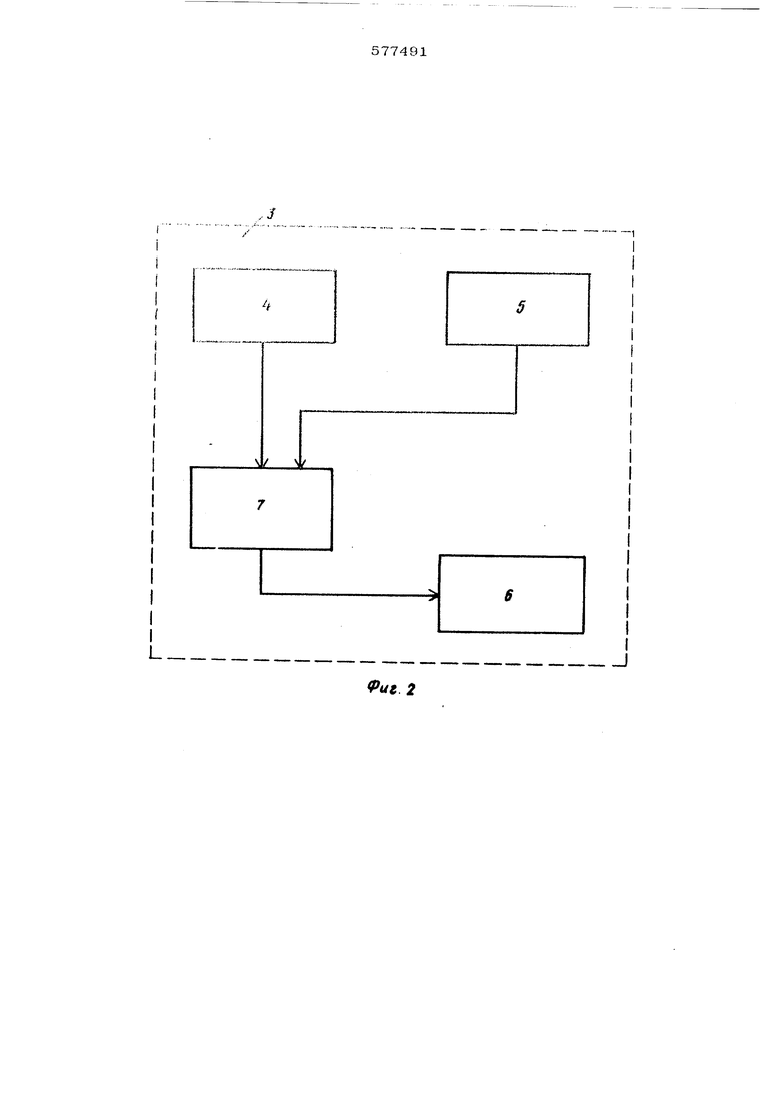

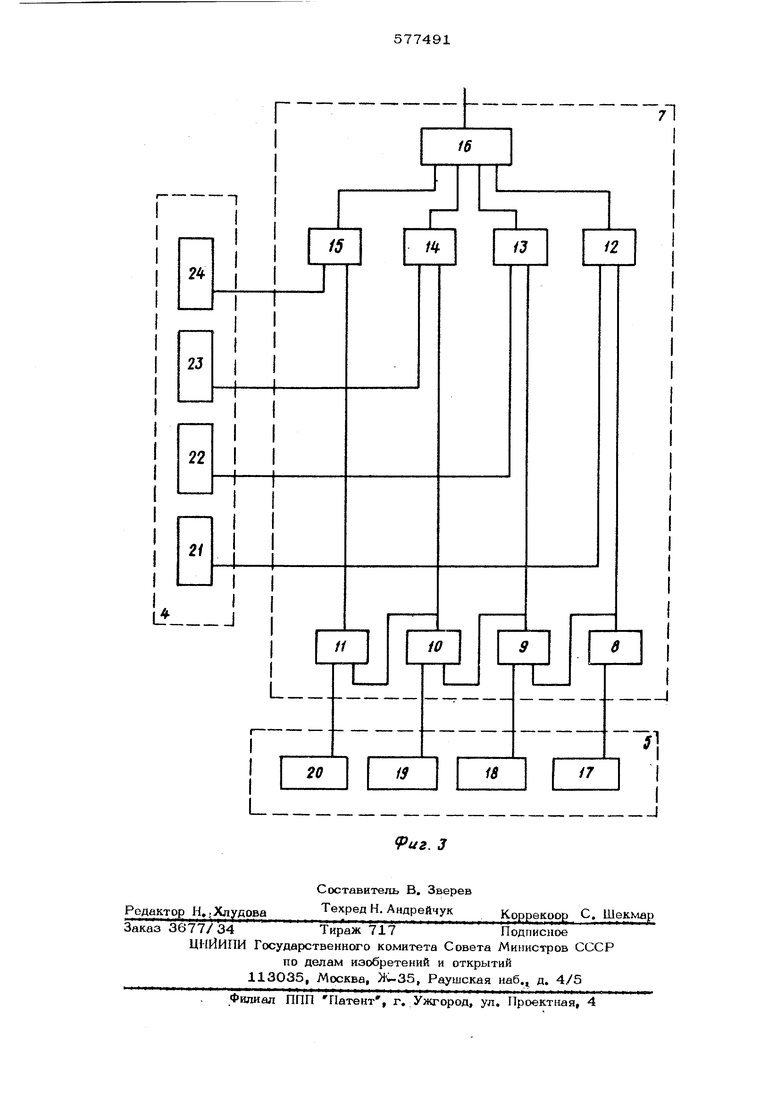

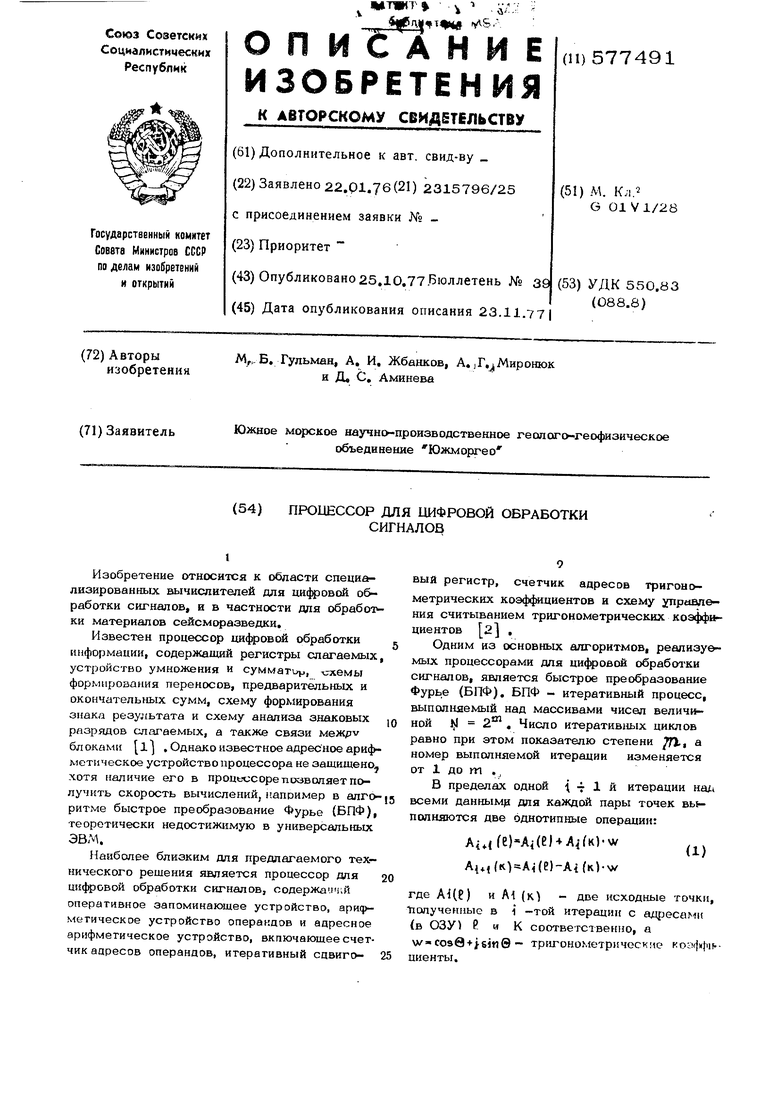

Эти KoadxbimsieHTbi для числа точек iV рао считываются заранее в количестве и хра1;яах;я в оперативной памяти, В каждой итерации дпя вычислений поформулам (1) необходимы значения тригономв трическнх коэффициентов в количестве, зависящем от номера выполняемой итерации: иефБОЙ - одно значение,во второй - два, в третьей - четыре и т.д., в последней итерации необходимо считать из оперативной пам4 ти все - значений тригонометрических фициентоБ. В известном процессоре схема управления считыванием тригонометрических коэффициентов фиксирует состояние, при котором для расчета очередной пары точек необходимо использовать новое значение тригонометрического коэффициента, считанного в буферные регистры из оперативной памяти в пре дыдущем цикле смены трш онометрического коэффициента. В указанный момент времени значение тригонометрического коэффициента передает ся из буферных регистров в регистры множителя арифметического устройства операндо из оперативной памяти в буфер 1ые регистры считывается очередное значение трю онометр .коэффициентов и начинается цикл расчета очередной пары точек. Недостатком описанного процессора 5тл51ет.ся необходимость введения в его состав y буферных регистров с управл$нощей логикой для записи - считывания информации-, что приводит к увеличению схемного оборудования и снижению надежности работы процессора. Целью изобретения является повышение надежности процессора,,. Это достигается , тем, что в предлагаемом процессоре схема управления считыванием тригонометрических коэффициентов содержит два каскада схем ИЛИ, причем рторой кас кад объединен по выходам схемой И, выходы xpuriepOB итеративного сдвшового ре гистра поразрядно подключены к входам схем ИЛИ первогр каскада совместно с вь ходом схемы ;ИЛИ сииьднего младшего разряда, а выходы схем ИЛИ первого каскада и триггеров счетчика а/цэесов операндов поразрядно подключены к входам схем ИЛИ второго каскада. В этом случае схема управления считыванием тригонометрических коэффициентов фик сирует цикл, предалествующкй циклу расчета пары точек, для которого необходимо новое значение тршонометрического коэффициента и обеспечивает синхронизацию считывания триг номет|)1 ческих коэффициентов из оперативной па мяти непосрецственно врегисгры арифметическогоустройства операндов. Елш одаря этому, от падает необходимость в буферных регистрах и связанной с нцмн управляющей логике, сущесрве к но сокращается обтаем схемнс го оборудования и повышается надежность работы процессора. На фиг, 1 изображена блок-схема предла-гаемого процессора; на фиг. 2 - блочная схема адресного арифметического устройства; на фиг. 3 - схемд управления считыванием тригонометрических коэффициентов. Процессор содержит оперативное запоминающее устройство 1, арифметическое устройство операндов 2 и адресное арифметическое устройство 3., Адресное арифметическое устройство 3 содержит счетчик адресов операндов 4, итеративный сдвиговый регистр 5, счетчик адресов тригонометрических коэффициентов 6 и схему управления считыванием, тригономеррических коэффициентов 7, Схема управления считыванием тригонометрических коэффициентов 7 для случая, например, четырехразрядного (четырехбитного) адреса содержит схемь ИЛ И 12,13,14,15 второго каскада, объединенные по выходам схемой И 16, Схема управления считыванием тригонометрических коэффицнентов дпя адресов с большей разрядностью строится аналогично схеме, приведенной на фиг, 3, путем добавления в каждом каскаде одной двухвходовой, схемы ИЛИ и добавлением одного входа в схеме И на каждый дополнительный двои ный разряд адреса, Вхо.дь триггеров 17,18,19,20 итеративгного сдвигового регистра 5 подключены к соответствующим входам схем ИЛИ 8,9,10, 11, ко вторым входам которых подключены выходы схем ИЛИ соседних младщих разр дoвf выходы схем ИЛИ 8,9,10,11,подключ&ны соответственно к входам схем ИЛИ 12, 13,14,15, ко вторым входам которых по; ключены выходы триггеров 21,22,23,24, соответствующих разрядов счетчшса адресов операндов 4, Всякий раз в I -той итерации единичное состояние на выходе схемы И указывает на необходимость считывания нового тригонометрического коэффициента в регистры множителя арифметического устройства операндов. Применение в предлагаемом процессоре вышеприведенной схемы управления считььванием тригонометрических коэффициентов обеопечило считывание тригонометрических коэ фициентов непосредственно в рабочие регист ры арифметического устройства операндов, что исключает в процессоре буфернъге регисч ры с управляющей логикой, испогшауемые в практике, и за счёт этого существенно умень

inaeT ооьем схемисчО ооорудивання и повььiiuKiT Надежность работы процессора.

Ф и р мула н 3 о б р и т е и и я

ilfionoccop для цнфроьои обработки citrMtaлов, содержаииш окератианое запоминающее yciiJuiicTBO, арифметическое устройство опеpaiiAuii 1 адресное арифметическое устройств во, ыччючающее трипперы счетчика адресов ияи-риидов, счетчик адресов тригонометриMiCKiiX коэффициентов, трш херы итеративного сдвшоьаг о pejMiCTpa и схему управления сншываиием траг онометрических коэффищ OHToii, отличающийся тем, что, с и(лыо ноБЫшения надежности процессора, схюма управления считыванием тригонометрических коэ4х{)ициентов выпшаена в виде двух каскадов схем ИЛИ, причем второй какад объединен но выходам схемой И, вь ходы тршгеров итеративного сдвигово1 о регис ра поразрядно подключены к входам сх(м ИЛИ первого каскада совместно с выходом схемы ИЛИ сосед11его младшего разряда, а выходы схем ИЛИ первоа о каскада и три: геров счетчика адресов операндов поразрядно подключены к входам схем ИЛИ BTOpoJo каскада.

Источники информации, принятые во внимание при экспертизе:

1,Авторское свидетельство СССР № 51О948, кл. G 01 V 1/28, 1976.

2.Патент США N9 3517173, кп. 235156, 1970 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Процессор быстрого преобразования Фурье | 1983 |

|

SU1119027A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1277135A1 |

| Устройство для реализации быстрого преобразования Фурье последовательности с нулевыми элементами | 1983 |

|

SU1119025A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1983 |

|

SU1111173A1 |

иг. 1

иг 2

1

24

Авторы

Даты

1977-10-25—Публикация

1976-01-22—Подача