Изобретение относится к цифровой вычислительной технике и может быть использовано при решении задач фильтрации и идентификации сигналов,:

Цель изобретения - расширение функциональных возможностей устройства за счет вычисления быстрых преобразований в базисах дискретных ортогональных функций по ПРОИЗВОЛЬНОМ ; основанию.

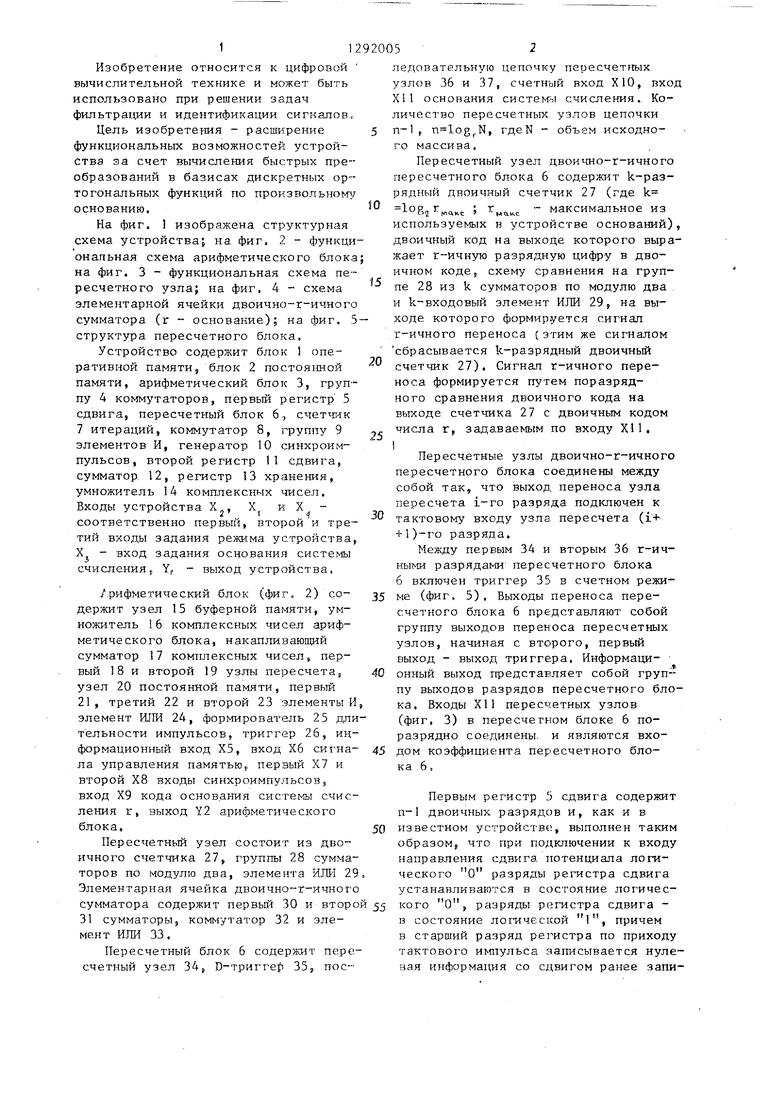

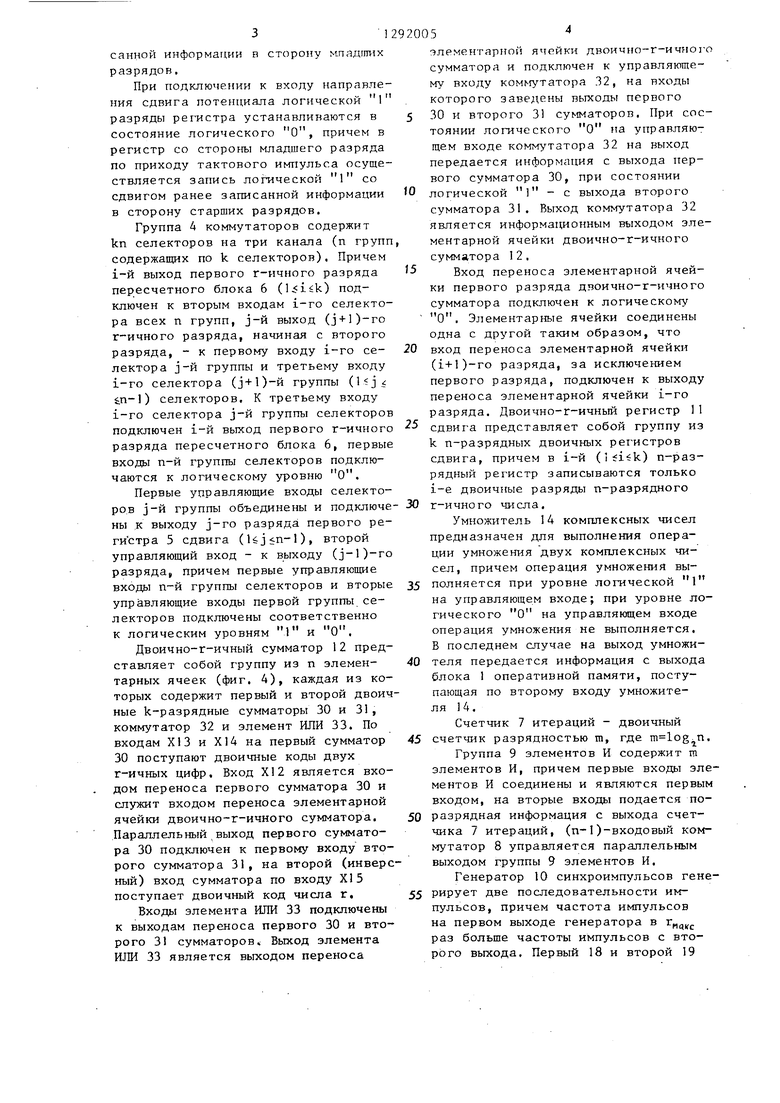

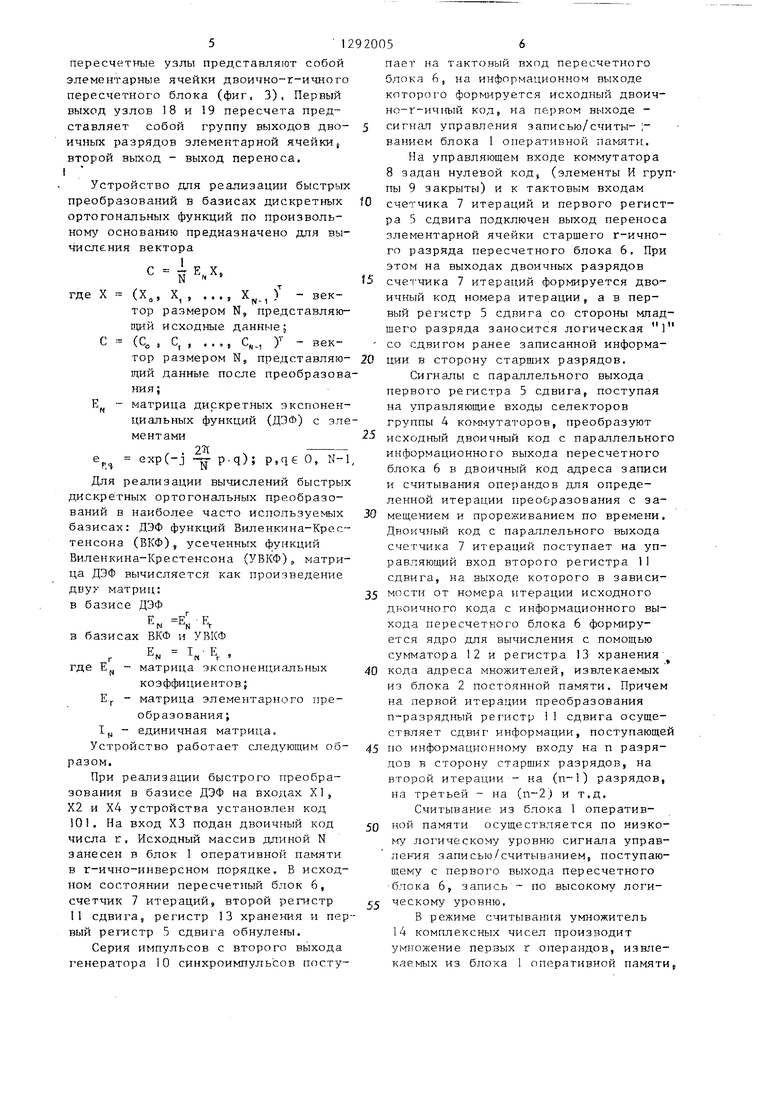

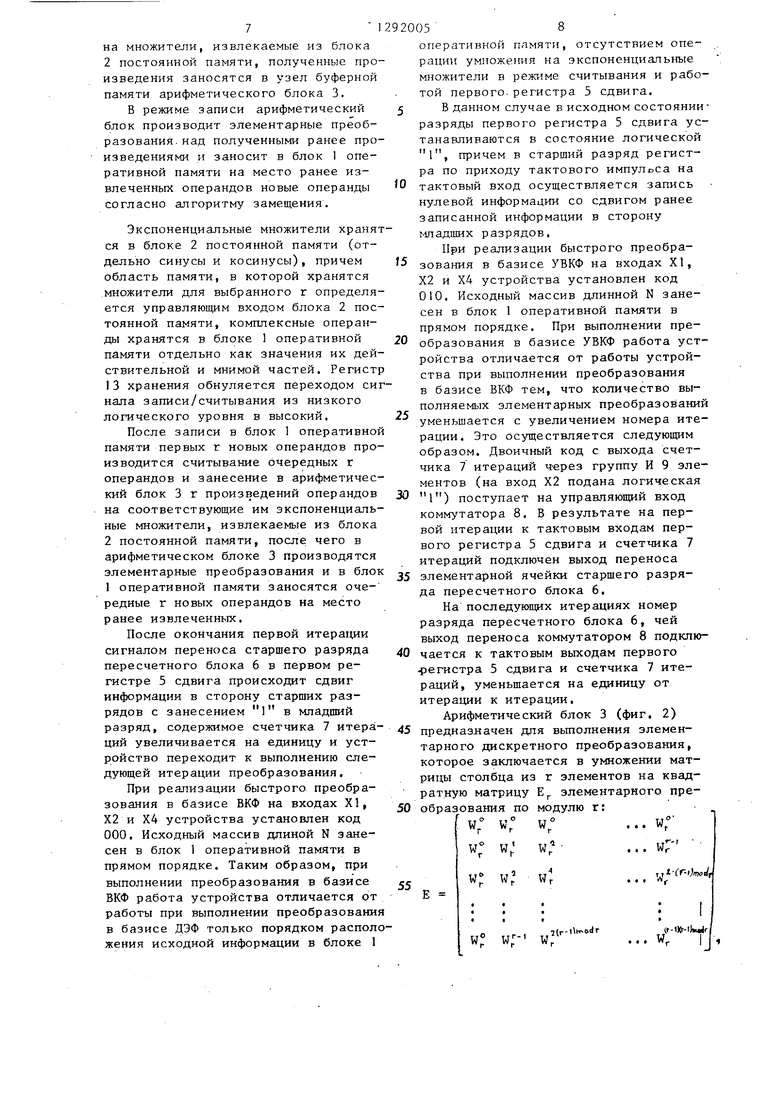

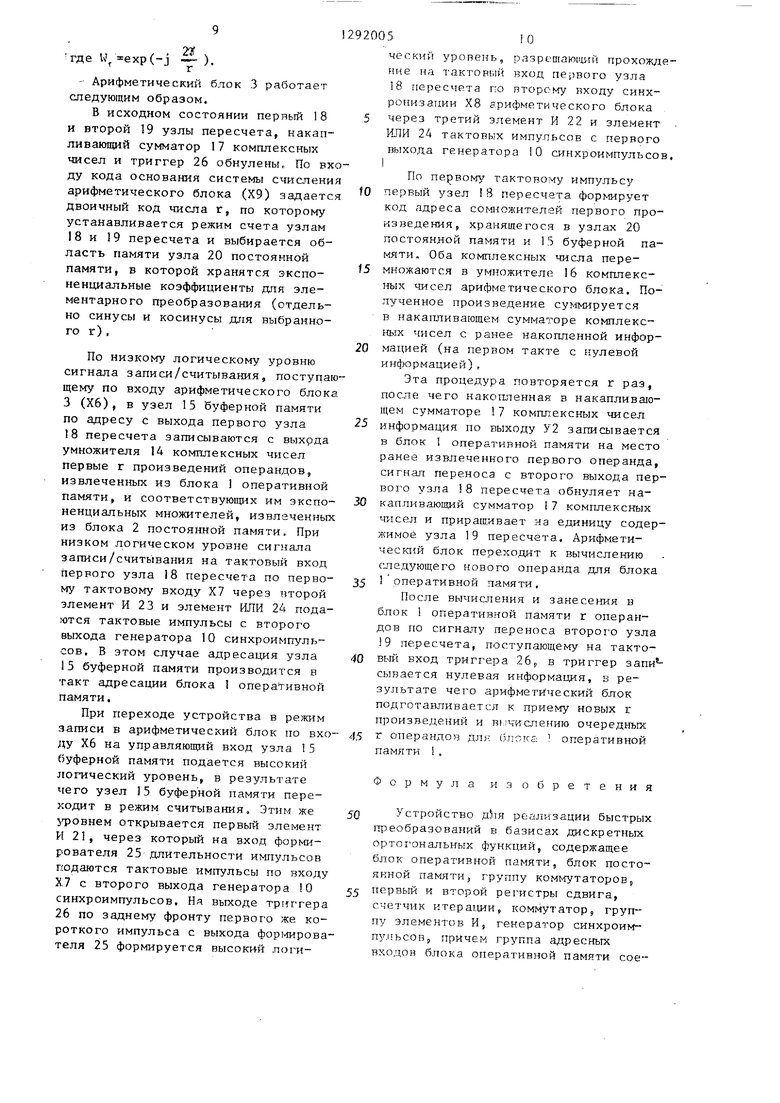

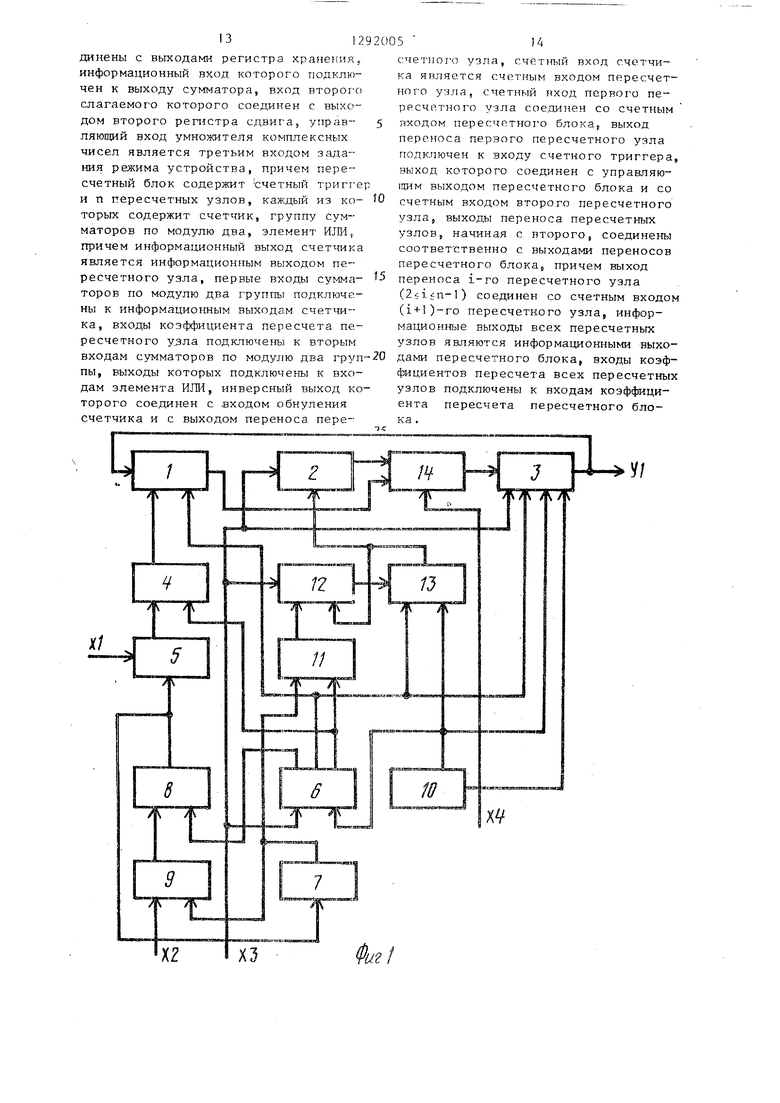

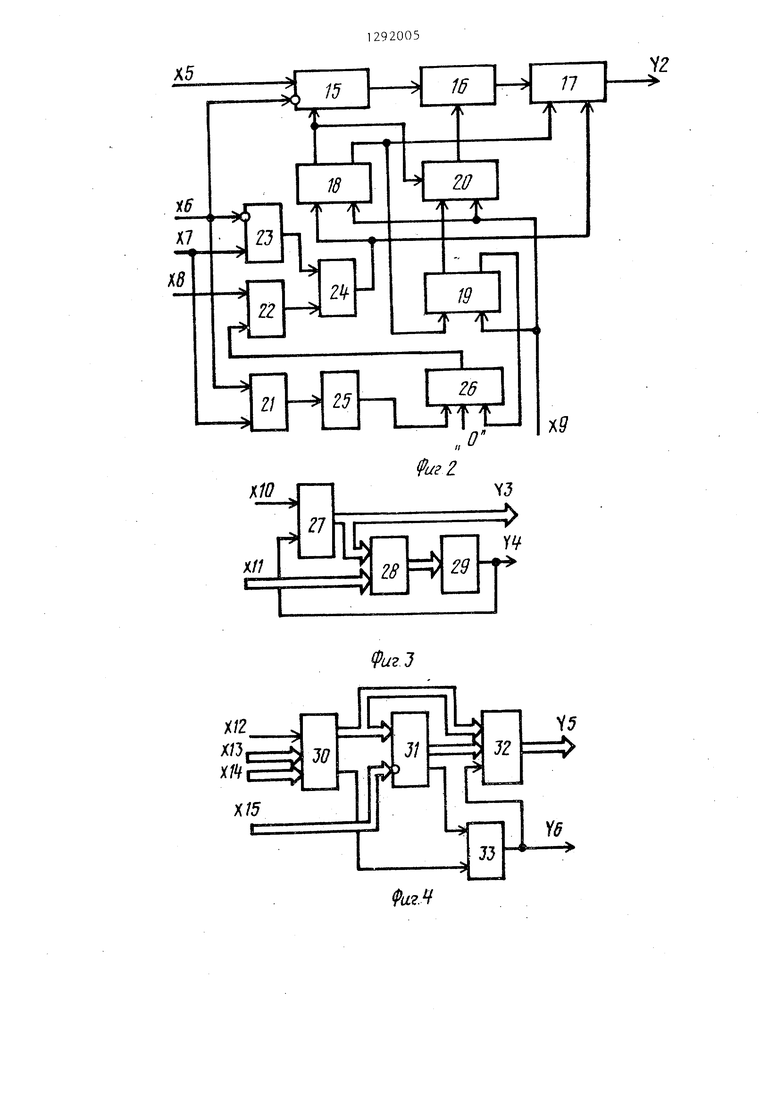

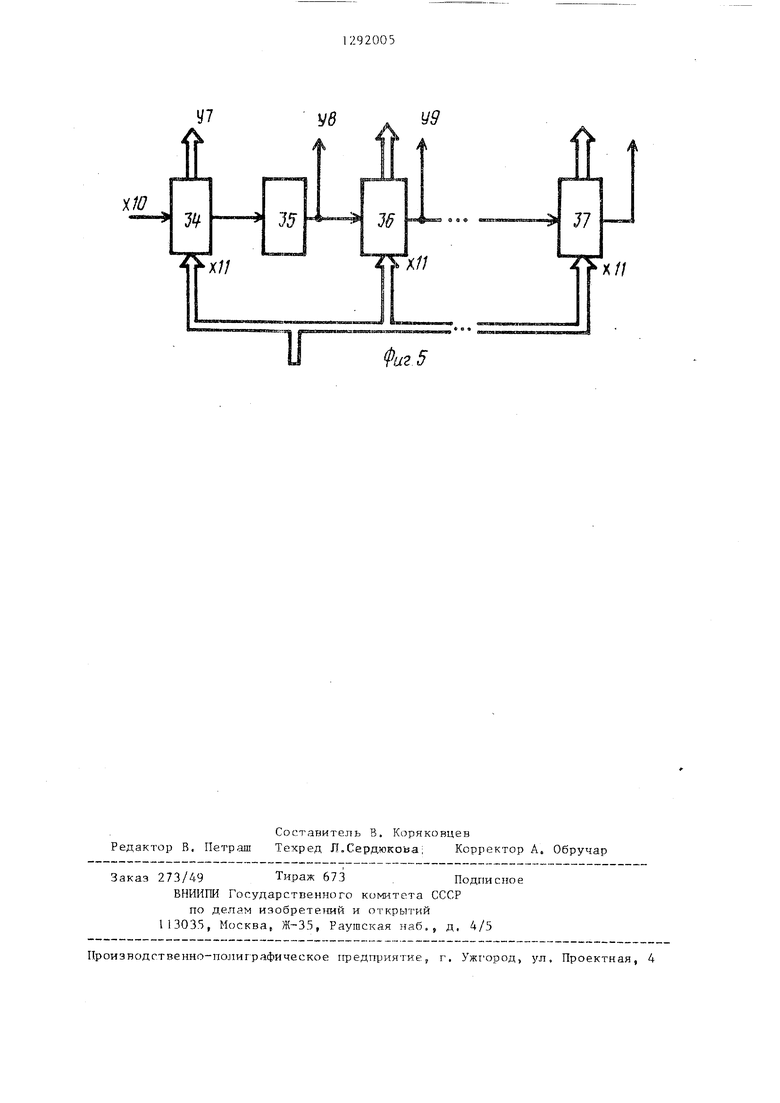

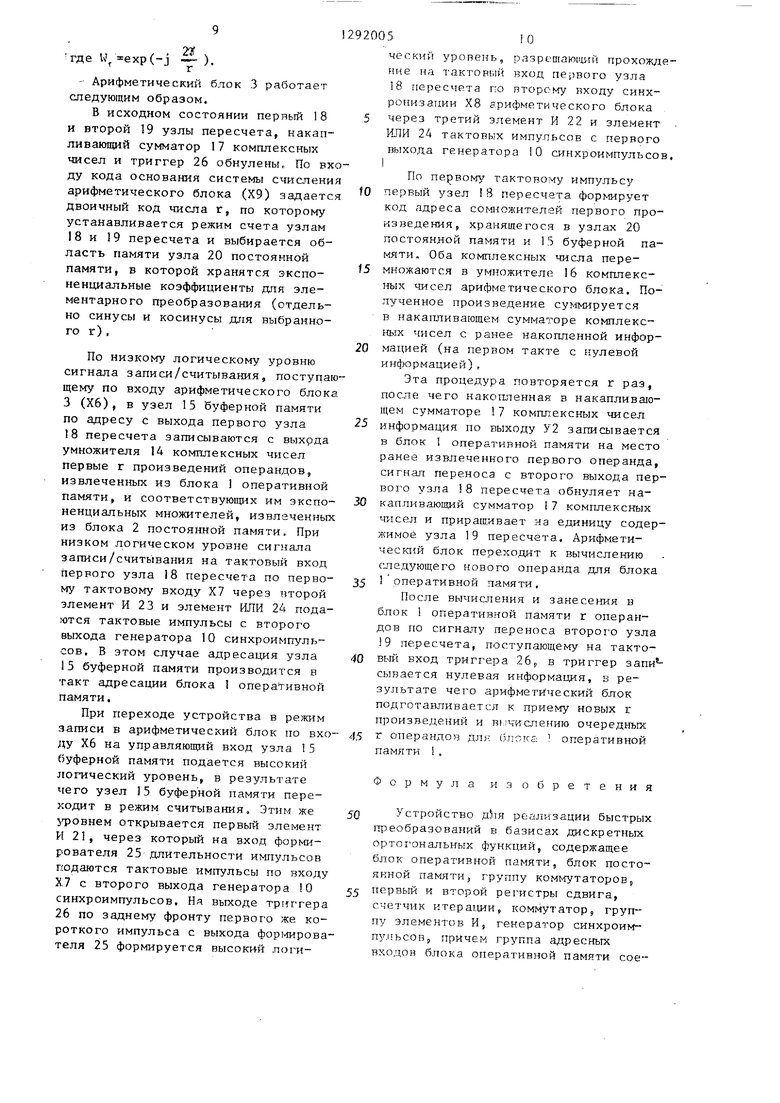

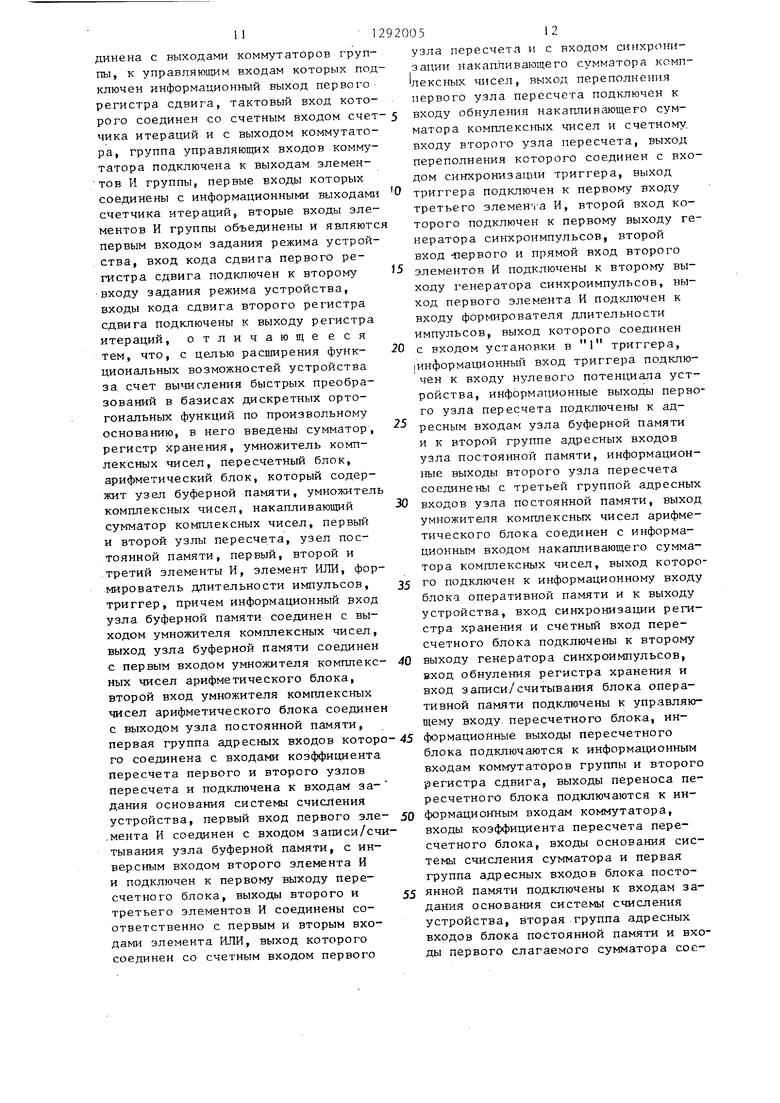

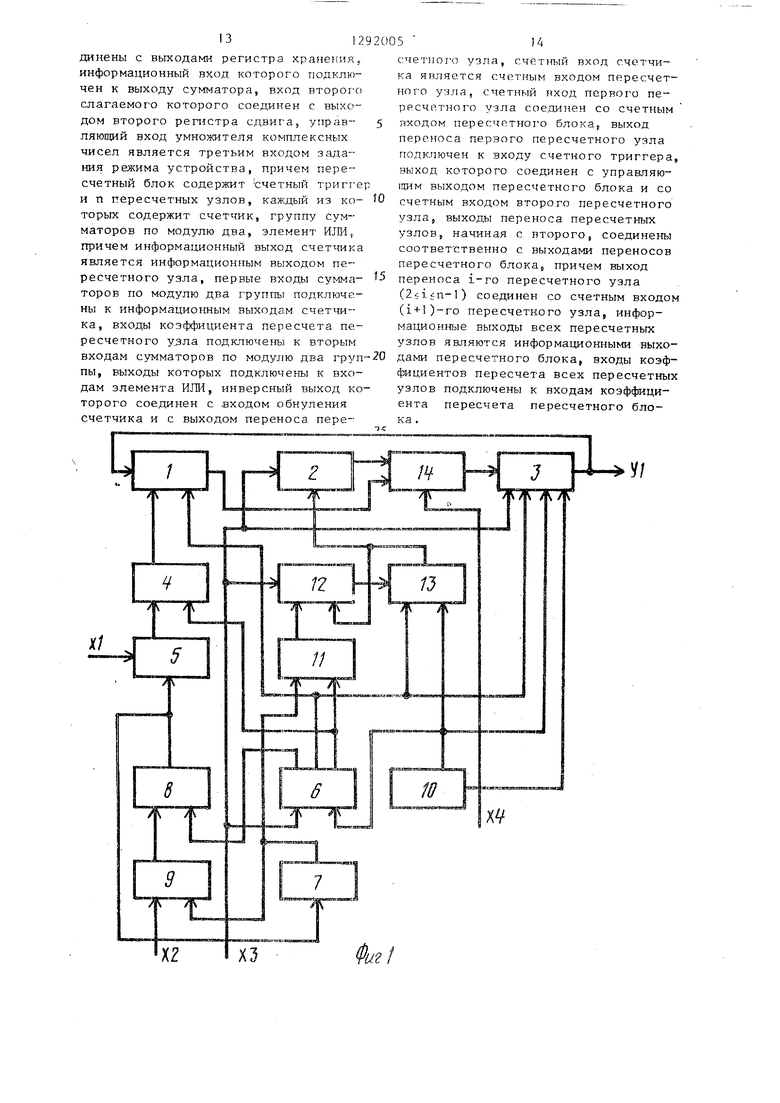

На фиг. изображена структурная схема устройства на фиг. 2 - функциональная схема арифметического блока на фиг, 3 - функциональная схема пересчетного узла; на фиг, 4 - схема элементарной ячейки двоично-г-ичного сумматора (г - основание); на фиг. 5 структура пересчетного блока.

Устройство содержит блок 1 оперативной памяти, блок 2 постоянной памяти, арифметический блок 3, группу 4 коммутаторов, первый регистр 5 сдвига, пересчетный блок 6., счетчтлк 7 итераций, коммутатор 8, группу 9 элементов И, генератор 10 синхроимпульсов, второй регистр 11 сдвига, сумматор. 12, регистр 13 хранения, умножитель 14 комплексных чисел. Входы устройства X , X и X - соответственно первый, второй и третий входы задания режима устройства, Х - вход задания основания системы счисления 5 Y, - выход устройства.

/.рифметический блок (фиг, 2) содержит узел 15 буферной памяти, умножитель 16 комплексных чисел арифметического блока, накапливающий сумматор 17 комплексных чисел, первый 18 и второй 19 узлы пересчета, узел 20 постоянной памяти, первый 21, третий 22 и второй 23 элементы И, элемент ИЛИ 24, формирователь 25 длительности импульсов, триггер 26, ицформациониый вход Х5, вход Х6 сигна- 45 дом коэффициента пересчетного бло- ла управления памятью,, первый Х7 и второй Х8 входы синхроимпульсов, вход Х9 кода основ.ания системы счисления г, выход Y2 арифметического блока,50

Пересчетный узел состоит из двоичного счетчика 27, группы 28 сумматоров по модулю два, элемента ИЛИ 29, Элементарная ячейка двоично-г-ичного сумматора содержит первьй 30 и второй 55 кого О 31 сумматоры, коммутатор 32 и элемент ИЛИ 33.

Пересчетный блок 6 содержит пересчетный узел 34, D-TpHrrefi 35, поска 6,

Первым регистр 5 сдвига содержи п- двоичных разрядов и, как и в известном устройстве, выполнен таки образом, что при подключении к вход направления сдвига потенциала логического о разряды регистра сдвига устанавливаются в состояние логичес , разряды регистра сдвига - 1, причем

в старший разряд регистра по приход тактового иьшульса записывается нул вая информация со сдвигом ранее зап

920052

ледовательную цепочку пересчетртых узлов 36 и 37, счетный вход Х10, вход XI основания системы счисления.. Количество пересчетных узлов цепочки 5 п f , гдеН - объем исходного массива.

Пересчетный узел двоично-г-ичного пересчетного блока 6 содержит k-раз- рядный двоичный счетчик 27 (где k

to

- максимальное из

15

20

25

30

35

40

1орп

используемых в устройстве оснований),

двоичный код на выходе которого выражает г-ичную разрядную цифру в двоичном коде, схему сравнения на группе 28 из k сумматоров по модулю два . и k-входовый элемент ИЛИ 29, на выходе которого формируется сигнал г-ичного переноса (этим же сигналом сбрасывается k-разрядный двоичный счетчик 27). Сигнал г-ичного переноса формируется путем поразрядного сравнения двоичного кода на выходе счетчика 27 с двоичным кодом числа г, задаваемым по входу XII.

1

Пересч.етные узлы двоично-г-ичного

пересчетного блока соединены между собой так, что выход переноса узла пересчета i-ro разряда подключен к тактовому входу узла, пересчета (i+ +1)-го разряда.

Между первым 34 и вторым 36 г-ич- ными разрядами пересчетного блока 6 включен триггер 35 в счетном режиме (фиг. 5). Выходы переноса пересчетного блока 6 представляют собой группу выходов перен:оса пересчетных узлов, начиная с второго, первый выход - выход триггера. Информаци- онный выход ггредставляет собой группу выходов разрядов пересчетного блока. Входы XII пересчетных узлов (фиг, 3) в пересчетном блоке 6 поразрядно соединены, и являются входом коэффициента пересчетного бло-

кого О

ка 6,

Первым регистр 5 сдвига содержит п- двоичных разрядов и, как и в известном устройстве, выполнен таким образом, что при подключении к входу направления сдвига потенциала логического о разряды регистра сдвига устанавливаются в состояние логичес- , разряды регистра сдвига - 1, причем

кого О

в старший разряд регистра по приходу тактового иьшульса записывается нулевая информация со сдвигом ранее записанной информаг1ии в сторону мпад1т1х разрядов,

При подключении к входу направления сдвига потенциала логической 1 разряды регистра устанавливаются в состояние логического О, причем в регистр со стороны младшего разряда по приходу тактового импульса осуществляется запись логической 1 со сдвигом ранее записанной информации в сторону старших разрядов.

Группа 4 коммутаторов содержит kn селекторов на три канала (п групп содержащих по k селекторов). Причем i-й выход первого г-ичного разряда пересчетного блока 6 () подключен к вторым входам i-ro селектора всех п групп, j-й выход (j-H)-ro г-ичного разряда, начиная с второго разряда, - к первому входу i-ro селектора j-й группы и третьему входу i-ro селектора (j+l)-й группы ( tn-1) селекторов, К третьему входу i-ro селектора j-й группы селекторов подключен i-й выход первого г-ичного разряда пересчетного блока 6, первые входы п-й группы селекторов подключаются к логическому уровню О.

Первые управляющие входы селекторов j-й группы объединены и подключе ны к выходу j-ro разряда первого регистра 5 сдвига (), второй управляющий вход - к выходу (j-l)-ro разряда, причем первые управляющие входы п-й группы селекторов и вторые управляющие входы первой группы селекторов подключены соответственно к логическим уровням 1 и О.

Двоично-г-ичный сумматор 12 представляет собой группу из п элементарных ячеек (фиг. 4), каждая из которых содержит первый и второй двоичные k-разрядные сумматоры 30 и 31, коммутатор 32 и элемент ИЛИ 33. По входам XI3 и Х14 на первый сумматор 30 поступают двоичные коды двух г-ичных цифр. Вход Х12 является входом переноса первого сумматора 30 и служит входом переноса элементарной ячейки двоично-г-ичного сумматора. Параллельный выход первого сумматора 30 подключен к первому входу второго сумматора 31, на второй (инверсный) вход сумматора по входу XI5 поступает двоичный код числа г.

Входы элемента ИЛИ 33 подключены к выходам переноса первого 30 и второго 31 сумматоров Выход элемента ИЛИ 33 является выходом переноса

0

5

0

5

элементарной ячейки двоичьго-г-ичного сумматора и подключен к управляющему входу KOMNfyTaTopa 32, на входы которого заведены выходы первого 30 и второго 31 cyND-iaTOpOB. При состоянии логического О на управляющем входе коммутатора 32 на выход передается информация с выхода первого сумматора 30, при состоянии логической 1 - с выхода второго сумматора 31. Выход коммутатора 32 является информационным выходом элементарной ячейки двоично-г-ичного сумматора 1 2 .

Вход переноса элементарной ячейки первого разряда двоично-г-ичного сумматора подключен к логическому О, Элементарные ячейки соединены одна с другой таким образом, что вход переноса элементарной ячейки (i+l)-ro разряда, за исключением первого разряда, подключен к выходу переноса элементарной ячейки i-ro разряда. Двоично-г-ичный регистр 11 сдвига представляет собой группу из k п-разрядных двоичных регистров сдвига, причем в i-й (Ifisk) п-раз- рядный регистр записываются только i-e двоичные разряды п-разрядного

г-ичного числа.

Умножитель 14 комплексных чисел предназначен для выполнения операции умножения двух комплексных чисел, причем операция умножения выполняется при уровне логической 1

г-ичного числа.

на управляющем входе; при уровне логического О на управляющем входе операция умножения не выполняется. В последнем случае на выход умножителя передается информация с выхода блока 1 оперативной памяти, поступающая по второму входу умножителя 14.

Счетчик 7 итераций - двоичный

счетчик разрядностью т, где .n.

Группа 9 элементов И содержит m элементов И, причем первые входы элементов И соединены и являются первым входом, на вторые входы подается поразрядная информация с выхода счетчика 7 итераций, (п-1)-входовый коммутатор 8 управляется параллельным выходом группы 9 элементов И.

Генератор 10 синхроимпульсов генерирует две последовательности импульсов, причем частота импульсов на первом выходе генератора в т„ раз больше частоты импульсов с второго выхода. Первый 18 и второй 19

пересчетные узлы представляют собой элементарные ячейки двоично-г-ичного пересчетного блока (фиг, 3), Первый выход узлов 18 и 19 пересчета представляет собой группу выходов двоичных разрядов элементарной ячейкиj второй выход - выход переноса, I

Устройство дня реализации быстргз1х преобразований в базисах дискретных ортогональных функций по произвольному основанию предназначено для вычисления вектора

де X (X

- -Ip X

N X

X.

f

векС

р .

РЛ

о N « ч „., тор размером N, представляю- пщй исходные данные; (Со . С, , . . ,, С,, Y - вектор размером N, представляющий данные после преобразования ;

матрица дискретных экспоненциальных функций () с элементами

. . Z Jt

exp(-j Y

p-q); о, N-I,

Для реализации вычислений быстрых дискретных ортогональных преобразований в наиболее часто используемых базисах: ДЭФ функций Виленкина-Крес тенсона (ВКФ), усеченных функций Виленкина-Крестенсона (УВКФ)„ матрица ДЭФ вычисляется как произведение двуу матриц: в базисе ДЭФ

F -F ti N

Y

В базисах ВКФ и УВКФ

где Е,

EN

Т:«-Е,

Е. матрица экспоненциальных коэффициентов; матрица элементарного преобразования ; 1 - единичная матрица. Устройство работает следующим образом.

При реализации быстрого преобразования в базисе ДЭФ на входах XI, Х2 и Х4 устройства установлен код 101. На вход ХЗ подан двоичный код числа г. Исходный массив длиной N занесен в блок 1 оперативной памяти в г-ично-инверсном порядке. Б исходном состоянии пересчетный блок 6, счетчик 7 итераций, второй регистр 11 сдвига, регистр 13 хранения и первый регистр 5 сдвига обнулены.

Серия импульсов с второго выхода генератора 10 синхроимпульсов посту0

5

пает на тактовый вход пересчетного блока 6, на информационном выходе которого формируется исходный двоич- но г-ичнь1й код в на первом выходе - сигнгш управления записью/считы- ;- ванием блока 1 оперативной памяти,.

На управляющем входе коммутатора 8 задан нулевой код, (элементы И группы 9 закрыты) и к тактовым входам счетчика 7 итераций и первого регистра 5 сдвига подключен выход переноса элементарной ячейки старшего г-ично- го разряда пересчетного блока 6. При этом на выходах двоичных разрядов 5 счетчика 7 итерагшй формируется двоичный код номера итерации, а в первый регистр 5 сдвига со стороны младшего разряда заносится логическая со сдвигом ранее записанной информации в сторону старших разрядов.

Сигналы с параллельного выхода первого регистра 5 сдвига, поступая на управляющие входы селекторов группы 4 коммутаторов, преобразуют исходный двоичный код с параллельного информационного выхода пересчетного блока 6 в двоичный код адреса записи и считывания операндов для определенной итерации преобразования с за- 0 мещением и прореживанием по времени. Двоичный код с параплельного выхода счетчика 7 итераций поступает на управляющий вход второго регистра 11 сдвига, на выходе которого в зависи- 5 мости от номера итерации исходного двоичного кода с информационного выхода пересчетного блока 6 формируется ядро для вычисления с помощью cy мaтopa 12 и регистра 13 хранения 0 кода адреса множителей, извлекаемых из блока 2 постоянной памяти. Причем на первой итерации преобразования п-разрядный регистр 11 сдвига осуществляет сдвиг информации, поступающей 5 по информационному входу на п разрядов в сторону старших разрядов, на второй итерации - на (п-) разрядов, на третьей - на (п-2) и т.д.

Считывание из блока 1 оператив- 0 ной памяти осуществляется по низко- I fy логическому уровню сигнала управ- лекия записью/считыванием, поступающему с первого выхода пересчетного блока 6, запись - по высокому логи- ческому уровню,

В режиме считывания умножитель 14 комплексных чисел производит умн ожение первых г операндов, извлекаемых из блока 1 оперативной памяти

на множители, извлекаемые из блока 2 постоянной памяти, полученные произведения заносятся в узел буферной памяти арифметического блока 3.

В режиме записи арифметический блок производит элементарные преобразования, над полученными ранее произведениями и заносит в блок 1 оперативной памяти на место ранее извлеченных операндов новые операнды согласно алгоритму замещения.

Экспоненциальные множители храняся в блоке 2 постоянной памяти (отдельно синусы и косинусы), причем область памяти, в которой хранятся множители для выбранного г определяется управляющим входом блока 2 постоянной памяти, комплексные операнды хранятся в блоке I оперативной памяти отдельно как значения их действительной и мнимой частей. Регистр 13 хранения обнуляется переходом синала записи/считывания из низкого логического уровня в высокий.

После записи в блок 1 оперативной памяти первых г новых операндов производится считывание очередных г операндов и занесение в арифметический блок 3 г произведений операндов на соответствующие им экспоненциальные множители, извлекаемые из блока 2 постоянной памяти, после чего в арифметическом блоке 3 производятся элементарные преобразования и в блок 1 оперативной памяти заносятся очередные г новых операндов на место ранее извлеченных.

После окончания первой итерации сигналом переноса старшего разряда пересчетного блока 6 в первом регистре 5 сдвига происходит сдвиг информации в сторону старших разрядов с занесением 1 в младший разряд, содержимое счетчика 7 итераций увеличивается на единицу и устройство переходит к выполнению следующей итерации преобразования.

При реализации быстрого преобразования в базисе ВКФ на входах XI, Х2 и Х4 устройства установлен код 000, Исходный массив длиной N занесен в блок 1 оперативной памяти в прямом порядке. Таким образом, при выполнении преобразования в базисе ВКФ работа устройства отличается от работы при выполнении преобразования в базисе ДЭФ только порядком расположения исходной информации в блоке 1

оперативной ппмяти, отсутствием операции умножения на экспоненциальные множители в режиме считывания и работой первого.регистра 5 сдвига. В данном случае в исходном состоянии- разряды первого регистра 5 сдвига устанавливаются в состояние логической 1, причем в старший разряд регистра по приходу тактового импулсса на

тактовый вход осуществляется запись нулевой информации со сдвигом ранее записанной информации в сторону г-шадших разрядов.

При реализации быстрого преобразования в базисе УВКФ на входах Х1, Х2 и Х4 устройства установлен код 010. Исходный массив длинной N занесен в блок 1 оперативной памяти в прямом порядке. При выполнении преобразования в базисе УВКФ работа устройства отличается от работы устройства при выполнении преобразования в базисе ВКФ тем, что количество выполняемых элементарных преобразований уменьшается с увеличением номера итерации. Это осуществляется следующим образом. Двоичный код с выхода счетчика 7 итераций ч-ерез группу И 9 элементов (на вход Х2 подана логическая

1) поступает на управляющий вход коммутатора 8, В результате на первой итерации к тактовым входам первого регистра 5 сдвига и счетчика 7 итераций подключен выход переноса

элементарной ячейки старшего разряда пересчетного блока 6,

На последуюш 1х итерациях номер разряда пересчетного блока 6, чей выход переноса коммутатором 8 подключается к тактовым выходам первого 4)егистра 5 сдвига и счетчика 7 итераций, уменьшается на единицу от итерации к итерации.

Арифметический блок 3 (фиг. 2)

предназначен для вьтолнения элементарного дискретного преобразования, которое заключается в умножении матрицы столбца из г элементов на квадратную матрицу Е,. элементарного преобразования по модулю г:

5

Е

w; w; w; w;

w w,

w; w:

w:

w;

wr

i,t-Cr-iVi/

w:

w

jlr-lWoJr

it-1|fr-l)lMjr

W, I

2

где W exp(-j r )

- Арифметический блок 3 работает следующим образом.

В исходном состоянии первый 18 и второй 19 узлы пересчета, накапливающий сумматор I7 комплексных чисел и триггер 26 обнулены. По входу кода основания системы счисления арифметического блока (Х9) задается двоичный код числа г, по которому устанавливается режим счета узлам 18 и 19 пересчета и выбирается область памяти узла 20 постоянной памяти, в которой хранятся экспоненциальные коэффициенты для элементарного преобразования (отдельно синусы и косинусы для выбранного г) ,

По низкому логическому уровню сигнала записи/считывания, поступающему по входу арифметического блока 3 (Х6), в узел 15 буферной памяти по адресу с выхода первого узла 18 пересчета записываются с выхрда умножителя 14 комплексных чисел первые г произведений операндов, извлеченных из блока оперативной памяти, и соответствующих им экспоненциальных множителей, извлеченных из блока 2 постоянной памяти. При низком логическом уровне сигнала записи/считывания на тактовый вход первого узла 18 пересчета по первому тактовому входу Х7 через второй элемент И 23 и элемент ИЛИ 24 подаются тактовые импульсы с второго выхода генератора 10 синхроимпульсов, В этом случае адресация узла 15 буферной памяти производится в такт адресации блока 1 оперативнор памяти.

При переходе устройства в режим записи в арифметический блок по вхо ду Х6 на управляющий вход узла 15 буферной памяти подается высокий логический уровень, в результате чего узел 5 буферной памяти переходит в режим считывания. Этим же Зфовнем открывается первый элемент И 21, через который на вход формирователя 25 ,1злительности импульсов г.1Одаются тактовые импульсы по входу Х7 с второго выхода генератора 0 синхроимпульсов, Ня выходе триггера 26 по заднему фронту первого же короткого импульса с выхода фор1 шрова теля 25 формируется высокий логический уровень, разрешаю|ций прохождение на тактовшй вход первого узла

18пересчета по raTOpobfy входу синх- роиизагдаи Х8 арифметического блока

5 через третий элемент И 22 и элемент ИЛИ 24 тактовых импульсов с первого выхода генератора 10 синхроимпульсов, I

По первому тактовому импульсу

10 первый узел 3 пересчета формирует код адреса сом{ожителей первого произведения, хранящегося в узлах 20 постоянной памяти и 15 буферной памяти. Оба комплексных числа пере)5 множаются в умножителе 16 комплексных чисел арифметического блока. Полученное произведение сумтмируется в накапливающем сумматоре комплекс- чисел с ранее накопленной инфор20 мадией (на первом такте с нулевой информацией),

Эта процедура повторяется г раз, после чего накопленная в накапливающем сумматоре 17 комплексных чисел

25 информация по выходу У2 записывается в блок 1 оперативной памяти на место ранее извлеченного первого операнда, сигнал переноса с второго выхода первого узла 8 пересчета обнуляет на30 капливающий сумматор i 7 комплексных чисел и приращивает на единицу содер- лсимоё узла 19 пересчета, Арифмети- блок переходит к вычислению следующего нового операнда для блока

35 3 оперативной памяти.

После вычисления и занесения в блок 1 оперативной памяти г операндов по сигналу переноса второго узла

19пересчета, поступающему на такто- 40 вый вход триггера 26р в триггер запи

сьпзается нулевая информация, в результате чего арифметический блок подготавливается к приему новых г произведений и ви -гиспению очередных 45 операндов для (5.тюкс; оперативной памяти ,

Формула изобретения

50Устройство д51Я -рсзлизации быстрых

преобразований в базисах дискретных ортогональных функций, содержащее блок оперативной памяти, блок постоянной памяти, группу коммутаторовц

первый и второй регистры сдвига, счетчик итерагши, коммутатор, группу элементов И, генератор синхроим - nyjibcoB, причем группа адресных входов блока оперативной памяти соединена с выходами коммутаторов группы, к управляющим входам которых подключен информационный выход первого регистра сдвига, тактовый вход которого соединен со счетным входом счетчика итераций и с выходом коммутатора, группа управляющих входов коммутатора подключена к выходам элемен- тов И группы, первые входы которых соединены с информационными выходами счетчика итераций, вторые входы элементов И группы объединены и являются первым входом задании режима устройства, вход кода сдвига первого регистра сдвига подключен к второму входу задания режима устройства, входы кода сдвига второго регистра сдвига подключены к выходу регистра итераций, отличающе еся тем, что, с целью расширения функциональных возможностей устройства за счет вычисления быстрых преобразований в базисах дискретных ортогональных функций по произвольному основанию, в него введены сумматор, регистр хранения, умножитель комплексных чисел, пересчетный блок, арифметический блок, который содержит узел буферной памяти, умножитель комплексных чисел, накапливающий сумматор комплексных чисел, первый и второй узлы пересчета, узел постоянной памяти, первый, второй и третий элементы И, элемент ИЛИ, формирователь длительности импульсов, триггер, причем информационный вход узла буферной памяти соединен с выходом умножителя комплексных чисел, выход узла буферной памяти соединен с первым входом умножителя комплексных чисел арифметического блока, второй вход умножителя комплексных чисел арифметического блока соединен с выходом узла постоянной памяти.

первая группа адресных входов которо- 45 формациоНные выходы пересчетного го соединена с входами коэффициента блока подключаются к информационным

входам коммутаторов группы и второго регистра сдвига, выходы переноса пепересчета первого и второго узлов пересчета и подключена к входам за- Дания основания системы счисления устройства, первый вход первого эле- 50 формационкым входам коммутатора, .мента И соединен с входом записи/счи- входы коэффициента пересчета перересчетного блока подключаются к интывания узла буферной памяти, с инверсным входом второго элемента И и подключен к первому выходу пересчетного блока, выходы второго и третьего элементов И соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен со счетным входом первого

О

0

узла пересчета и с входом сиихрони- накапливающего сумматора комп- шексных чисел, выход переполнения первого узла пересчета подключен к входу обнуления накапливающего сумматора комплексных чисел и счетному, входу второго узла пересчета, выход переполнения которого соединен с входом синхронизации триггера, выход триггера подключен к первому входу третьего элемента И, второй вход которого подключен к первому выходу генератора синхроимпульсов, второй вход -первого и прямой вход второго

5 элементов И подключены к втopo y выходу генератора синхроимпульсов, выход первого элемента И подключен к входу форг-шрователя длительности импульсов, выход которого соединен с входом установки в 1 триггера, Информационный вход триггера подключен к входу нулевого потенциала устройства, информационные выходы первого узла пересчета подключены к адресным входам узла буферной памяти и к второй группе адресных входов узла постоянной памяти, информационные выходы второго узла пересчета соединены с третьей группой адресных входов узла постоянной памяти, выход умножителя комплексных чисел арифметического блока соединен с информационным входом накапливающего сумматора комплексных чисел, выход которо5 го подключен к информационному входу блока оперативной памяти и к выходу устройства, вход синхронизации регистра хранения и счетный вход пересчетного блока подключены к второму выходу генератора синхроимпульсов, вход обнуления регистра хранения и вход записи/считывания блока оперативной памяти подключены к управляющему входу пересчетного блока, ин5

0

0

формационкым входам коммутатора, входы коэффициента пересчета перересчетного блока подключаются к инсчетного блока, входы основания системы счисления сумматора и первая группа адресных входов блока посто- НИНОЙ памяти подключены к входам задания основания системы счисления устройства, вторая группа адресных входов блока постоянной памяти и входы первого слагаемого сумматора сое13129

динены с выходами регистра хранеггия. информационный вход которого подключен к выходу сумматора, вход второг о слагаемого которого соединен с выходом второго сдвига, управ- дяющий вход умножителя комплексных чисел является третьим входом задания режима устройства, причем пересчетный блок содержит счетный триггер и п пересчетных узлов, каждый из которых содержит счетчик, группу сумматоров по модулю два, элемент И1Ш,, причем информационный выход является информационным выходом пе-- ресчетного узла, первые входы сумматоров по модулю два группы подключены к информационным выходам счетчика, входы коэффициента пересчета пересчетного узла подключень к вторым входам сумматоров по модулю два группы, выходы которых подключены к входам элемента ИЛИ, инверсный выход которого соединен с .входом обнуления счетчика и с выходом переноса переи

/IV

1

Z

5 1А

счетного узла, счетный вход счетчика является счетным входом пересчетного узла, счетный вход первого пересчетного узла сое.динен со счетным

входом пересчетного блока, выход переноса первого пересчетного узла подключен к входу счетного триггера, выход которого соединен с управляющим выходом пересчетного блока и со счетным входом второго пересчетного узлар выходы переноса пересчетных узлов, начиная с второго, соединены соответственно с выходами переносов пересчетного блока, причем выход переноса i-ro пересчетного узла () соединен со счетным входом (i+l)-ro пересчетного узла, информационные выходы всех пересчетных узлов являются информационными выходами пересчетного блока, входы коэффициентов пересчета всех пересчетных узлов подключены к входам коэффициента пересчета пересчетного блока .

/V

4N ж ж

У/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований | 1986 |

|

SU1416981A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Устройство для реализации быстрого преобразования Фурье последовательности с нулевыми элементами | 1983 |

|

SU1119025A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

) Изобретение относится к области вычислительной техники и может быть использовано при решении задач фильтрации и идентификации сигналов. Целью изобретения является расширение функциональных возможностей устройства за счет вычисления быстрых преобразований в базисах дискретных ортогональных функций по произвольноNiy основанию. По сравнению с прототипом в предлагаемом устройстве дополнительно реализуются преобразования в часто используемых базисах функций Виленкина-Крестенсона (ВКФ), усеченных функций Виленкина-Крестенсона (УВКФ). Устройство содержит блок оперативной памяти, блок постоянной памяти, арифметический блок, блок коммутаторов, первый регистр сдвига, пересчетный блок, счетчик итераций, коммутатор, группу элементов И, генератор синхроимпульсов, регистр сдвига, введены; сумматор, регистр хранения, умножитель комплексных чисел и вход задания кода основания преобразования. Применение предлагаемого устройства позволяет оптимально подобрать длину входной выборки за счет изменения основания преобразования при обра- |ботке сигналов, а также приводит к расширению реализуемых ортогональ- йых преобразований, используемых при идентификации и определении характеристик сигналов. 5 ил. 13 сл

V

П

t

7R Ж

/J

х/

//

/

Х2

хз

т

И

т

(и. г.Ц

Фи2 5

| Устройство для вычисления коэффициентов обобщенных дискретных функций | 1978 |

|

SU752347A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-23—Публикация

1985-03-29—Подача