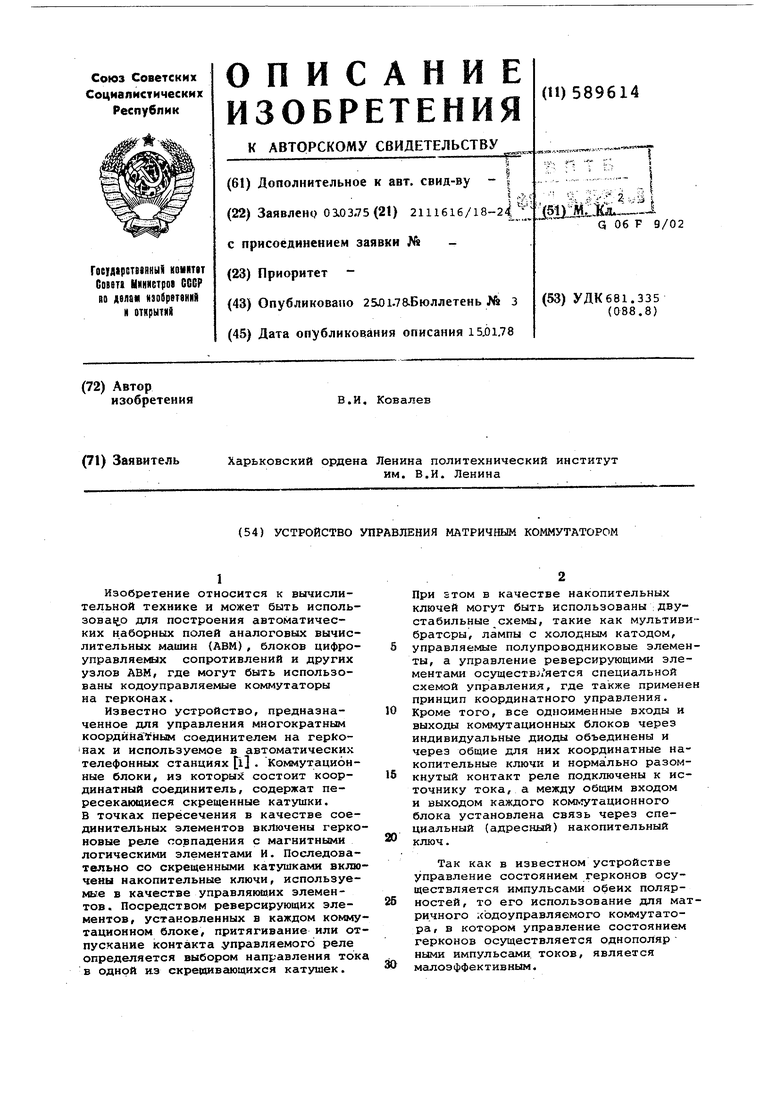

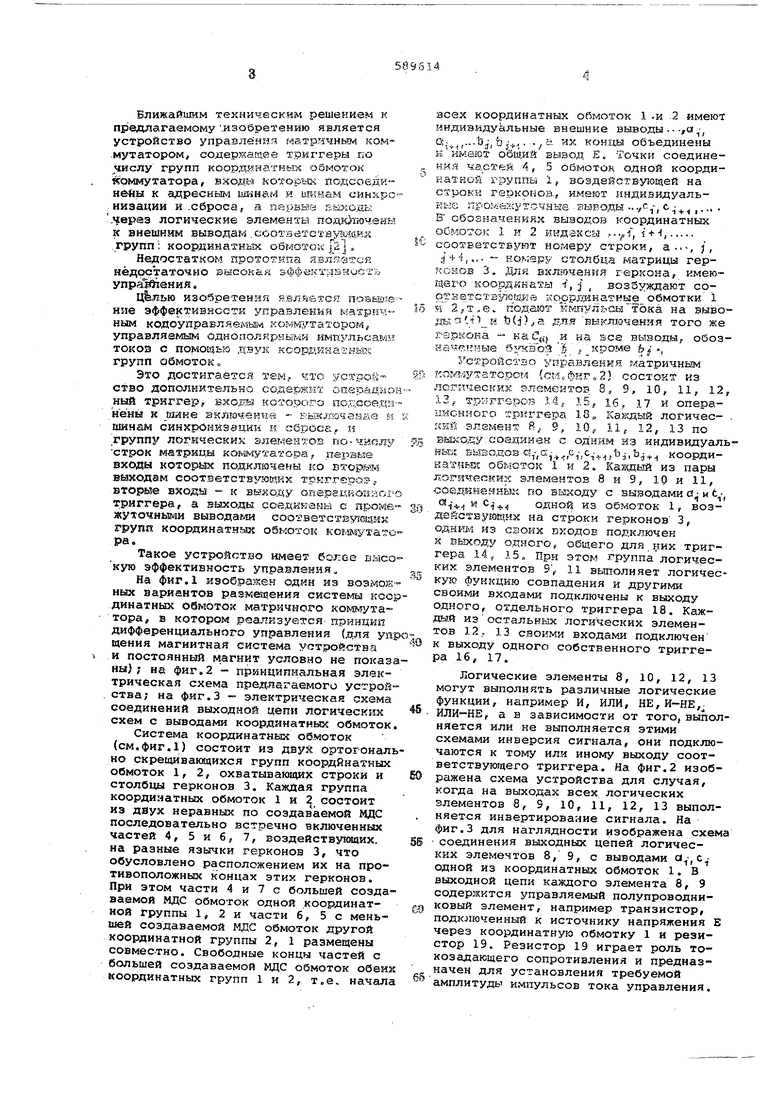

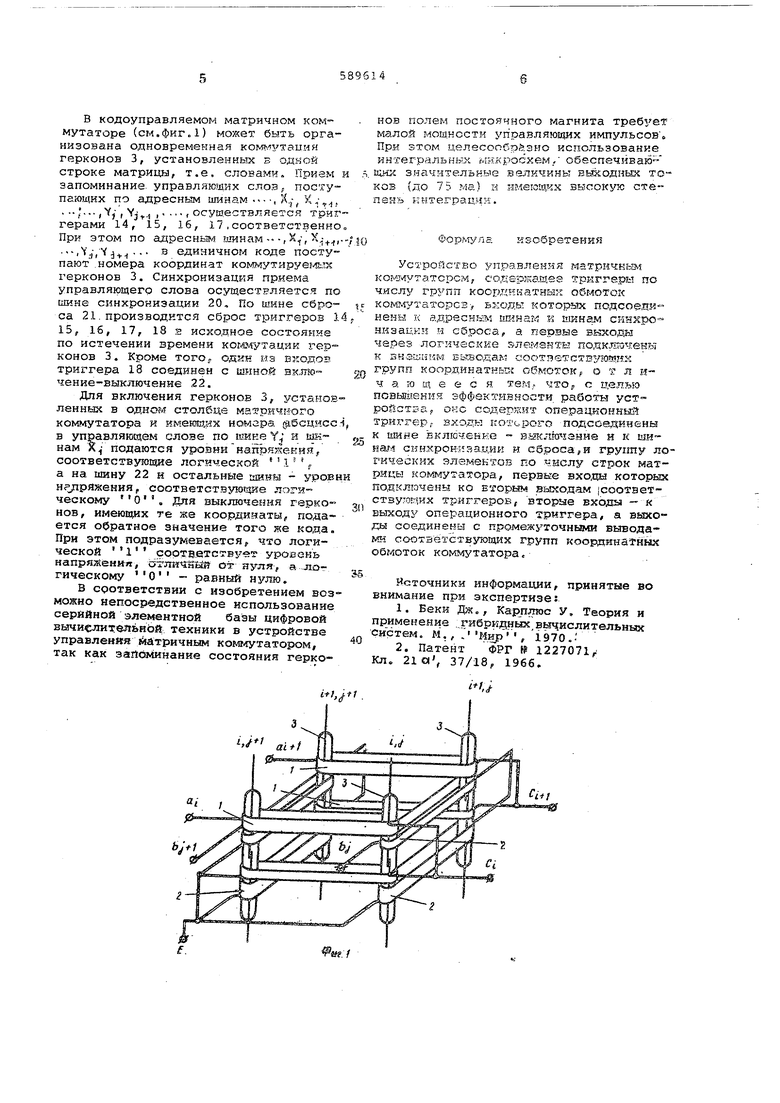

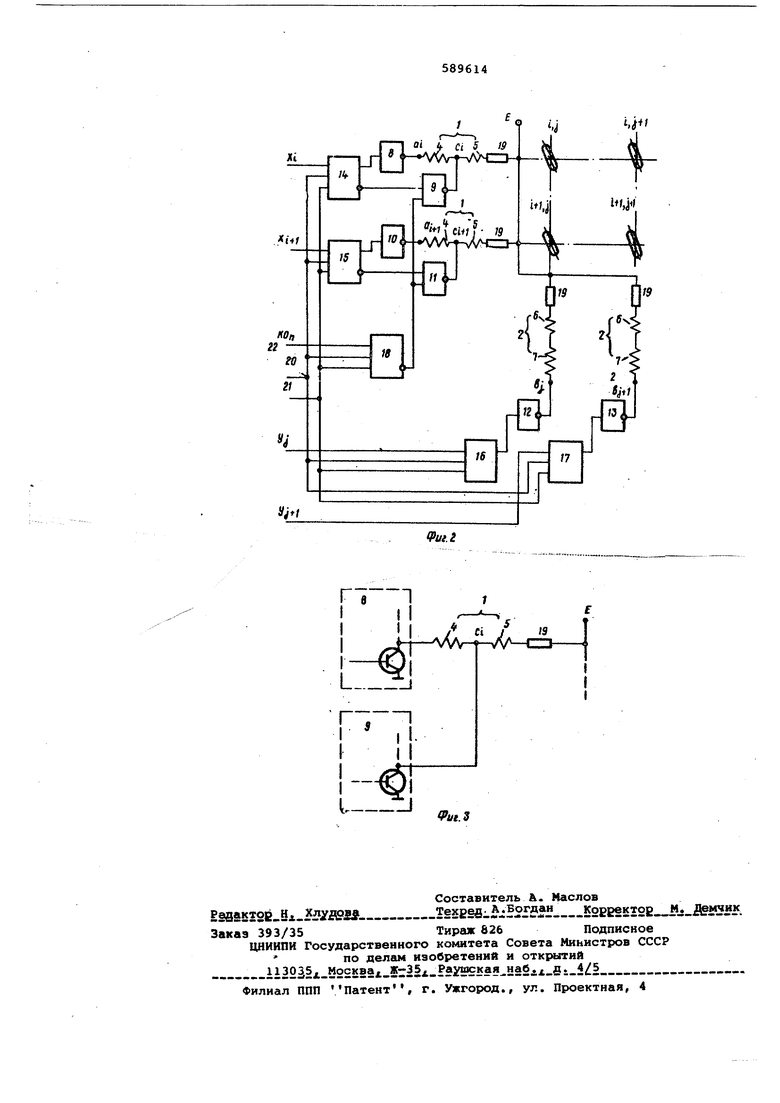

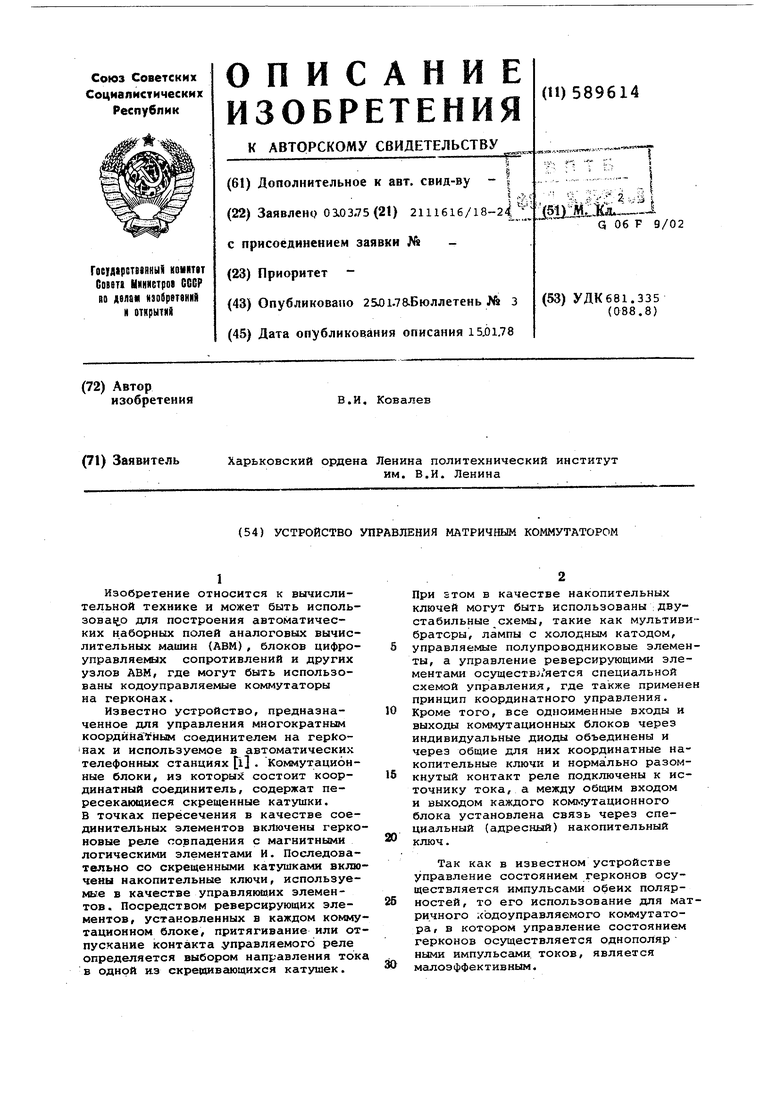

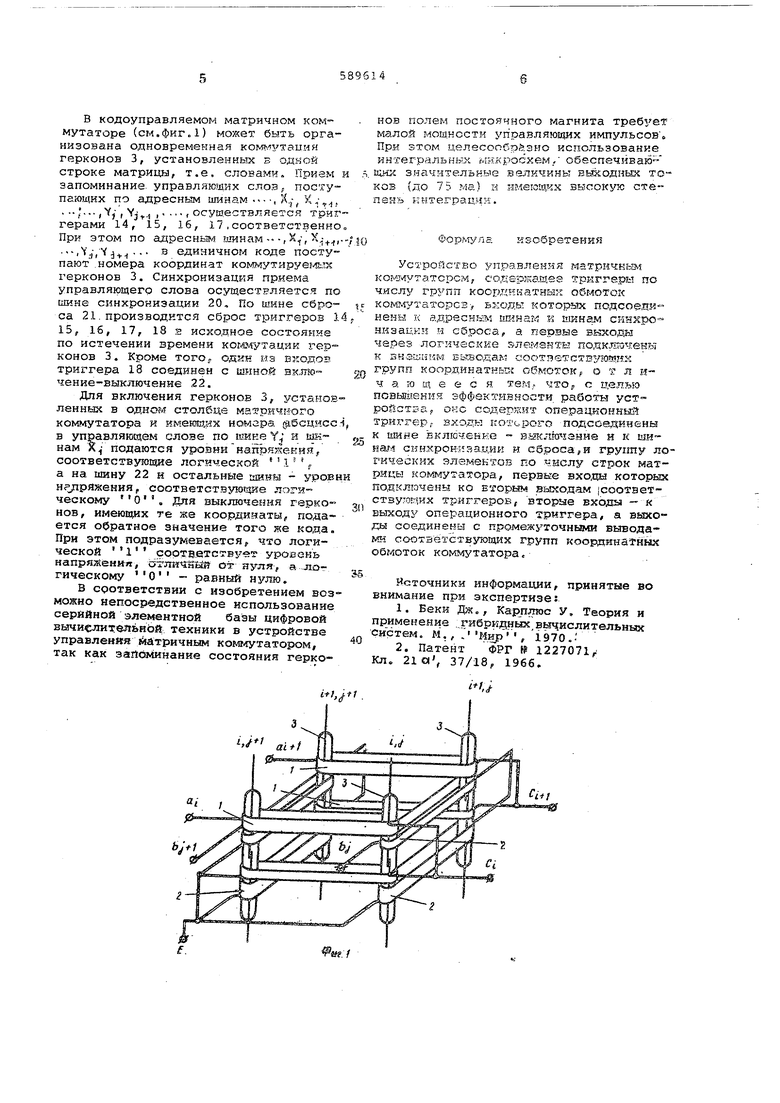

(54) УСТРОЙСТВО УПРАВЛЕНИЯ МАТРИЧНЫМ КОММУТАТОРОМ Ближайцим техническим решением к предлагаемому .изобретению является устройство управления матр.ччным ком.мутатором, содержатее триггеры по числу групп координатные обмоток Коммутатора, входы которых пс-дсоедин&йы к адресным шинам и цшаам синхрс. низации и .сброса, а первые .г ..чераэ логические элементы подк)1ючены к внешним вывoдa s .соответсгв).ищ.кх групп; координатных обмоток 2, Недостатком прототипа явлпс-згск недостаточно высокая зФФектьшносгь упра йения. цЬлью изобретения является повьш-а ние эФфектквисстк управления матричным кодоуправляемш комк татором, управляемым однополкрными импульсами TOKOS с помощью лэук ксордикагйьв групп обмоток о Это достигается тем,, что устрой-ство дополнительно содержит операдко ный триггерf входь которого псдсоеди нены к ймке включение - къшкк)че.па.® и шинам синхронизацин и сброса а группу логически.к элементов гю-чиолу строк матрицы коь мутатора,, первые входы которых подключены ко вторагм выходам соответствующих триггеров ,вторые входы - к вцходу ог5ерадйоай01 триггере, а выходы соедккана с проУгв жуточными выводами соответствутйдях групп координатнак обмоток ког мух&уо Такое устройство имеет более высо кую эффективность управления. На фиг.1 изображен один из SOSMOJK Hfcjx вариантов размещения системы коо динатных обмоток матричного комьуута тора, в котором реализуется-принцип дифференциального управления (для уп щения магнитная система устройства и ПОСТОЯННЕЙ магнкт условно не показ ны); на фиг.2 - принципиальная электрическая схема предлагаемого устрой ства; на фиг.З - электрическая схема соединений выходной цепи логических схем с выводами координатных обмоток Система координатных об.моток (см.фиг.1) состоит из двух ортогонал но скрещивающихся групп координатных обмоток 1, 2, охватывающих строки и столбцы герконов 3. Каждая группа координатных обмоток 1 и состоит из даух неравных по создаваемой МДС последовательно встречно включенных частей 4, 5 и 6, 7, воздействующих. на разные язычки герконов 3, что обусловлено расположением их на противоположных концах этих герконов. При этом части 4 и 7 с большей созда ваемой МДС обмоток одной координатной группы If 2 к части б, 5 с меньшей создаваемой ВДС обмоток другой координатной группы 2, 1 размещены совместно. Свободные концы частей с большей создаваемой МДС обмоток обеи координатных групп 1 и 2, т.е. начал всех координатных обмоток 1 -и 2 имеют индивидуальные внешние выводы /а -, а.- , ii / кони:ы объединены к имеют обгя.ий вывод Е Точки соединения частей 4, 5 обмоток одной координатной группьз 1, воэдэй-ствующей на строки герконов., имеют индивидуальЕке лром& :-;ут- чньге выводы , с- .. ,. - В обозначениях выводо.8 координатных обмоток 1 и 2 икдаксы ,.1, i + -, соотЕетстБуют строки, а-.-, j, .j-H,,.- - Ho.;-spy столбца матрицы герконов 3. Для включения геркона, имеющего координаты 1,j , возбуждают соотвйтствуюшлв ксюрдвнаткые обмотки 1 SJ 2,jT,ew пода т кмпульеьз тЬка на вывоЯЬ1аи)к 1(з)а Д.ПЯ выключения того же геркока - ка. и на все выводы, обозлвч.кккые S I кроме Ь , стройсгзо ynpaBJieHSSH рлатричннм когФзутатс.рсм (сМсфкг.2) состокт из логических элементов 8, 9, 10, 11, 12, 13 f триггеров .1-4., 15 f 16, 17 и операцисниого триггера 18 Какодый логичес- . ккй элемент К 9, 10, 11, 12, 13 по ВЁ&оду соединен с одним из индивидуальешг ВКВО..ЦОВ ,G,c,-,c.,-,.ft3-,b.,. координаачдшг обг.юток i и 2, Какгдый из пары логичйских злемантов 8 и 9, 10 и 11, -соединенный; по выходу с выводами б и , и с,-. одной из обмо-ток 1, воздействующих на строки герконов 3, одншл из своих входов подключен к внходу одногоf общего для них триггера 14, 15, При этом группа логических элементов S, 11 вьшолняет логическую функцию совпадения и другими своими входами подключены к выходу одного, отдельного триггера 18. Кажды-й из остальных логических элементов 12. 13 СВ055МИ входамл подключен к выходу одного собственного триггера 16, 17. Логические элементы 8, 10, 12, 13 могут выполнять различные логические функции, например И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, а в зависимости от того, выполняется или не выполняется этими схемами инверсия сигнала, они подключаются к тому или иному выходу соответствующего триггера. На фиг.2 изобргшена схема устройства для случая, когда на выходах всех логических элементов 8, S, 10, 11, 12, 13 выполняется инвертирование сигнала. На фиг.З для наглядности изображена схема соединения выходных цепей логических элементов 8, 9, с выводами 01-{, одной из координатных обмоток 1. В выходной цепи каждого элемента 8, 9 содержится управляемый полупроводниковый элемент, например транзистор, подключенный к источнику напряжения Е через координатную обмотку 1 и резистор 19. Резистор 19 играет роль токозадающего сопротивления и предназначен для установления требуемой амплитудь импульсов тока управления. В кодоуправляемом матричном коммутаторе (см. фиг Л) мо7лет быть организована одновременная ком лутаиия герконов 3, установленных в одной строке матрицы, т.е. словами. Прием запоминание управляющих слов j поступающих по адресным шинам -, K.j, v, ...;... ,Yj, , осушествляется триг герами 14, 15, 16, 17.соответственно При этом по адресным гютнам--, , , в единичном коде поступают .номера координат KO « MyTHpyeiv bTs герконов 3. Синхронизация приема управляющего слова осущестЕЛяется по шине синхронизации 20, По шине сброса 21. производится сброс триггеров 1 15, 16, 17, 18 Е искодное состояние по истечении времени когвсутацик конов 3. Кроме того, один из вкодов триггера 18 соединен с шиной вк.гйочение-выключенне 22. Для включения герконов 3, установ ленных в одном столбце мзтричЕ ого коммутатора и номзра в управляющем слове по шине и шк нам Х подаются уровни напЬя.5кенйя, соответствующие логической .1 - f а на шину 22 и остальные гаины уровн нрдряжения, соответствуюйще логиДля выключения герко ческому нов, имеющих те же координаты, подается обратное значение того же кода, При этом подразумеваетсяf что логической Ч соответствует уровень напряжения, сгглйЧ:Ш:а от нуля, а лог гическому О - равный нулю. В сротэетствии с изобретением воз можно непосредственное использование серийной элементной базы цифровой вычислительной техники в устройстве управления матричным ком-гутатором, так как запоминание состояния герко НОВ полем постоячного магнита требует малой мощности управляющих импульсов . При этом целесопбр&.зно использование интегральных « ккросхем, обеспечиваю тих з.начительные величины выходных токов (до 75 ма) и HMeioELHX высокую степень кнтеграц.цк. Формула изобретения УстротЛство уп.равления мзтричкьэког« ута.торсм, содаржащее триггеры по числу групп координатных обмоток комг.утаторсЗ, ькоды которах подсоея йены к адресным шгнам к шинам синхро™ нкзацин .и сброса, а первые выходы через логические подклаченьт к Бнзщнмм Еьшодак аос тветстЕуюй НХ групп коор.динатньш обмоток о т л и чающееся тем, что с целью повшиения эффективности работы уст ройстза, онс сод€;р5кит операционный триггер,, зхо.дк KOTGporvO подсоединены к шине включение - Вцклгочзние я к шинам снн.хрон-иза.дии и сбросами группу логических элементов по «:нслу строк матрицы комглутатора, первые входы которых подключены ко вторым выходам jcooTBeTству.),их триггеров, вторые входы - к выходу операционного триггера, а выходы соединены с промежуточными выводами соответствующих групп координатных обмоток коммутатора, источники информации, принятые во внимание при экспертизе 1.Беки Дж., Карплгос У, Теория и применение . гибркдаых вычислительных Систем. М., . Мир , 1970 .2.Патент ФРГ № 1227071,: Кл, 210, 37/18, 1966.

Hi

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления матричным коммутатором | 1978 |

|

SU767762A1 |

| Устройство для управления матрич-НыМ КОММуТАТОРОМ | 1979 |

|

SU832719A1 |

| Матричное наборное поле | 1979 |

|

SU809214A1 |

| Координатный коммутатор | 1974 |

|

SU597095A2 |

| Матричное наборное поле | 1980 |

|

SU943749A2 |

| Матричное наборное поле | 1983 |

|

SU1128268A2 |

| Устройство умножения булевых матриц | 1980 |

|

SU959063A1 |

| Устройство для отображения информации | 1990 |

|

SU1737499A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

(

w.3

Авторы

Даты

1978-01-25—Публикация

1975-03-03—Подача