ройство, синтезированное на базе распределителя импульсов, выполненного либо на счетчике с дешифратором, либо сдвиговом регистре с элементами управления на логических элементах и триггерах, либо, как в предложенном устройстве, на логических элементах, триггерах и одновибраторах.

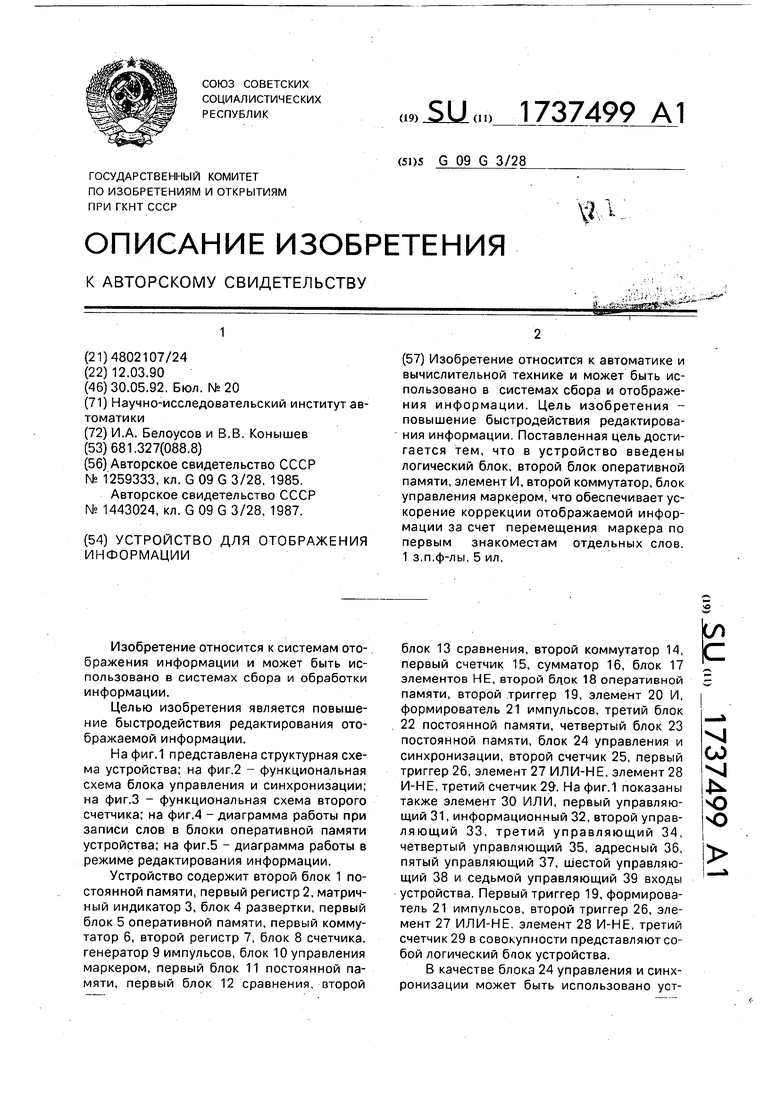

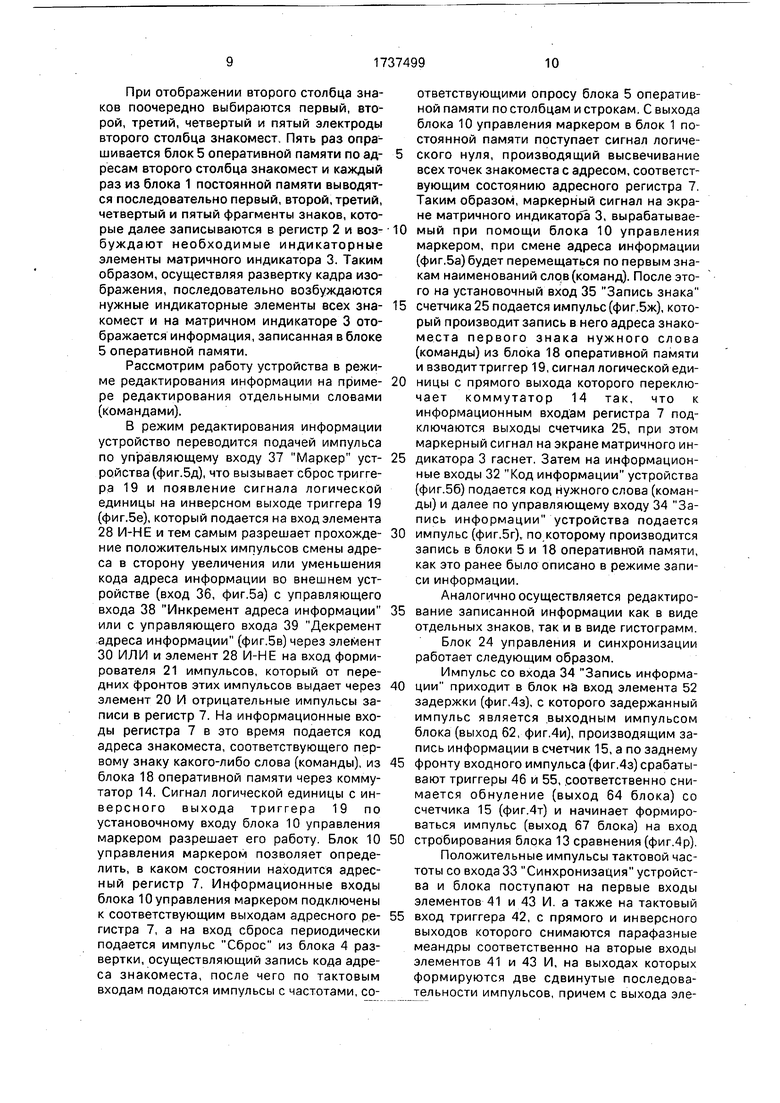

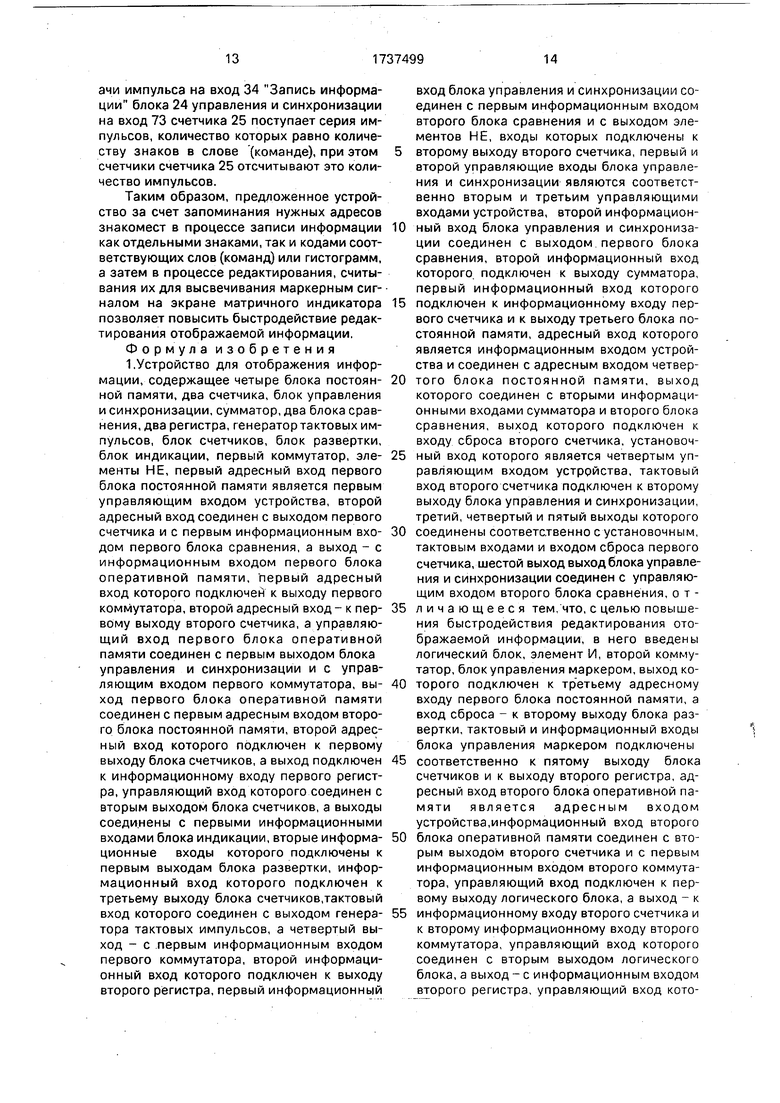

Блок 24 управления и синхронизации содержит элементы 40,48 и 49 НЕ, элементы 41,43 И, триггеры 42,46,54 и 55, элементы 44,45,47,50,51 и 56 И-НЕ, элемент 52 задержки, формирователь 53 импульсов,

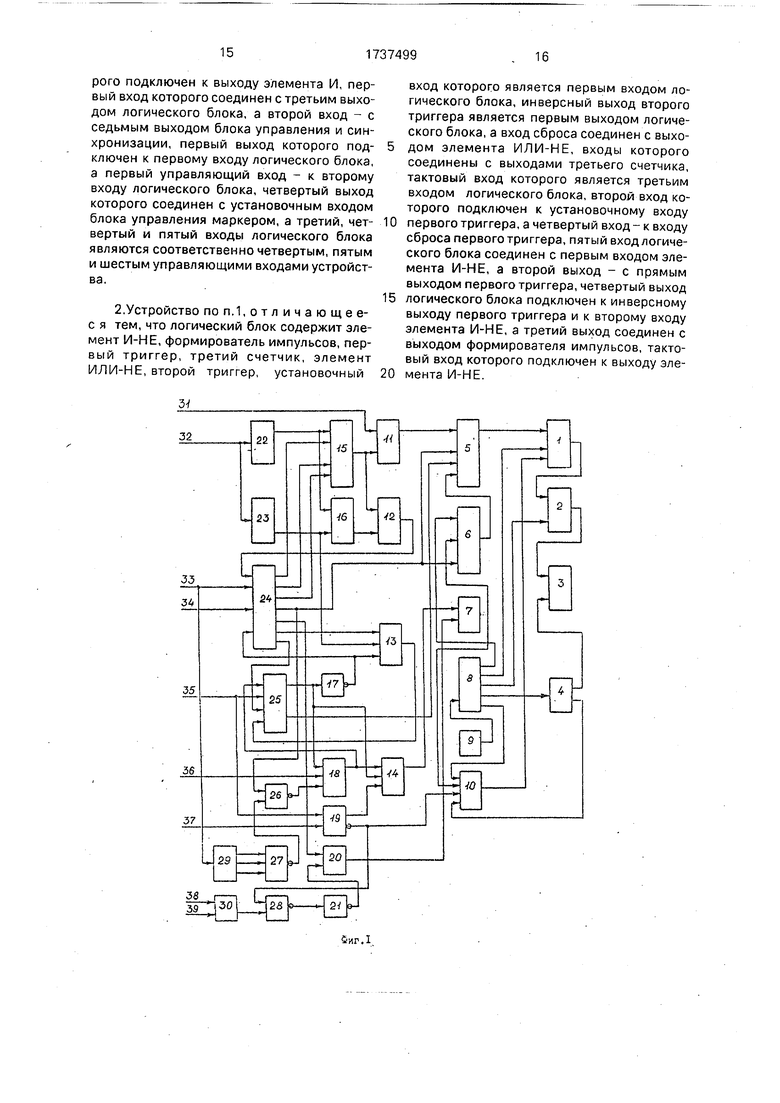

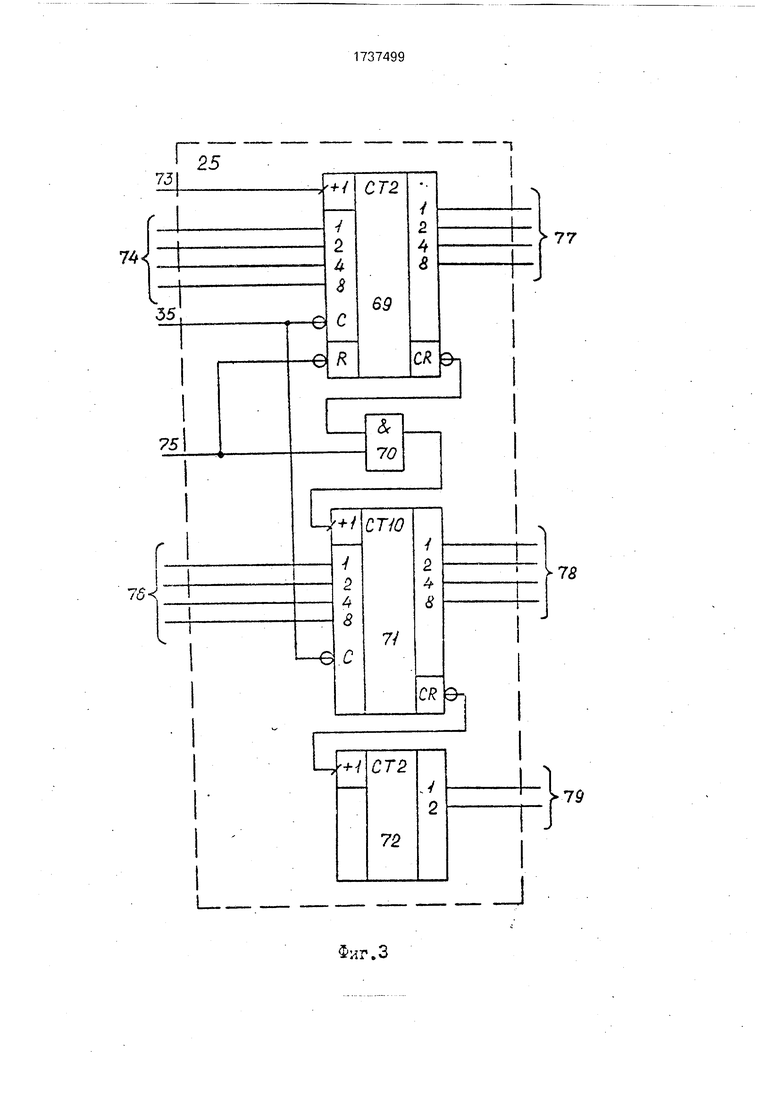

Счетчик 25 содержит двоичный счетчик 69 столбцов, элемент 70 И, двоично-десятичный счетчик 71 строк, двоичный счетчик 72 страниц, тактовый вход 73, информационные входы 74 и 76 счетчиков 69 и 71 столбцов и строк, установочный вход 35 счетчиков 69 и 71 столбцов и строк, вход сброса 75 счетчика 69 и перевода счетчика 71 в следующее состояние, выходы 77-79 счетчиков 69,71 и 72 сголоцов, строк и страниц.

Устройство имеет три режима работы: режим записи, при котором производится запись соответствующей информации в ячейки памяти блоков 5 и 18 оперативной памяти, режим отображения, когда производится периодическое считывание информации из ячеек памяти блока 5 оперативной памяти и в соответствии с ней отображение на экране матричного индикатора 3 знаков, слов (команд) или гистограмм и режим редактирования информации.

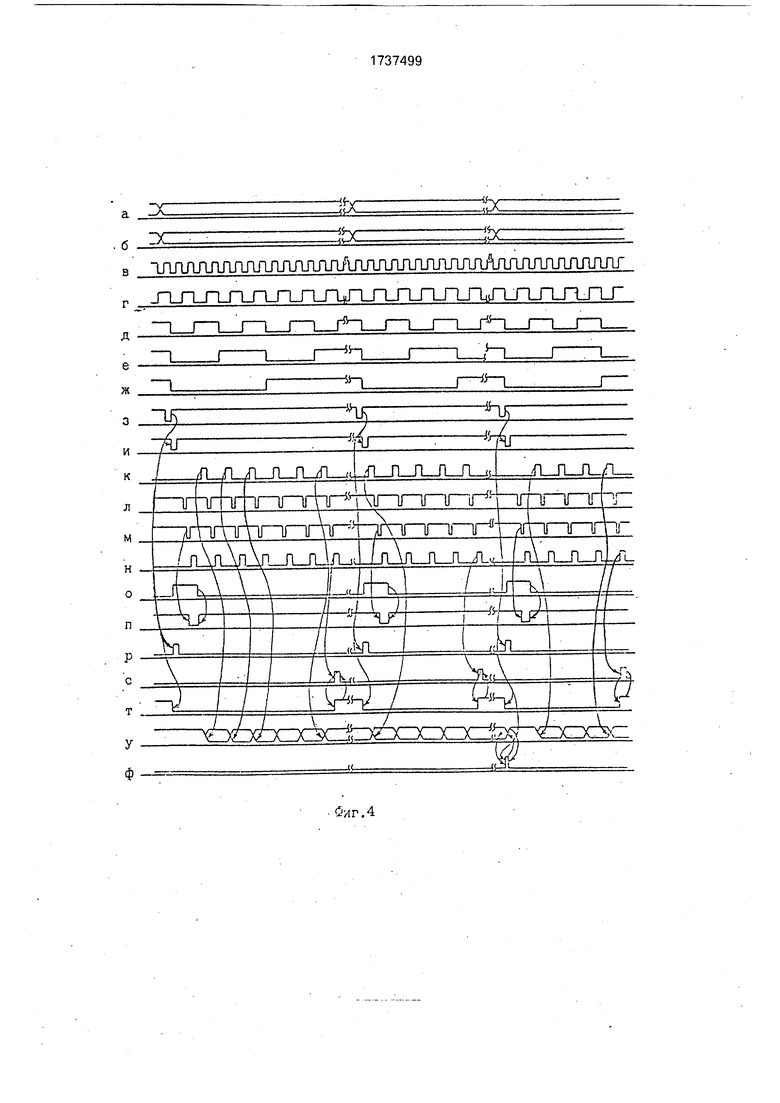

Рассмотрим работу устройства в режиме записи информации на примере записи слов (команд), предположив, что первое слово будет отображено в левом верхнем углу экрана индикатора, т.е. счетчик 25 - в нулевом состоянии. В этом режиме триггер 19 находится во взведенном состоянии и код адреса знакоместа матричного индикатора 3 поступает с выходов счетчика 25 через коммутатор 14 на информационные входы регистра 7.

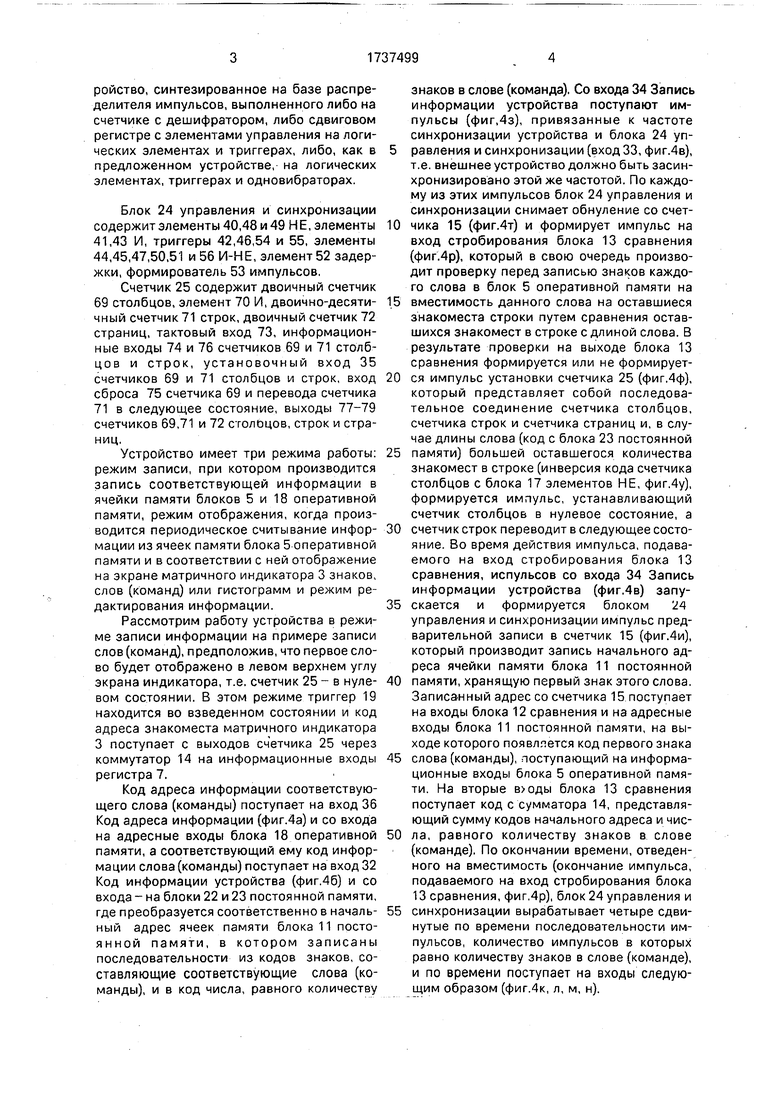

Код адреса информации соответствующего слова (команды) поступает на вход 36 Код адреса информации (фиг.4а) и со входа на адресные входы блока 18 оперативной памяти, а соответствующий ему код информации слова (команды) поступает на вход 32 Код информации устройства (фиг.4б) и со входа - на блоки 22 и 23 постоянной памяти, где преобразуется соответственно в начальный адрес ячеек памяти блока 11 постоянной памяти, в котором записаны последовательности из кодов знаков, составляющие соответствующие слова (команды), и в код числа, равного количеству

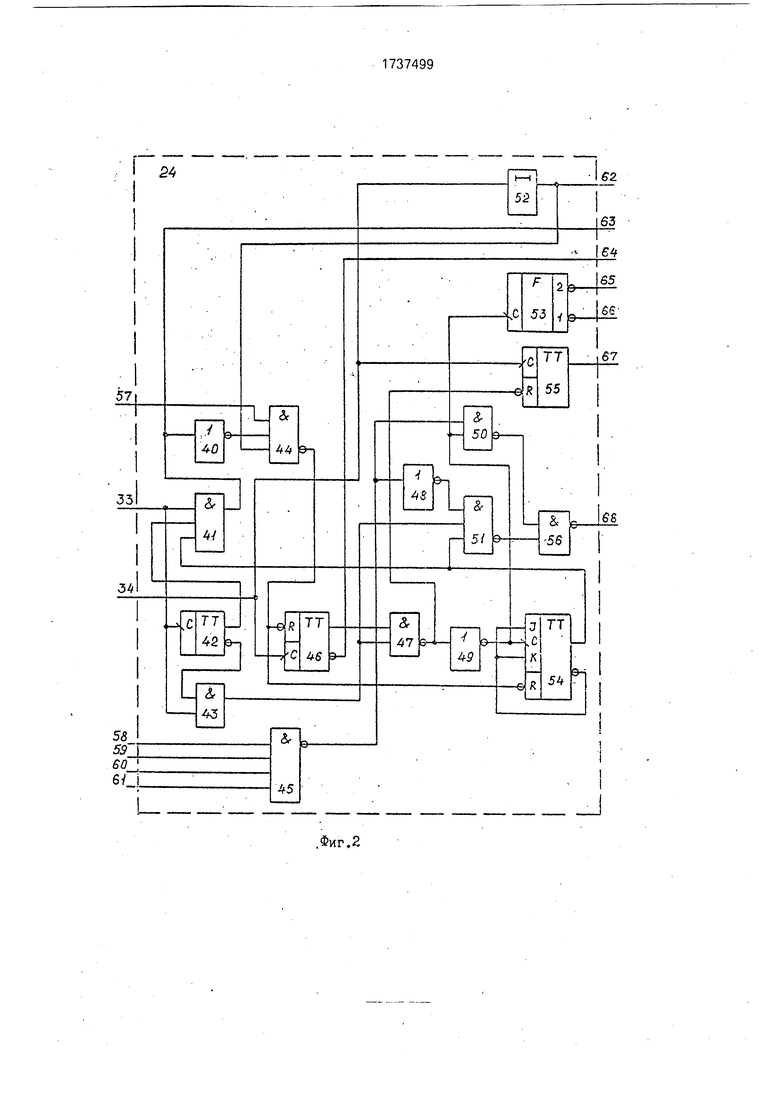

знаков в слове (команда). Со входа 34 Запись информации устройства поступают импульсы (фиг,4з), привязанные к частоте синхронизации устройства и блока 24 управления и синхронизации (вход 33, фиг.4в), т.е. внешнее устройство должно быть засин- хронизировано этой же частотой. По каждому из этих импульсов блок 24 управления и синхронизации снимает обнуление со счет0 чика 15 (фиг.4т) и формирует импульс на вход стробирования блока 13 сравнения (фиг.4р), который в свою очередь производит проверку перед записью знаков каждого слова в блок 5 оперативной памяти на

5 вместимость данного слова на оставшиеся знакоместа строки путем сравнения оставшихся знакомест в строке с длиной слова. В результате проверки на выходе блока 13 сравнения формируется или не формирует0 ся импульс установки счетчика 25 (фиг.4ф), который представляет собой последовательное соединение счетчика столбцов, счетчика строк и счетчика страниц и, в случае длины слова(код с блока 23 постоянной

5 памяти) большей оставшегося количества знакомест в строке (инверсия кода счетчика столбцов с блока 17 элементов НЕ, фиг.4у), формируется импульс, устанавливающий счетчик столбцов в нулевое состояние, а

0 счетчик строк переводит в следующее состояние. Во время действия импульса, подаваемого на вход стробирования блока 13 сравнения, испульсов со входа 34 Запись информации устройства (фиг.4в) запу5 скается и формируется блоком 24 управления и синхронизации импульс предварительной записи в счетчик 15 (фиг.4и), который производит запись начального адреса ячейки памяти блока 11 постоянной

0 памяти, хранящую первый знак этого слова. Записанный адрес со счетчика 15 поступает на входы блока 12 сравнения и на адресные входы блока 11 постоянной памяти, на выходе которого появляется код первого знака

5 слова (команды), поступающий на информационные входы блока 5 оперативной памяти. На вторые блока 13 сравнения поступает код с сумматора 14, представляющий сумму кодов начального адреса и чис0 ла, равного количеству знаков в слове (команде). По окончании времени, отведенного на вместимость (окончание импульса, подаваемого на вход стробирования блока 13 сравнения, фиг.4р), блок 24 управления и

5 синхронизации вырабатывает четыре сдвинутые по времени последовательности импульсов, количество импульсов в которых равно количеству знаков в слове (команде), и по времени поступает на входы следующим образом (фиг.4к, л, м, н).

Первым формируется и поступает импульс из последовательности, подаваемой на вход инкрементации счетчика 25(фиг.4к), причем в случае, когда слово (команда) должно отобразиться с начала строки, т.е. счет- чик столбцов находится в нулевом состоянии, то единицы с блока 17 элементов НЕ поступают на четвертые входы блока 24 управления и синхронизации, на п-вхо- довой элемент И-НЕ (л - количество разрядов счетчика столбцов), сигнал с выхода которого блокирует в этом случае первый импульс последовательности и он не поступает на вход инкрементации счетчика 25.

Вторым по времени формируется и поступает импульс из последовательности, подаваемой на вход записи информации регистра 7 (фиг.4л), по которому адрес, поступающий на информационные входы через коммутатор 14 со счетчика 25, переписывается в регистр 7.

Третьим формируется и поступает импульс из последовательности, подаваемой на вход коммутатора 6 и на вход записи информации блока 5 оперативной памяти (фиг.4м), по которому код первого знака слова (команды), поступающий на информационные входы блока 5 оперативной памяти с выхода блока 11 постоянной памяти, записывается в ячейку памяти по адресу, поступившему с регистра 7 через коммутатор 6, который коммутирует данный свой вход на выход на время действия импульса по входу управления.

Четвертым формируется и поступает импульс из последовательности, подаваемой на вход инкрементации счетчика 15 (фиг.4н), по которому счетчик переводится в следующее состояние, и на информационные входы блока 5 оперативной памяти поступит код второго знака слова (команды) из блока 11 постоянной памяти.

На этом заканчивается цикл записи в блок 5 оперативной памяти одного знака слова (команды), В дальнейшем циклы записи повторяются - формируется и поступает второй импульс из последовательности, подаваемой на тактовый вход счетчика 25, и т.д., формируется столько импульсов в каждой последовательности, сколько знаков в слове (команде) и с приходом последнего импульса из последовательности, подаваемой на тактовый вход счетчика 15, который переводится в следующее состояние, блок 12 сравнения вырабатывает импульс

(фиг.4с), по которому блок 24 управления и синхронизации начинает формировать импульс на вход обнуления счетчика 15 (фиг.4т). На этом заканчивается запись пер- вого слова (команды), которое отобразится в левом верхнем углу экрана, т.е. с начала первой строки.

На фиг.4 изображены диаграммы записи трех слов (команд): первое из семи знаков отображается с начала первой строки; второе из пяти знаков отображается за первым в первой стро ке; третье из пяти знаков не вмещается в первой строке, поэтому переносится и отображается с начала второй строки.

Запись в блок 18 оперативной памяти осуществляется следующим образом. На адресные входы поступает код адреса информационных ячеек внешнего устройства со входа 36 Код адреса информации (фиг.4а), а на информационные входы - коды адреса знакомест с выхода счетчика 25. Частота синхронизации устройства и блока 24 управления и синхронизации с входа 33 Синхронизация устройства (фиг.4в) поступает на вход инкрементации счетчика 29, частотные последовательности с выходов второго, третьего и четвертого разрядов

которого (выход первого разряда не используется, фиг.4г, д, е, ж) поступают на входы элемента 27 ИЛИ-НЕ, сигнал на выходе которого осуществляет обнуление или снятие обнуления триггера 26 (фиг.4о).

Триггер 26 срабатывает по входу от импульса записи информации первого знака слова (команды) с соответствующего выхода блока 24 управления и синхронизации (фиг.4м) во время снятия обнуления на входе (фиг.4о). В результате этого на инверсном выходе триггера 26 формируется импульс записи информации в блок 18 оперативной памяти (фиг.4п).

При записи в блоки 5 и 18 оперативной

памяти отдельных знаков и гистограмм устройство работает аналогичным образом, как и при записи слов (команд) с учетом следующего.

При записи отдельных знаков, как и

слов, на управляющий вход 31 Выбор способа записи устройства подается сигнал логического нуля, а при записи гистограмм - логической единицы, чем достигается переключение областей памяти блока 11 постоянной памяти, в которых записана .информация о знаках и словах (командах) в одной области и о гистограммах в другой.

При записи отдельных знаков для кодов, соответствующих этим знакам в блоке 23 постоянной памяти, занесен код единицы, что соответствует количеству знаков (слово из одного знака).

При записи гистограмм для всех 100 значений входной величины, возможных к отображению (00-99) на экране индикатора, в блоке 23 постоянной памяти занесен код пятнадцати с целью, чтобы каждое новое значение входной величины, какое бы мало оно не было, отображалось с новой строки. На экране индикатора десятки отображаются забитием необходимого числа знакомест в строке, например буквой ж, равного количеству десятков входной величины, а в следующих знакоместах строки отображаются цифры, первая из которых соответствует десяткам, т.е. количеству забитых знакомест, а вторая отображает и соответствует единицам входной величины. Оставшиеся свободные знакоместа строки заполняются пробелами. Такое отображение, забитое полем знакомест, придает удобство зрительного восприятия общего изменения входной величины, а цифры обеспечивают удобство считывания конкретных значений этой величины.

В блоке 11 постоянной памяти в области памяти, отведенной под гистограммы, занесены последовательности из кодов знаков забития, цифр и пробелов, составляющих совокупность всех 100 значений входной величины.

В режиме отображения информации на входе управления коммутатора 6 блоком 24 управления и синхронизации поддерживается уровень логической единицы, что определяет прохождение адресных сигналов с выхода блока 8 счетчиков через коммутатор 6 на адресные входы блока 5 оперативной памяти.

Генератор 9 запускает блок 8 счетчиков, который синхронизирует работу устройства в режиме отображения. Цифровой код с третьих выходов блока 8 счетчиков поступает на блок 4 развертки, который в определенной последовательности переключает электроды развертки матричного индикатора 3. Адрес с пятых выходов блока 8 счетчиков, поступая через коммутатор 6 на адресные входы блока 5 оперативной памяти, выводит из него цифровой код знака, записанного блоке 5 оперативной памяти ранее. Блок 1 постоянной памяти преобразует этот цифровой код в графический код знака. Порядковый номер вертикального фрагмента знака, выводимого из блока 1 постоянной памяти в каждый данный момент времени, задается цифровым кодом с

первого выхода блока 8 счетчиков. Синхросигнал со второго выхода блока 8 счетчиков обеспечивает запись фрагмента знака в необходимую часть регистра 2, выходные сигналы которого являются управляющими для информационных электродов матричного индикатора 3. Каждому знакоместу матричного индикатора 3 соответствует свой адрес в блоке 5 оперативной памяти.

0 Допустим, что электроды развертки расположены вертикально и матрица знакоместа состоит из 35 индикаторных элементов (5 вертикальных столбиков по 7 индикаторных элементов в каждом). В этом случае

5 блок 8 счетчиков управляет работой устройства следующим образом.

Блок 4 развертки выбирает первый электрод первого столбца матриц знакомест. Одновременно блок 8 счетчиков по0 следовательно опрашивает блок 5 оперативной памяти по адресам, соответствующим первому столбцу знакомест, с адреса верхнего до адреса нижнего знака. Коды информации, записанные в блок 5 опера5 тивной памяти, воздействуя на блок 1 постоянной памяти, выводят графические коды первых фрагментов всех знаков первого столбца, которые затем записываются в регистр 2 таким образом, что первый фрагмент

0 верхнего знака оказывается в той части регистра 2, которая управляет индикаторными электродами верхнего знакоместа матричного индикатора 3, первый фрагмент второго сверху знака оказывается в части

5 регистра 2, управляющей индикаторными электродами второго сверху знакоместа, и т.д. Вывод информации из блока 5 оперативной памяти, преобразование ее в блоке 1 постоянной памяти и заполнение регистра

0 2 осуществляется за время, составляющее меньшую часть периода выбора электрода развертки матричного индикатора 3. Большую часть времени информация, записанная в регистр 2, статична и возбуждает

5 необходимые индикаторные элементы матричного индикатора 3.

Далее, блок 8 счетчиков с помощью блока 4 развертки выбирает второй вертикальный электрод первого столбца знакомест

0 матричного индикатора 3, опрашивает блок 5 оперативной памяти по тем же адресам, соответствующим первому столбцу знаков. На блок 1 постоянной памяти с блока 8 счетчиков в это время подается код второго

5 фрагмента знаков, которыми заполняется регистр 2. Таким же образом выводится на индикацию третий, четвертый и пятый фрагменты всех знаков при выборе третьего, четвертого и пятого электродов столбца знакомест.

При отображении второго столбца знаков поочередно выбираются первый, второй, третий, четвертый и пятый электроды второго столбца знакомест Пять раз опрашивается блок 5 оперативной памяти по адресам второго столбца знакомест и каждый раз из блока 1 постоянной памяти выводятся последовательно первый, второй, третий, четвертый и пятый фрагменты знаков, которые далее записываются в регистр 2 и возбуждают необходимые индикаторные элементы матричного индикатора 3. Таким образом, осуществляя развертку кадра изображения, последовательно возбуждаются нужные индикаторные элементы всех знакомест и на матричном индикаторе 3 отображается информация, записанная в блоке 5 оперативной памяти.

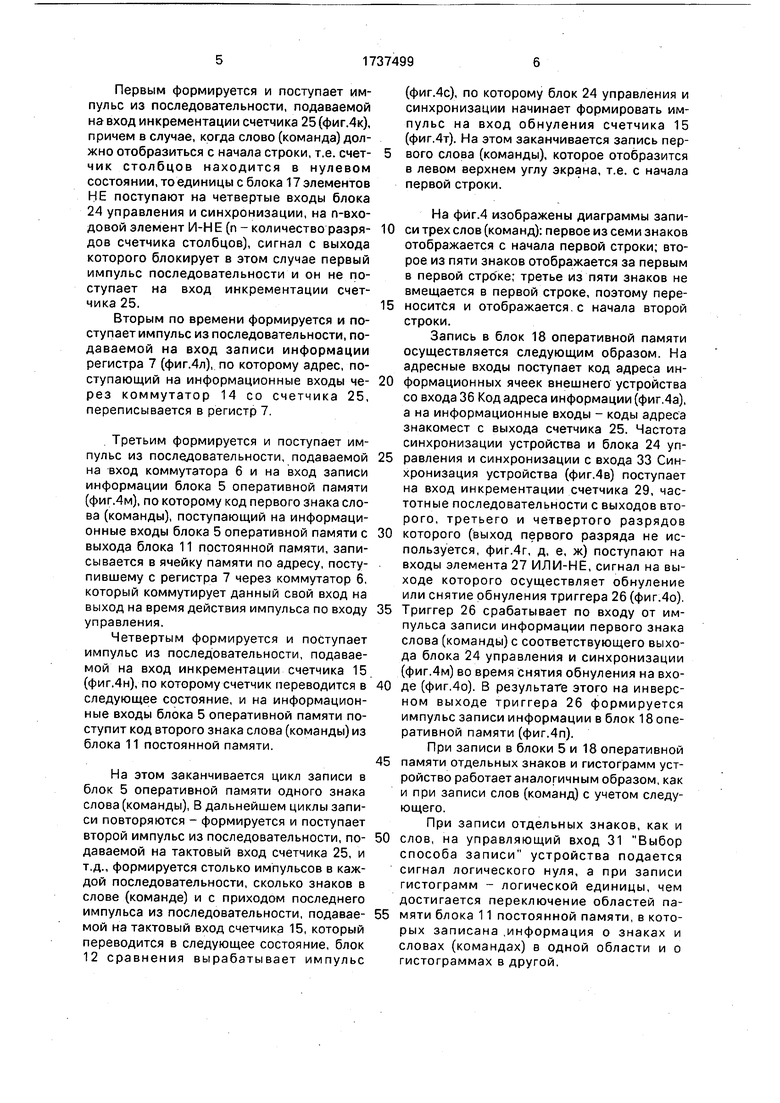

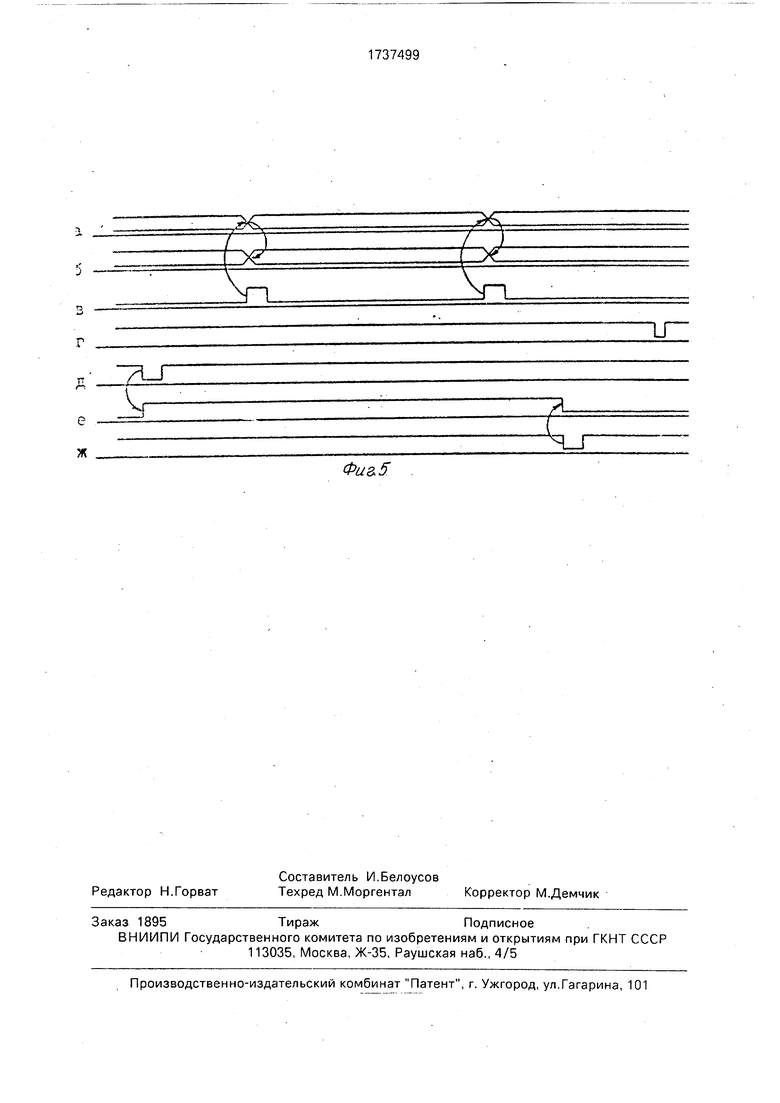

Рассмотрим работу устройства в режиме редактирования информации на примере редактирования отдельными словами (командами).

В режим редактирования информации устройство переводится подачей импульса по управляющему входу 37 Маркер устройства (фиг.бд), что вызывает сброс триггера 19 и появление сигнала логической единицы на инверсном выходе триггера 19 (фиг.Бе), который подается на вход элемента 28 И-НЕ и тем самым разрешает прохождение положительных импульсов смены адреса в сторону увеличения или уменьшения кода адреса информации во внешнем устройстве (вход 36, фиг.ба) с управляющего входа 38 Инкремент адреса информации или с управляющего входа 39 Декремент адреса информации (фиг.бв) через элемент 30 ИЛИ и элемент 28 И-НЕ на вход формирователя 21 импульсов, который от передних фронтов этих импульсов выдает через элемент 20 И отрицательные импульсы записи в регистр 7. На информационные входы регистра 7 в это время подается код адреса знакоместа, соответствующего первому знаку какого-либо слова (команды), из блока 18 оперативной памяти через коммутатор 14. Сигнал логической единицы с инверсного выхода триггера 19 по установочному входу блока 10 управления маркером разрешает его работу. Блок 10 управления маркером позволяет определить, в каком состоянии находится адресный регистр 7. Информационные входы блока 10 управления маркером подключены к соответствующим выходам адресного регистра 7, а на вход сброса периодически подается импульс Сброс из блока 4 развертки, осуществляющий запись кода адреса знакоместа, после чего по тактовым входам подаются импульсы с частотами, соответствующими опросу блока 5 оперативной памяти по столбцам и строкам. С выхода блока 10 управления маркером в блок 1 постоянной памяти поступает сигнал логического нуля, производящий высвечивание всех точек знакоместа с адресом, соответствующим состоянию адресного регистра 7. Таким образом, маркерный сигнал на экране матричного индикатор 3, вырабатывае0 мый при помощи блока 10 управления маркером, при смене адреса информации (фиг.Ба) будет перемещаться по первым знакам наименований слов (команд). После этого на установочный вход 35 Запись знака

5 счетчика 25 подается импульс (фиг.бж), который производит запись в него адреса знакоместа первого знака нужного слова (команды) из блока 18 оперативной памяти и взводиттриггер 19, сигнал логической еди0 ницы с прямого выхода которого переключает коммутатор 14 так, что к информационным входам регистра 7 подключаются выходы счетчика 25, при этом маркерный сигнал на экране матричного ин5 дикатора 3 гаснет. Затем на информационные входы 32 Код информации устройства (фиг.56) подается код нужного слова (команды) и далее по управляющему входу 34 Запись информации устройства подается

0 импульс (фиг.5г)г по которому производится запись в блоки 5 и 18 оперативной памяти, как это ранее было описано в режиме записи информации.

Аналогично осуществляется редактиро5 вание записанной информации как в виде отдельных знаков, так и в виде гистограмм. Блок 24 управления и синхронизации работает следующим образом.

Импульс со входа 34 Запись информа0 ции приходит в блок на вход элемента 52 задержки (фиг.4з), с которого задержанный импульс является выходным импульсом блока (выход 62, фиг.4и), производящим запись информации в счетчик 15, а по заднему

5 фронту входного импульса (фиг.4з) срабатывают триггеры 46 и 55, соответственно снимается обнуление (выход 64 блока) со счетчика 15 (фиг.4т) и начинает формироваться импульс (выход 67 блока) на вход

0 стробирования блока 13 сравнения (фиг.4р). Положительные импульсы тактовой частоты со входа 33 Синхронизация устройства и блока поступают на первые входы элементов 41 и 43 И. а также на тактовый

5 вход триггера 42, с прямого и инверсного выходов которого снимаются парафазные меандры соответственно на вторые входы элементов 41 и 43 И, на выходах которых формируются две сдвинутые последовательности импульсов, причем с выхода элемента 41 И последовательность на вход ин- крементации счетчика 15 (выход 63 блока) формируется с приходом сигнала с прямого выхода триггера 54, который в свою очередь включен по схеме триггера защелки и пере- водится в единичное состояние по заднему фронту первого, прошедшего через элемент 47 И-НЕ импульса последовательности с элемента 43 И, прохождение которой через элемент 47 И-НЕ обеспечивает сигнал с пря- мого выхода триггера 46, который введен в единичное состояние задним фронтом импульса со входа 34 Запись информации. Первый импульс с элемента 47 И-НЕ сбрасывает триггер 55 по обнуляющему входу, что обеспечивает окончание формирования импульса (выход 67 блока) на вход строби- рования блока 13 сравнения (фиг.4р). Последовательность положительных импульсов с выхода элемента 49 НЕ производит каждым импульсом запуск формирователя 53 пары импульсов, задержанных относительно запускающего и сдвинутых по отношению друг к другу (фиг.4л, м, выходы 66 и 65 блока). Импульсы на выходах 66 и 65 блока соответственно производят запись адреса в регистр 7 и запись информации по этому адресу в блок 5 оперативной памяти. Последовательность положительных импульсов с выхода элемента 49 НЕ поступает также на вход элемента 50 И-НЕ, на второй вход которого подается сигнал с элемента 45 И-НЕ, соответствующий единице, когда на входе этого элемента хотя бы один из входных сигналов (входы 58-61), поступающих с вы- хода блока 17 инверторов, равен нулю (счетчик столбцов не в нулевом состоянии), в результате чего последовательность через элемент 50 И-НЕ и через элемент 56 И-НЕ поступает на выход 68 блока (сигнал инкрементации счетчика 25), а при сигнале с элемента 45 И-НЕ, равном нулю (счетчик столбцов в нулевом состоянии), первый импульс последовательности не проходит через элемент 50 И-НЕ на выход 68 блока и счетчик столбцов, входящий в счетчик 25, не меняет своего состояния. Единичный сигнал с прямого выхода триггера 54, появившийся по заднему фронту первого импульса последовательности с элемента 49 НЕ, а также единица с элемента 48 НЕ разрешает прохождение второму импульсу последовательности через элемент 51 И-НЕ на элемент 56 И-НЕ и на выход 68 блока, в результате чего счетчик столбца изменит свое нулевое состояние на единичное и элемент 45 И-НЕ разрешит прохождение импульсов последовательности через элемент 50 И-НЕ для дальнейшей работы. С окончанием записи слова (команды) блок 12 сравнения начинает вырабатывать единичный сигнал (фиг.4с), который поступает на вход 57 блока 24 управления и сигнализации и на первый вход элемента 44 И-НЕ, в результате чего на выходе этого элемента формируется нулевой сигнал, обнуляющий триггеры 46,54, и с инверсного выхода триггера 46 снимается на выход 64 блока обнуляющий потенциал на счетчик 15(фиг.4т), обнуление которого приводит к окончанию единичного сигнала на выходе блока 12 сравнения, а также к окончанию обнуляющего сигнала с выхода элемента 44 И-НЕ на триггеры 46 и 54.

Элементы блока установились в исходное состояние для приема и отображения следующего слова (команды). На второй и третий входы элемента 44 И-НЕ поступают отрицательные импульсы с элемента 40 НЕ, вход которого подключен к выходу элемента 41 И, и с элемента 52 задержки, блокирующие возможные помехи, поступающие на первый вход с выхода блока 12 сравнения, которые возникают в результате переходных процессов при записи информации в счетчик 15 и при его инкрементации.

Счетчик 25 работает следующим образом.

Применение двоичных счетчиков в качестве счетчиков 69,72 столбцов и страниц обусловлено тем, что в индикаторе ИМГ-1- 03 экран имеет 16 столбцов и 4 страницы информации, а применение двоично-десятичного счетчика в качестве счетчика 71 строк обусловлено тем, что в индикаторе ИМГ-1-03 экран имеет 10 строк.

В режиме записи соответствующими счетчиками счетчика 25 осуществляется счет столбцов, строк и страниц с записью информации с выходов счетчика 69 столбцов и счетчика 71 строк в регистр 7 и информации об адресе знакомест первых знаков слов (команд) в блок 18 оперативной памяти. В этом же режиме отрицательный импульс с выхода блока 13 сравнения по входу сброса 75 счетчика 25 осуществляет сброс счетчика 69 столбцов и через элемент-70 И перевод счетчика 71 строк в следующее состояние.

В режиме отображения информации счетчики 69,71,72 находятся в статическом состоянии.

В режиме редактирования информации после выбора нужного адреса слова (команды) на информационных входах 74 и 76 счетчиков 69 и 71 установлен код адреса знакоместа первого знака этого слова (команды) и по установочному входу 35 счетчика 25 подачей импульса осуществляется запись в него этого кода. Затем после подачи импульса на вход 34 Запись информации блока 24 управления и синхронизации на вход 73 счетчика 25 поступает серия импульсов, количество которых равно количеству знаков в слове (команде), при этом счетчики счетчика 25 отсчитывают это количество импульсов.

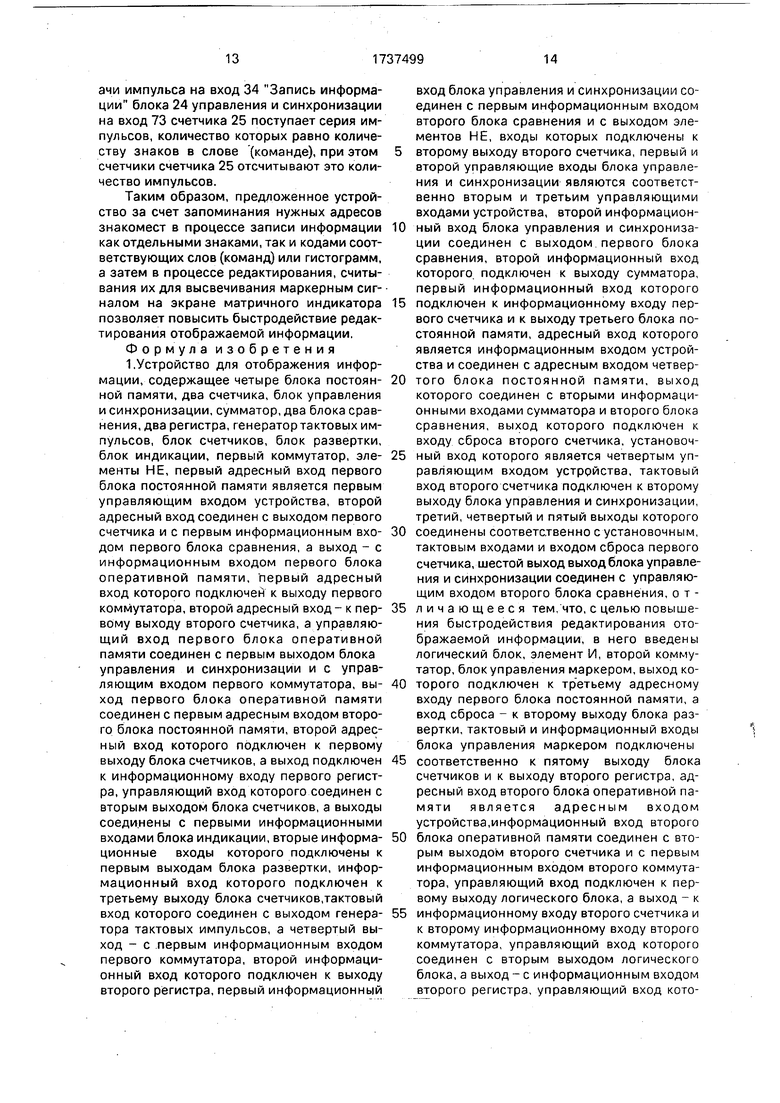

Таким образом, предложенное устройство за счет запоминания нужных адресов знакомест в процессе записи информации как отдельными знаками, так и кодами соответствующих слов (команд) или гистограмм, а затем в процессе редактирования, считывания их для высвечивания маркерным сигналом на экране матричного индикатора позволяет повысить быстродействие редактирования отображаемой информации. Формула изобретения 1.Устройство для отображения информации, содержащее четыре блока постоян- ной памяти, два счетчика, блок управления и синхронизации, сумматор, два блока сравнения, два регистра, генератор тактовых импульсов, блок счетчиков, блок развертки, блок индикации, первый коммутатор, эле- менты НЕ, первый адресный вход первого блока постоянной памяти является первым управляющим входом устройства, второй адресный вход соединен с выходом первого счетчика и с первым информационным вхо- дом первого блока сравнения, а выход - с информационным входом первого блока оперативной памяти, первый адресный вход которого подключен к выходу первого коммутатора, второй адресный вход - к пер- вому выходу второго счетчика, а управляющий вход первого блока оперативной памяти соединен с первым выходом блока управления и синхронизации и с управляющим входом первого коммутатора, вы- ход первого блока оперативной памяти соединен с первым адресным входом второго блока постоянной памяти, второй адресный вход которого подключен к первому выходу блока счетчиков, а выход подключен к информационному входу первого регистра, управляющий вход которого соединен с вторым выходом блока счетчиков, а выходы соединены с первыми информационными входами блока индикации, вторые информа- ционные входы которого подключены к первым выходам блока развертки, информационный вход которого подключен к третьему выходу блока счетчиков,тактовый вход которого соединен с выходом генера- тора тактовых импульсов, а четвертый выход - с первым информационным входом первого коммутатора, второй информационный вход которого подключен к выходу второго регистра, первый информационный

вход блока управления и синхронизации соединен с первым информационным входом второго блока сравнения и с выходом элементов НЕ, входы которых подключены к второму выходу второго счетчика, первый и второй управляющие входы блока управления и синхронизации являются соответственно вторым и третьим управляющими входами устройства, второй информационный вход блока управления и синхронизации соединен с выходом первого блока сравнения, второй информационный вход которого подключен к выходу сумматора, первый информационный вход которого подключен к информационному входу первого счетчика и к выходу третьего блока постоянной памяти, адресный вход которого является информационным входом устройства и соединен с адресным входом четвертого блока постоянной памяти, выход которого соединен с вторыми информационными входами сумматора и второго блока сравнения, выход которого подключен к входу сброса второго счетчика, установочный вход которого является четвертым управляющим входом устройства, тактовый вход второго счетчика подключен к второму выходу блока управления и синхронизации, третий, четвертый и пятый выходы которого соединены соответственно с установочным, тактовым входами и входом сброса первого счетчика, шестой выход выход блока управления и синхронизации соединен с управляющим входом второго блока сравнения, о т - личающееся тем, что, с целью повышения быстродействия редактирования отображаемой информации, в него введены логический блок, элемент И, второй коммутатор, блок управления маркером, выход которого подключен к третьему адресному входу первого блока постоянной памяти, а вход сброса - к второму выходу блока развертки, тактовый и информационный входы блока управления маркером подключены соответственно к пятому выходу блока счетчиков и к выходу второго регистра, адресный вход второго блока оперативной памяти является адресным входом устройства,информационный вход второго блока оперативной памяти соединен с вторым выходом второго счетчика и с первым информационным входом второго коммутатора, управляющий вход подключен к первому выходу логического блока, а выход - к информационному входу второго счетчика и к второму информационному входу второго коммутатора, управляющий вход которого соединен с вторым выходом логического блока, а выход - с информационным входом второго регистра, управляющий вход которого подключен к выходу элемента И, первый вход которого соединен с третьим выходом логического блока, а второй вход - с седьмым выходом блока управления и синхронизации, первый выход которого подключен к первому входу логического блока, а первый управляющий вход - к второму входу логического блока, четвертый выход которого соединен с установочным входом блока управления маркером, а третий, четвертый и пятый входы логического блока являются соответственно четвертым, пятым и шестым управляющими входами устройства.

2,Устройство поп.1,отличающее- с я тем, что логический блок содержит элемент И-НЕ, формирователь импульсов, первый триггер, третий счетчик, элемент ИЛИ-НЕ, второй триггер, установочный

вход которого является первым входом логического блока, инверсный выход второго триггера является первым выходом логического блока, а вход сброса соединен с выходом элемента ИЛИ-НЕ, входы которого соединены с выходами третьего счетчика, тактовый вход которого является третьим входом логического блока, второй вход которого подключен к установочному входу

первого триггера, а четвертый вход-к входу сброса первого триггера, пятый вход логического блока соединен с первым входом элемента И-НЕ, а второй выход - с прямым выходом первого триггера, четвертый выход

логического блока подключен к инверсному выходу первого триггера и к второму входу элемента И-НЕ, а третий выход соединен с выходом формирователя импульсов, тактовый вход которого подключен к выходу элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1987 |

|

SU1443024A1 |

| Формирователь символов для устройств отображения информации на матричных экранах | 1989 |

|

SU1688280A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1989 |

|

SU1793458A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1401447A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Устройство для ввода информации | 1991 |

|

SU1828553A3 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1985 |

|

SU1312560A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1987 |

|

SU1495780A1 |

,Фиг.2

п

25

Фиг.З

DC

-ib

DC

fe

1JlanлJlRЛJШЛллJ JгnAлллJlшшг

д

e ж

b

2C

Sc

2x:

jh.

/-L

-w-.

-0„ 7U

e Т

Ж

Фи&5

7ГТ

Vi.

Авторы

Даты

1992-05-30—Публикация

1990-03-12—Подача