1

Изобретение относится к области вычислительной техники, в частности, к устройствам переменного приоритета и может быть использовано при построении вычислительных комплексов и систем обмена информацией.

Известно устройство переменного приоритета 1, содержащее регистры, дешифраторы, схемы совпадения, схемы сборки, схемы сравнения, триггеры, счетчик пропущенных обращений в каждой позиции приоритета с дополнительными схемами сборки и схемами совпадения.

Недостатком устройства является необходимость больших затрат оборудования при его реализации.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство переменного приоритета 2, содержащее блок хранения ходов приоритетов, выходы которого соединены с кодовыми входами коммутатора, регистр запросов, разрядные выходы которого соединены с первыми входами соответствующих элементов И группы, причем выходы элементов И группы соединены с соответствующими управляющими входами коммутатора, а разрядные входы регистра запросов соединены с запросными входами устройства.

Недостатком устройства является значительная сложность его построения.

Цель изобретения - упрощение устройства.

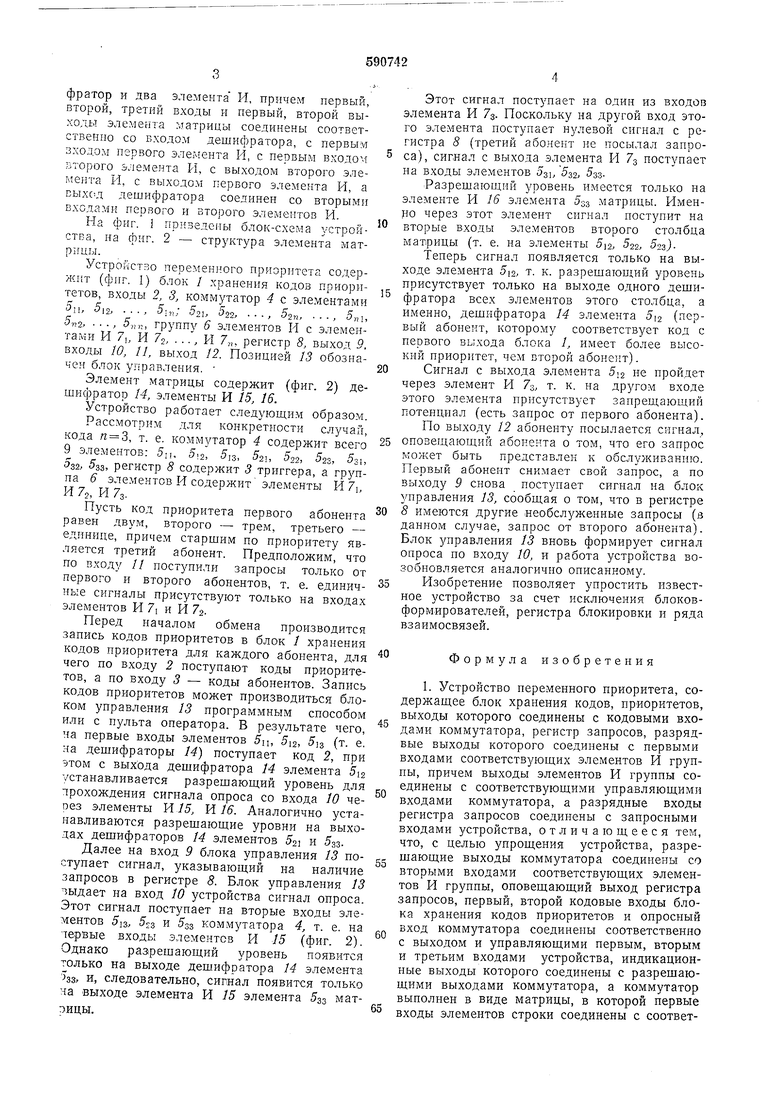

Поставленная цель достигается тем, что разрешающие выходы коммутатора соединены со вторыми входами соответствующих элементов И группы, оповещающий выход регистра запросов, первый, второй кодовые входы блока хранения кодов приоритетов и опросный вход коммутатора соединены соответственно с выходом и управляющими первым, вторым и третьим входами устройства, индикационные выходы которого соединены с разрешающими выходами коммутатора, а коммутатор выполнен в виде матрицы, в которой первые входы элементов строки соединены с соответствующим кодовым входом коммутатора, опросный вход которого соединен со вторыми входами элементов столбца мат)ицы, первые выходы элементов столбца матрицы соединены со вторыми входами элементов предыдущего столбца матрицы, вторые выходы элементов строки матрицы соединены с соответствующим разрешающим выходом коммутатора, третьи входы элементов строки матрицы соединены с соответствующим управляющим входом коммутатора.

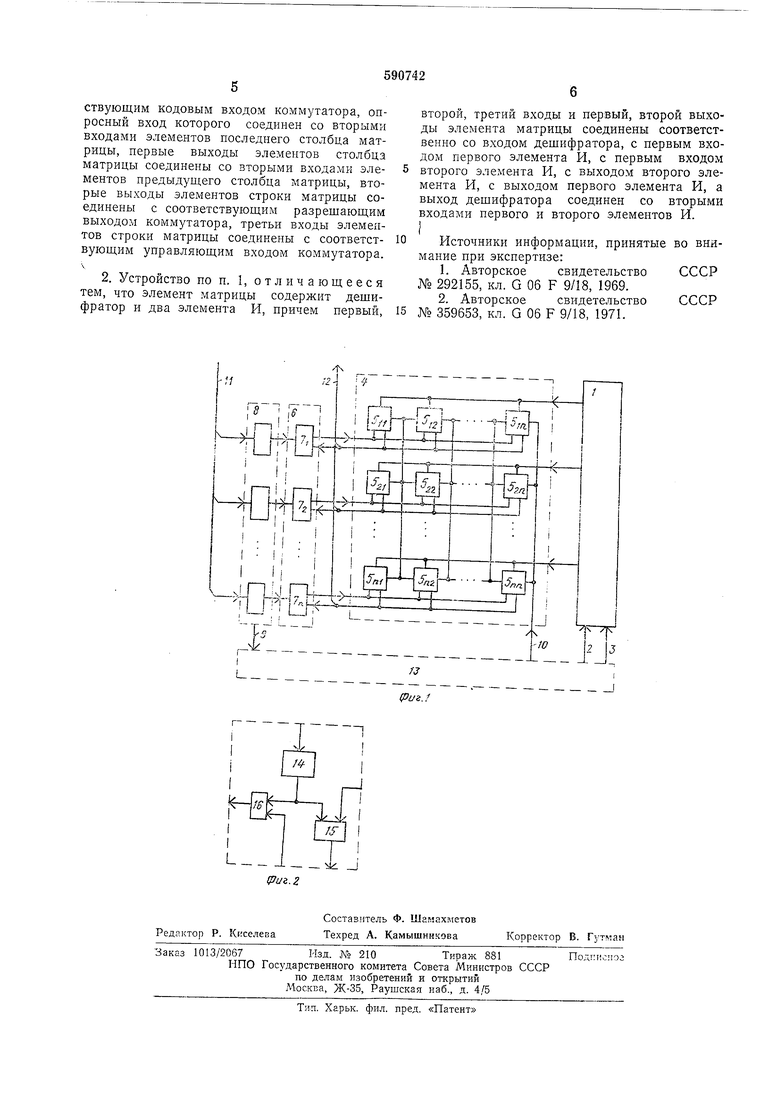

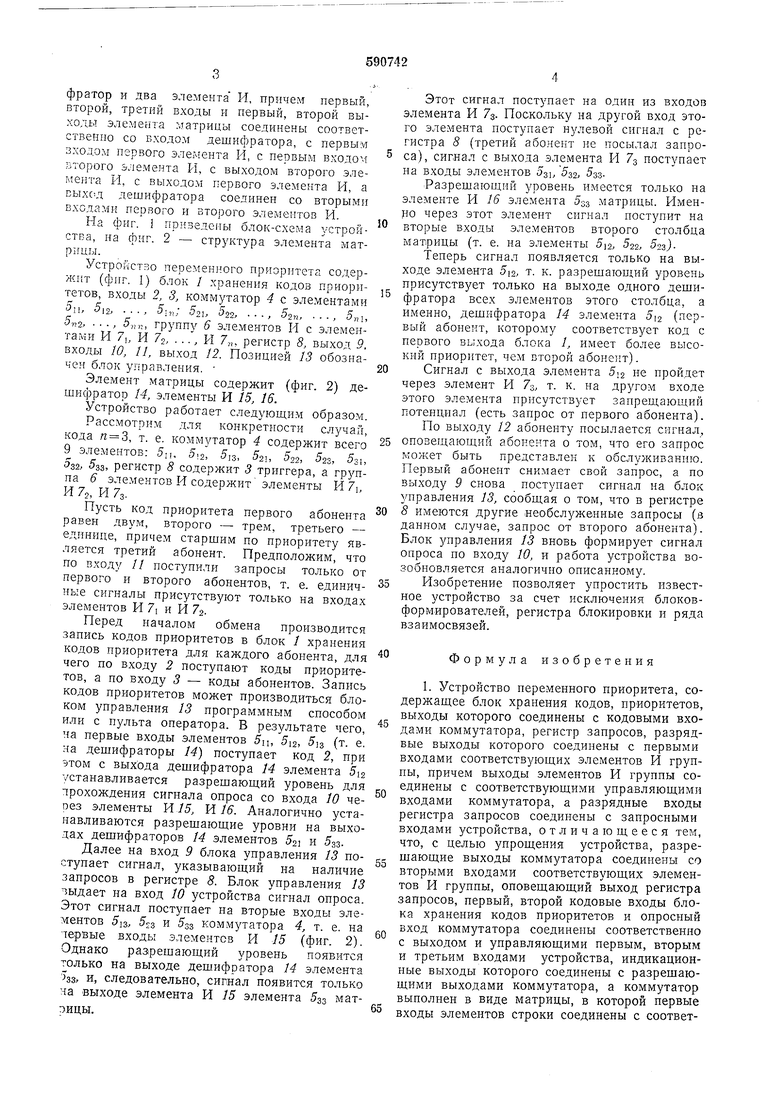

Поставленная цель достигается также тем, что элемент матрицы содержит дещифратор и два элемента И, причем первый, второй, третий входы и первый, второй выходы элемента матрицы соединены соответственно со входом дешифратора, с первым зходом первого элегчента И, с первым входом йторого элемента И, с выходом второго элемента И, с выходом первого элемента И, а сыхс-д дешифратора соединен со вторыми входами первого и второго элементов И. На фиг. приведены блок-схема устройства, на фиг. 2 - структура элемента матрицы. Устройство переменного приоритета содержит (фиг. I) блок / хранения кодов приоритетов, входы 2, 3, коммутатор 4 с элементами 512; , 5i-fi 5zn, , Уп1, 5п2, , 5пп, группу 6 элементов И с элементами И 7|, И /2, .... И 7„, регистр 8, выход 9. входы 10, 11, выход 12. Позицией 13 обозиачен блок управления. Элемент матрицы содержит (фиг. 2) дешифратор 14, элементы И 15, 16. Устройство работает следующим образом. Рассмотрим , конкретности сл)чай, кода л 3, т. е. коммутатор 4 содержит всего 9 элементов: S, 5.2, , , 822, 23, 5з, 32, 5z3, регистр 8 содержит 3 триггера, а группа 6 эле.ментов И содержит элементы И 7ь И /2, И 7з. Пусть код приоритета первого абонента равен двум, второго - трем, третьего - единице, причем старшим по приоритету является третий абонент. Предположим, что по входу // поступи.ди запросы только от первого и второго абонентов, т. е. единичные сигналы присутствуют только на входах элементов И 7i и И 72. Перед началом обмена производится запись кодов приоритетов в блок / хранения кодов приоритета для каждого абонента, для чего по входу 2 поступают коды приоритетов, а по входу 3 - коды абонентов. Запись кодов приоритетов может производиться блоком управления 13 программным способом или с пульта оператора. В результате чего, на первые входы элементов 5п, 5i2, 5i3 (т. е. на дешифраторы 14) поступает код 2, при этом с выхода дешифратора 14 элемента 5i2 устанавливается разрешаюший уровень для прохождения сигнала опроса со входа 10 чеоез элементы HIS, И16. Аналогично устанавливаются разрешаюш;ие уровни на выходах дешифраторов 14 элементов 52 и 5зз. Далее на вход 9 блока управления 13 поступает сигнал, указывающий на наличие запросов в регистре 5. Блок управления 13 выдает на вход 10 устройства сигнал опроса. Этот сигнал поступает на вторые входы элементов , 5s3 и 5зз коммутатора 4, т. е. на lepBbie входы элементов И 15 (фиг. 2). Однако разрешающий уровень появится только на выходе дешифратора 14 элемента Таз. и, следовательно, сигнал появится только на выходе элемента И 15 элемента 5зз матЭтот сигнал поступает на один из входов элемента И /а- Поскольку на другой вход этого элемента поступает нулевой сигнал с регистра 8 (третий абонент не посылал запроса), сигнал с выхода элемента И 7з поступает на входы элементов 5зь 5з2. 5ззРазрешающий уровень имеется только на элементе И 16 элемента 5зз матрицы. Именно через этот элемент сигнал поступит на вторые входы элементов второго столбца матрицы (т. е. на элементы 5j2. 522, 52з). Теперь сигнал появляется только на выходе элемента 5i2. т. к. разрешающий уровень присутствует только на выходе одного дешифратора всех элементов этого столбца, а именно, дешифратора 14 элемента 5i2 (первый абонент, которому соответствует код с первого вьхода блока 1, имеет более высокий приоритет, чем второй абонент). Сигнал с выхода элемента 5i2 не пройдет через элемент И 7з, т. к. на другом входе этого элемента присутствует запрещающий потенциал (есть запрос от первого абонента). По выходу 12 абоненту посылается сигнал, оповещающей абонента о том, что его запрос может быть представлен к обслуживанию. Первый абонент снимает свой запрос, а по выходу 9 снова поступает сигнал на блок управления 13, сообщая о том, что в регистре 8 имеются другие необслуженные запросы (в данном слзчае, запрос от второго абонента). Блок управления 13 вновь формирует сигнал опроса по входу 10, и работа устройства возобновляется аналогично описанному. Изобретение позволяет упростить известное устройство за счет исключения блоковформирователей, регистра блокировки и ряда взаимосвязей. Формула изобретения 1. Устройство переменного приоритета, содержащее блок хранения кодов, приоритетов, выходы которого соединены с кодовыми входами коммутатора, регистр запросов, разрядвые выходы которого соединены с первыми входами соответствующих элементов И группы, причем выходы элементов И группы соединены с соответствующими управляющими входами коммутатора, а разрядные входы регистра запросов соединены с запросными входами устройства, отличающееся тем, что, с целью упрощения устройства, разрешающие выходы коммутатора соединены со вторыми входами соответствующих элементов И группы, оповещающий выход регистра запросов, первый, второй кодовые входы блока хранения кодов приоритетов и опросный вход коммутатора соединены соответственно с выходом и управляющими первым, вторым и третьим входами устройства, индикационные выходы которого соединены с разрешаюими выходами коммутатора, а коммутатор ыполнен в виде матрицы, в которой первые ходы элементов строки соединены с соответствующим кодовым входом коммутатора, опросный вход которого соединен со вторыми входами элементов последнего столбца матрицы, первые выходы элементов столбца матрицы соединены со вторыми входами элементов предыдущего столбца матрицы, вторые выходы элементов строки матрицы соединены с соответствующим разрещающим выходом коммутатора, третьи входы элементов строки матрицы соединены с соответствующим управляющим входом коммутатора.

.

2. Устройство по п. I, отличающееся тем, что элемент матрицы содержит дешифратор и два элемента И, причем первый.

второй, третий входы и первый, второй выходы элемента матрицы соединены соответственно со входом дешифратора, с первым входом первого элемента И, с первым входом второго элемента И, с выходом второго элемента И, с выходом первого элемента И, а выход дешифратора соединен со вторыми входами первого и второго элементов И.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 292155, кл. G 06 F 9/18, 1969.

2.Авторское свидетельство СССР № 359653, кл. G 06 F 9/18, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1976 |

|

SU942021A1 |

| Устройство приоритета | 1977 |

|

SU674023A1 |

| Приоритетное устройство | 1976 |

|

SU638963A1 |

| Многоканальное устройство переменного приоритета | 1983 |

|

SU1095180A1 |

| Устройство для сопряжения | 1976 |

|

SU703798A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Матричный коммутатор | 1991 |

|

SU1800605A1 |

| Устройство для группового обслуживания запросов | 1984 |

|

SU1196868A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Устройство для сопряжения | 1976 |

|

SU651335A1 |

Авторы

Даты

1978-01-30—Публикация

1976-05-03—Подача