Изобретеуие относится к вычислительной технике и может быть использовано для управления сверхоперативной буферной памятью (СБП) высокопроизводительных ЭВМ. Известно устройство, которое содержит буферную память, регистр адреса процессора, блок сравнения адресов, коммутатор адреса ряда, регистр записываемой информации, регистр считанной информации, коммута тор адреса.колонки, матрицу адресов блок приоритетов l. Данное устройство имеет недостаточно высокое быстродействие из-за примененного алгоритма обслуживания запросов в память процессоров и каналов ввода-вывода (при каждой запи си требуется обращение к основной о ративной памяти); кроме того, не обеспечена совмещенная работа блока трансляции адреса и матрицы адресов со сверхоперативной буферной памятью, ЧТО увеличивает время обращения к СБП. Реализованный алгоритм замещений блоков информации не позволяет увеличить производительность ЭВМ путем применения СБП большей емко- сти. Наиболее близким к предлагаемому является устройство, содержащее блок буферной памяти, матрицу адресов, блок приоритетов, регистры считанной и записываемой информации, регистр кодов защиты памяти 2. Указанное устройство имеет несколько большее быстродействие так как обслуживание запросов каналов вводавывода не влияет на время обслуживания запросов процессоров, но сохраняет недостатки вышеописанного устройства. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ, содержащее селектор адресов, селектор маркеров и селектор входной информации, управляющие входы которых объединены и подключены к выходу блока приоритетов, выход которого является приоритетным выходом устройства, первые входы селекторов являются канальным адресным, канальным маркерным и канальным информационным входами устройства, соответственно, первый вход блока приоритетов является канальным входом запроса устройства, выходы селектора маркеров и селектора входной информации соединены соответственно с входами регистра маркеров и регистра входной информации, выходы которых соединены с выходом маркеров и выходом записываемой информации устройства соответственно, а также с входом маркеров и данных блока сверхоперативной буферной памяти, вход разрешения записи которого соединен с выходом триггера разрешения записи, вход которого соединен с выходом второго элемента ИЛИ, .первый вход которого соединен с выходом первого элемента И, первый вход последнего соединен с выходом первого элемента ИЛИ, входы которого соединены с входами шифратора, выход которого соединен с первым входом селектора номера строки, выход которого соединен с входом регистра номера строки, выход которого соединен с входом номера строки блока сверхоперативной буферной памяти и входом номера строки матрицы адресов, вход нового адреса которой соединен с выходом адреса страницы регистра адреса матрицы адресов, который является выходом адреса страницы устройства, а вход регистра адреса матрицы адресов соединен с выходом селектора адресов вход адреса копирования которого соединен с выходом счетчика копирования селектор считанной информации, выход которого соединен с входом регистра считанной информации, а выход последнего является выходом считанной информации устройства, и регистр кодов защиты памяти, введены селектор идентификаторов, селектор кодов защиты памяти, регистр идентификаторов матрицы адресов, два дешифратора, триггер длинных операций, счетчик длинных операций матрица кодов защиты памяти, счетчик слов, блок замещения, регистр адреса колонки, регистр идентификаторов буферной памяти, блок коррекции, мультиплексор, адресов, блок анализа ,мультиплексор адресов, блок анализа, мультиплексор считанной информации, блок управления записью новых данных, матрица битов изменения, мультиплексор битов изменения, второй элемент И, триггер конца операции, третий и четвертый элементы ИЛИ, регистр номера процессора, выход которого является выходом номера процессора устройства, а вход соединен с первым выходом регистра идентификаторов бу5ферной памяти, второй выход которого соединен с входом второго дешифратора, первый выход которого соединен с первым входом четвертого элемента ИЛИ, второй вход которого соеодинен с выходом триггера разрешения записи, а выход - с входом разрешения записи матрицы битов изменения, адресный вход которой соединен с адресными входами блока коррекции, мат5рицы кодов защиты, блока замещения, регистра адреса колонки и с выходом адреса колонки регистра адреса матрицы адресов, который является соответствующим выходом устройства, а выход

0 адреса слова регистра адреса матрицы адресов, который является выходом адреса слова устройства, соединен с входом счетчика слов, выход которого соединен с управляющим входом

5 регистра адреса колонки, выход по- . , следнего соединен с адресным входом блока сверхоперативной буферной памяти , вход номера строки которого соединен с входами номера строки матри0цы кодов защиты, матрицы битов изменения, блока замещения и с адресными входами мультиплексора адресов, мультиплексора битов, изменения, мультиплексора считанной информации, вход

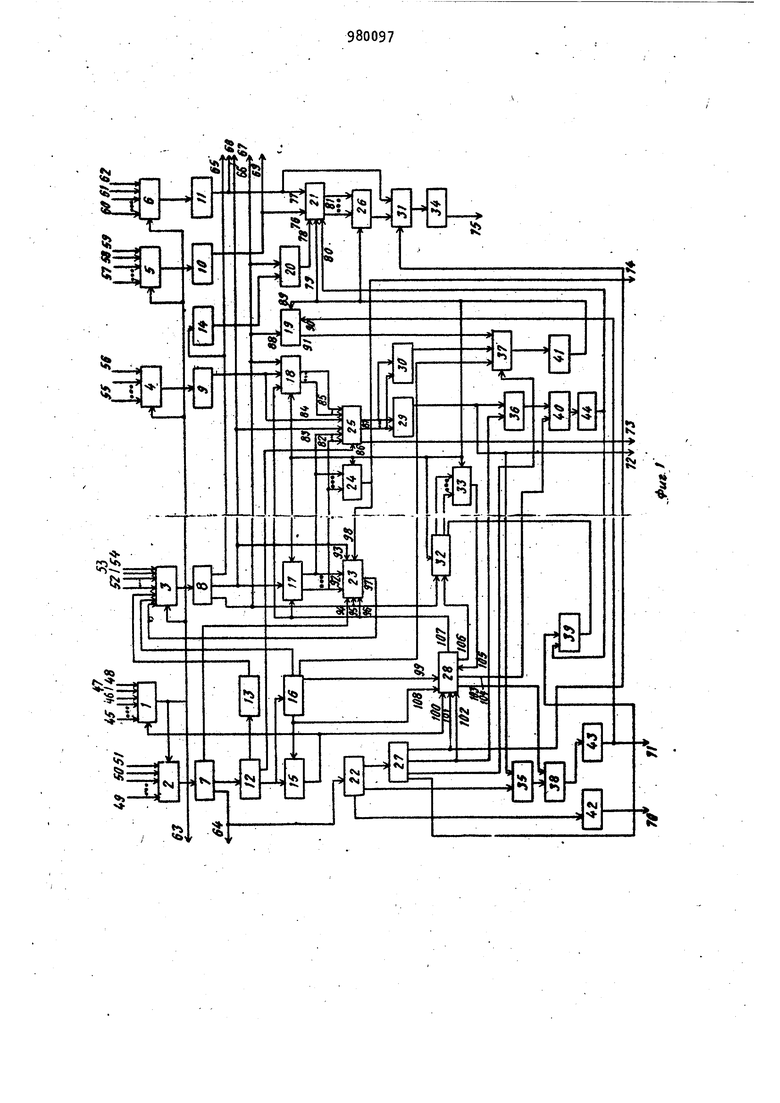

5 данных которого соединен с выходом считанной информации, блока сверхоперативной буферной памяти, а вы-,ход - с первым входом данных селектора считанной информации, управляю0щий вход которого соединен с входом операции перезаписи блока управления записью новых данных, выход бита изменения активного блока которого соединен с входом данных матрицы би5тов изменения, выход.которой соединен с входом данных мультиплексора битов изменения, выход которого соединен с входом бита изменения заме5щаемых данных блока управления записью новых данных, выход записи ад реса которого соединен .с входами ра решения записи блока коррекции, мат рицы кодов защиты, матрицы адресов, выход которой соединен с входом счи танных адресов блока анализа, входом хранимых данных блока коррекции, входом данных мультиплексора адресов, выход которого является выходом адреса страницы замещаемых данных устройства и соединен с вхо дом замещаемых данных блока коррекции , вход ошибки которого соединен с выходом ошибки адреса регистра идентификаторов матрицы адресов, а выход - с входом откорректированного адреса селектора адресов, вторые входы селекторов адреса маркеров, и входной информации являются соответственно адресным входом, вхо дом маркеров и информационным входом связи с процессорами устройства, группа входов селектора адресов, селектора маркеров и селектора входной информации является соответ ственно группой входов адресов процессоров устройства, группой входов маркеров процессоров устройства и группой входов информации процессоров устройства, третий вход селектора адресов соединен с первым выходом счетчика длинных операций, вход которого соединен с установочным входом триггера длинных операций и с первым выходом первого дешифратора , второй выход которого со динен с входом счетчика копирования, а вход соединен с выходом кода операции регистра индентификаторов матрицы адресов, выход идентифи каторов которого является соответствующим выходом устройства и соеди нен с входом регистра идентификаторов буферной памяти, а вход соедине с выходом селектора идентификаторов группа входов селектора идентификаторов является группой входов идентификаторов процессоров устройства, первый вход селектора является канальным входом идентификаторов уст.ройства, второй вход селектора явля ется входом связи с процессорами устройства, управляющий вход селек тора -идентификаторов соединен с выходом блока приоритетов и управляю щим входом селектора кодов защиты, группа входов блока приоритетов и его первый, второй и третий входы 7 являются соответственно группой входов запросов процессоров устройства, входом запроса блока обслуживания устройства, входом запроса канала и входом запроса связи с процессорами устройства, управляющий вход блока приоритетов соединен с выходом триггера длинных операций и с входом продолжительности длинных операций блока управления записью новых данных, вход переполнения которого соединен с выходом переноса счетчика длинных операций и входом сброса триггера длинных операций, вход четвертого такта блока управления записью соединен с вторым выходом счетчика длинных операций, вход операции записи - с вторым выходом второго дешифратора и с вторым входом первого элемента И, выход записи новых данных - с вторым входом второго элемента ИЛИ, а выход конца операции - с первым входом третьего элемента ИШ, второй вход которого соединен с выходом второго элемента И, а выход - с установочным входом триггера конца операции, выход которого является выходом конца операции устройства и соединен с входом разрешения записи блока замещения, выход которого соединен с вторым входом селектора номера строки .третий вход которого соединен с третьим выходом счетчика длинных операций а управляющий вход - с третьим выходом второго дешифратора, четвертый выход которого соединен с входом операции перезаписи блока управления записью, второй вход данных оперативной памяти селектора считанных данных соединен с входом блока сверхоперативной буферной памяти, группа входов селектора кодов заи11иты является группой входов кодов защиты процессоров устройства, вход селектора кодов защиты является канальным входом кодов защиты устройства, выход селе ip-op а кодов защиты соединен входом регистра кодов защиты, выход которого соединен с входом кода защиты новых данных матрицы кодов защиты и входом кода защиты запроса блока анализа, вход считанных кодов защиты которого оединен с выходом матрицы кодов защиты, вход адреса запроса - с входами нового адреса матрицы адресов и блока коррекции, вход операции чтения - с третьим выходом первого дешифратора, выход ошибки адреса является выходом устройства, а выходы сравнения соединены с входами первого элемента ИЛИ, выход которого яв ляется выходом наличия информации устройства и соединен с первыми входами первого и BTOpqro элементов И, второй вход второго элемента И соединен с третьим выходом регистра идентификаторов буферной памяти. Блок анализа содержит первую груп пу из m (m - целое число) элементов И, вторые и первые входы которых соединены соответственно с выходами т блоков свертки по модулю два кодов защиты и с выходами m схем сравнения кодов защиты, первые входы которых объединены и являются входом кода защиты запроса блока, а.вторые входы.соединены с входами блоков свертки по модулю два кодов защиты и являются входом считанных кодов защиты блока, вторую группу из m элементов И, выходы ко торых являются выходом сравнения блока, первые и вторые входы соеди,нены соответственно с выходами m блоков свертки по модулю два адресов и с выходами m схем сравнения адресов, первые входы которых соединены с входами блоков свертки по мо дулю два адресов и являются входом считанных адресов-блока, а вторые входы объединены и являются входом адреса запроса блока, m элементов ИЛИ, выходы которых соединены с соответствующими третьими входами эле ментов И второй ГРУППЫ, первые входы соединены с выходами элементов И первой группы, а вторые входы объ единены и являются входом операции чтения блока, элемент И, m входов которого соединены с соответствующими первыми входами элементов И второй группы, а выход - 9 входом эл мента НЕ , выход которого является выходом ошибки адреса блока. Кроме того, блок управления записью новь|х данных содержит три элемента НЕ, четыре триггера, два элемента. ИЛИ, четыре элемента И, причем вход четвертого такта блока соединен с установочным входом первого триггера и первым входом первого эле мента И, второй вход которого соеди нен с выходом первого триггера и вхо дом третьего элемента НЕ, информаци онный вход первого триггера соедине с входом первого элемента НЕ и с вх дом бита изменения замещаемого слов 78 блока, выход первого элемента НЕ соединен с первым входом четвертого элемента И, второй вход которого соединен с входом операции перезаписи блока и с информационным входом второго триггера, установочный вход которого соединен с установоч -i/ ным входом третьего триггера и выходом второго элемента НЕ, вход которого является входом продолжительности длинной операции блока, информацирнный вход третьего триггера является входом операции записи блока, а выход - выходом бита изменения активного блока, вход переполнения блока соединен с первым входом второго элемента И, второй вход которого соединен с третьим входом первого элемента И и первым входом третьего элемента И и выходом второго триггера, выход третьего элемента НЕ соединен с третьим и вторым входами второго и третьего элементов И соответственно, выход третьего элемента И является выходом записи блока, выход первого элемента И соединен с первыми входами первого и второго элементов ИЛИ, выход второго элемента И соединен с вторым входом первого элемента ИЛИ, выход которого соединен с входом четвертого три|- гера, выход которого является выходом записи адреса блока, выход четвертого элемента. И соединен с вторым входом второго элемента ИЛИ, выход которого является выходом конца операции бгюка. Одним из факторов, определЙющих быстродействие ЭВМ, является алгоритм обслуживания запросов процессоров и каналов ввода-вывода к двухуровневой оперативной памяти. В изобретении использован алгоритм Полностью асинхронный условный обман. При этом операция Запись при на- личйи данных в СБП выполняется только в СБП, а при отсутствии данных требуется один цикл ОП. В итоге значительно сокращается среднее время выполнения операции Запись. Структурная организация СБП и ее управление, кроме того, позволяют совместить цикл чтения собственно СБП с ассоциативным поиском в матрице адресов Это уменьшает время обслуживания запросов в СБП, В предлагаемом устройстве использовано техническое решение ( З) в качестве блока замещения. В целях обеспечения высокой надежности в состав устройства включен блок коррекции ошибок С а матрице адресов Структурные решения предлагаемого устройства позволяют использовать его для обслуживания запросов к двухуровневой оперативной памяти процессоров и каналов вводавывода , включенных в состав мультипроцессорной cиcteмы с минимальными задержками из-за конфликтов. Устройство может быть использовано для управления сверхоперативной буферной памятью, памятью в мул типроцессорной системе с общими ресурсами (СБП обслуживает запросы всех процессоров) и в системе, где СБП интегрированы со своими процессорами. . Устройство может обслуживать запросы процессоров к памяти на чтение или запись информации с темпом: каждый такт-один запрос при наличии информации в СБП, а при отсутствии инфррмации в СБП необходима перезапись блока информации из ОП в СБП с тем, чтобы последующие обра щения процессора к этому блоку информации обслуживались на уровне СБ Один запрос на чтение или запись информации в СБП обслуживается за два такта: такт матрицы адресов (МА и такт сверхоперативной.буферной памяти (в матрице адресов хранятся адреса тех блоков информации из ОП, которые имеются в СБП), при этом ор ганизован совмещенный режим работы МА и СБП по двум последовательным запросам, т.е. при обслуживании одного запроса в такте. СБП для следующего запроса выполняется такт МД На фиг, 1 представлена структурная схема устройства для управления сверхоперативной буферной памятью ЭВМ, на фиг, 2 - структурная схема блока сверхоперативной буферной naмяти; на фиг, 3 - структурная схема блока анализа; на фиг, t - структур ная схема блока замещения , на фиг.5 структурная схема блока коррекции; на фиг. 6 - структурная схема блока управления записью новых данных на фиг. 7 блок-схема алгоритма Полностью асинхронный условный объем. Устройство для управления сверхоперативной буферной памятью мульти 9710 процессорной ЭВМ содержит блок 1 приоритетов, селектор 2::идентификаторов, селектор 3 адресов, селектор кодов защиты , селектор 5 маркеров, селектор 6 входной информации, регистр 7 идентификаторов матрицы адресов, регистр 8 адреса матрицы адресов, регистр 9 защиты памяти, регистр 10 маркеров, регистр 11,входной информации, первый дешифратор 12, счетчик 13 копирования, счетчик }k слов, триггер 15 длинных операций, счетчик 16 длинных операций, матрицу 17 адресов, матрицу 18 кодов защиты памяти, блок 19 замещения, регистр 20 адреса колонки, блок 21 СБП,.регистр 22 идентификаторов буферной памяти, блок 23 коррекции, мультиплексор 2Ц адресовав, блок 25 анализа, мультиплексор 26 считанной информации, второй дешифратор 27, блок 28 управления . записью новых данных, первый элемент ИЛИ 29 шифратор 30, селектор 31 считанной информации матрицу 32битов изменения, мультиплексор 33битов изменения, регистр 3 считанной информации, второй элемент И 35, первый элемент И 36, селектор 37 номера строки, третий элемент ИШ 38, четвертый элемент ИЛИ 39, второй элемент ИЛИ 0, регистр номера строки, регистр «2 номера процессора, триггер 3 конца операции, триггер ЦЦ разрешения записи, входы канальных запросов процессоров устройства, вход связи с процессорами и вход блока обслуживания устройства, входы 9-51 идентификаторов процессоров устройства каналов и вход связи с процессорами, входы 52-5 адресов процессоров устройства, каналов и вход связи с процессорами, входы 55 и 56-КОДОВ защиты памяти процессоров устройства и входы маркеров процессоров устройства, канала и вход связи с процессорами, входы 60-62 информации процессоров устройства,.канала и вход связи с процессорами, выход 63 приоритетов, выход 6 идентификаторов , выход 65 адреса слова, выход 66записываемой информации, выход 67адреса колонки, выход 68 адреса страницы, выход 69 маркеров, выход 70 номера процессора, выход 71 конца операции, выход 72 наличия информации, выход 73 ошибки адреса, выход 7 адреса страницы замещаемого блока, выход 75 считанной инфорнации, выходы 76 маркеров, входы 77 данных, адресный вход 78, вход 79 номера строки, вход 80 разрешения записи, выходы 81 m строк, входы 82 считанных адресов, вход 83 адреса запроса, вход 8 кода защиты- запроса, входы 85 считанных кодов защит вход 86 операции чтения, выходы 87 сравнения, адресный вход 88, вход 89 номера строки, вход 90 разрешения записи, выход 91 номера замещаемой строки, входы 92 хранимых данных, вход 93 нового адреса, вход 9 ошибки адреса, адресный вход 95, вход 9б разрешения записи, выход 97откорректированного адреса, вход 98замещаемых данных, вход 99 четвертого такта, вход 100 продолжительности длинной операции, вход 101 операции перезаписи, вход 102 операции записи, выход103 конца операции, выход 104 записи блока, вход 105 бита изменения замещаемого блока, выход 106 бита изменения активного блока, выход 107 записи адреса, вход 108 переполнения, субблоки 109 памяти, дешифратор 110, m блоков 111 свертки по модулю два адресов, m схем 112 сравнения адреm схем 113 сравнения кодов защ блоков 114 свертки по модулю два кодов защиты, первую группу из m элементов И 115, m элементов ИЛИ 116, вторую группу из m элементов И 117, т-входовой элемент И 118, элемент НЕ 119, селектор 120 замещения, регистр 121 адреса замещения, шифратор 122, регистр 123 за писи хронологии, блок 124 памяти хронологии, селектор 125 хронологии регистр 126 чтения хронологии, дешифратор 127, регистр 128 адреса хронологии, селектор 129 адреса, сх му 130 сравнения, первый блок 131 поразрядного сложения, коммутатор 132, сдвигатель 133, второй блок 134поразрядного сложения, регистр 135вертикальной четности, первый блок 136 свертки, регистр 137 коррекции, первый элемент НЕ 138, блок 139 памяти вертикальной четности, второй блок l40 свертки, первую схе му l4l сравнения, второй элемент НЕ 142, третий элемент НЕ 143, вторую схему 144 сравнения, четвертый элемент НЕ 145, элемент И 146, выход 147 ошибок коррекции, элементы HL 148, 149, триггер 150 удаления блока, триггер 151 перезаписи, триг 9712 гер 152 бита изменения, элемент НЕ 153, элементы И 15/t-157, элементы ИЛИ 158, 159, триггер 1бО запи-си адреса, Устройство работает следующим образом. Выполнение операции Чтение двойного слова (данные в СБП имеются). В блоке 1 приоритетов анализируются имеющиеся запросы, одному из запросов присваивается приоритет в соответствии со следующей дисциплиной: первый приоритет имеет блок об- служивания, второй - адаптер связи с процессорами, третий - буферная секция каналов, четвертый - процессоры. 8 соответствии с присвоенным приоритетом в приемных селекторах 2 идентификаторов, 3 адреса, 4 кодов защиты 5, маркеров, 6 входной информации открывается направление для. приема всей информации о запросе от этого зааросчика на регистры 7 идентификаторов, 8 адреса, 9 защиты памяти, 10 маркеров, 11 входной информации, а соответствующему устройству выдается сигнал о присвоении приоритета. По адресу колонки с регистра 8 адреса матрицы адресов считываются значения матрицы 17 адресов и блока 19 замещения, параллельно адрес колонки записывается на регистр 20 адреса колонки,на который также принимается номер двойного слова в блоке данных СПБ со счетчика 14 слов. В блоке 25 анализа адреса, считанные из МА 17, сравниваются на схемах i12 поразрядного сравнения с адресом запроса с регистра 8 и контролируются на блоках 111 свертки. Если в считанных адресах имеется ошибка, то на выходе 73 блока 25 анализа появляется сообщение об ошибке адреса. Если ошибки нет и с выхода первого дешифратора 12 приходит сигнал о выполнении операции Чтение двойного слова, то в рассматриваемом режиме (данные есть в СБП) на одном из выходов 87 блока 25 анализа появляется сигнал Сравнение адресов этой стойки матрицы 17 адресов и Запроса, который кодируется на шифраторе 30 в номер сравнившейся строки и через селектор 37 записывается на регистр 41 номера строки. На элементе ИЛИ 29 формируется сигнал наличия информации , который выдается в буферную секцию каналов, если обслуживается ее запрос, или используется для формирования сигнала конца операции, есл обслуживается запрос одного из процессоров. Одновременно с работой блока 25 «анализа и формированием номера срав нившейся строки из блоков 109 памяти блока 21 СБП в соответствии с ад ресом регистра 20 адреса колонки сч тываются двойные слова всех строк колонки, которые поступают на вход данных мультиплексора 26 считанной информации, на адресный вход которо го в этот же момент поступает .номер сравнившейся строки с регистра номера строки. С выхода мультиплексора 26 данные попадают через вход данных буферной памяти селектора 31 считанной информации Не регистр З считанной информации для выдачи запросчику. Таким образом, цикл чтения собственно блоков 109 памяти совмещен с ассоциативным поиском адреса запроса и формированием номера сравнившейся строки. После цикла чтения матрицы 17 адресов идентификаторь запроса переписываются с регистра 7 идентификаторов матрицы адресов на регистр 2 идентификаторов буферной памяти для окончания обслуживания, а на уровень МА принимaetcя новый запрос в соответствии с работой блока 1 приоритетов. Одновременно с . выдачей считанной информации на регистр k2 номера процессора записывается номер процессора с регистра 22 идентификаторов, запрос которого обслужен, что сопровождается сигналом конца операции, который формируется на элементах И°35, ИЛИ 38 и триггере 3 конца опе рации. Сигнал конца операции используется также для изменения текущего значения хронологии блока 19 замещения , Выполнение операции записи двоит ного слова данных в СБП (рассматрива ется режим наличия данных в СБП) име ет следующие отличия от вышеописанно го режима работы устройства, В блоке 25 анализа для формирования сигналов сравнения используются кроме сравнения и контроля адресов, сравнение считанных кодов защиты из матрицы 18 кодов защиты с кодом защиты запроса с регистра 9 кода защиты и KOH троль считанных кодов защиты (элемен ты 113, И и 115 блока 25 анализа). Сигнал.наличия информации с выхода элемента ИЛИ 29 поступает на один из входов элемента И Зб, на второй вход которого приходит сигнал операции записи с выхода второго дешифратора 27, и через элемент ИЛИ tO устанавливает в 1 триггер разрешения записи. Выход триггера под| лючен на управляющий вход дешифратора 10 блока 21 СБП, на адресный вход которого приходит номер сравнив иейся строки с регистра tl номера строки. При э,том на одном из выходов деши фратора появляется сигнал разрешения записи в блоки 109 памяти СБП, принадлежащие этой строке блока 21 СБП, На входы данных блоков 109 памяти поступают байты информации с выходов регистра 11 входной информации. Запись производится только в те блоки 109 памяти соответствующей строки СБП, входы обращения которых отличны ОТ О, т,е, в соответствии с выходами регистра 10 маркеров. Параллельно с записью новой информации в блок 21 СБП в матрице 32 битов изменения устанавливается в 1 бит изменения этой строки СБП, причем на вход данных матрицы 32 поступает логическая единица с выхода триггера 152 бита изменения из блока 28 управления, который устанавливается д это состояние при каждой операции записи соответствующим выходом второго дешифратора 27, на вход разрешения записи матрицы 32 через элемент ИЛИ 39 поступает сигнал разрешения записи с триггера t, а номер строки определяется выходом регистра номера строки. Таким образом, анализ кода защиты запроса одновременно с анализом адреса запроса и возможность.фиксации каждого изменения информации в блоке БСП позволяют выполнять операцию записи двойного слова за 2 такта, как и, операцию чтения двойного слова. Такой алгоритм выполнения операции записи двойного слова, когда при наличии информации в СБП запись проиа водится только в СБП, а в ОП данные остаются без изменения, приводит к тому, что операция перезаписи помещение в СБП нового блока данных, если по запросу процессора необходимых данных в СБП не оказалось может быть двух видов: с удалением замещаемого блока данных, если бит изменения этого блока равен единице, опе рация занимает 9 тактов (один такт НА и восемь тактов СБП); без удалени замещаемого блок, если бит изменени этого блока равен нулю, операция занимает 5 тактов (один такт МА и четыре такта СБП) . .Рассмотрим первый вариант - выполнение операции перезаписи блока . с удалением замещаемого блока. Если по запросу процессора необходимого двойного слова данных не оказалось в блоке 21 СБП, то не будет выработан сигнал наличия информа ции, .и следовательно, не будет.взведен триггер k} конца операции. Такой запрос попадает -в очередь в ОП в ада тере связи с процессорами, а устройство продолжает обслуживать запросы других устройств. По получении блока информации из ОП- адаптер связи с процессорами получает приоритет бло ка 1 приоритетов и вся и нформация о запросе вновь попадает.на триамные регистры, но уже с признаком операции перезаписи на регистре 7 идентификаторов. Здесь следует заметить что в СБП из ОП помещается не одно двойное слово, необходимое процессору, а блок данных - четыре последовательных двойных слова с тем, что бы последующие запросы процессора мо ли быть обслужены на уровне СБП. По признаку операции-перезаписи с выхода длинных операций первого дешифра тора 12 устанавливается в единицу триггер 15 ДЛИ.ННЫХ операций, формирующий запрет в блок 1 приоритетов, а на сче.тчик 16 длинных операций за писывается такое значение, чтобы., при последующем счете за один Такт до окончания операции на его выходе переполнения появиласьединица, которая сбросит триггер 15 длинных оп раций с тем, чтобы снять запрет с блока 1 приоритетов (последний такт СБП всегда совмещен с -тактам МА нового запроса). По адресу колонки с регистра 8 адреса матрицы адресов в блоке 19 замещения считывается значение памя ти хронологии обращения к блокам эт колонки и на дешифраторе 127 формируется номер блока для замещения ег новым блоком (замещается блок, к ко торому наиболее долго не было обращения от выполняемых программ) . С выхода 91 блока 19 замещений номер замещаемой строки через селектор 37 номера строки попадает на регистр Ц номера строки, который попадает, на адресный вход мультиплексора 33 битов изменения, на вход данных которого к этому времени считываются значения битов изменения всех строк этой колонки. С выхода мультиплексора 33 бит изменения замещаемого блока попадает в блок 28 управления записью новых данных и устанавливает в 1 триггер 150 удаления. С выходов второго дешифратора 27 операции перезаписи устанавливается в единицу триггер 151 перезаписи и операции записи (если блок помещается по запросу процессора на запись двойного слова) --триггер 152 бита изменения. Из блока 21 СБП в соответствии с регистром 20 адреса колонки, регистра 1 номера строки через мультиплексор 26 и селектор 31 считанной информации на регистр 3, считанной информации считываются последовательно четыре двоичных слова замещаемого блока данных для записи в ОП. Пересчет номера двойного слова обеспечивается счетчиком И слов. Через мультиплексор 2 адресов в соответствии с номером замещаемой строки с регистра 1, который попадает на адресный вход мультиплексора, считывается адрес страницы замещаемого блока в оперативной памяти (выход 7) , а адрес колонки замещаемого блока появляется на выходе 67 адреса колонки устройств. По окончании считывания четвертого двойного слова сигналом четвертого такта со счетчика длинных операций сбрасывается триггер 150 удаления и на элементах НЕ 153 и И 156 формируется сигнал записи блока, который через элемент ИЛИ О устанавливает в 1 триггер kk разрешения записи на четыре такта для записи в блоке 21 СБП четырех двойных слов информации с регистра 11 входной информации из адаптера связи с процессорами на место замещаемого блока, определяемое регистром 41 номера строки, С записью в блок СБП первого двойного слова в селекторе 31 считанной информации открывается вход данных оперативной памяти и на регистр 3 считанной информации попадает первое двойное слово данных, которое выдается в процессор, если был запрос на чтениеJ на элементах И IS, ИЛИ 158 формируется сигнал конца операции, который из блока 28 управления записью новых данных через элемент ИЛИ ЗВ записывается на триггер ДЗ конца операции и сопровождается номером процессора С регистра kZt Перед записью последнего елова в блок СБП сигналом .переполнения через элементы И 155, ИЛИ 159 устанавливается в 1 триггер 160 запиСИ адреса блока 28 управленил который разрешает записать в матрицу 17 адресов новый адрес с репистра 8 в матрицу 18 кодов защиты - код защиты нового адреса с регистра 9, в блок 19 замещения через элепент ИЛИ 39 новое значение хронологии, в блок 2 коррекции - новое значение битов вертикальной четности, а в матрицу 32 битов изменения - бит изменения с выхода 1 об бита изменения активного блока (триггер 152 бита изменения) .блока 28 управления. Запись-все новых значений производится в строку, определяемую регистром +1 номера строки. По сбросу триггера 15 длинных операций сбрасываются триггеры 151 и 152 блока 28 управления записью новых данных. Второй вариант операции перезаписи блока без удаления замещаемого блока отличается от первого тем, что бит изменения замещаемого блока на входе мультиплексора 33 битов изменения равен нулю, поэтому триггер 150 удаления блока 28 управления остается в нуле, следовательно, выполняется сразу вторая часть операции п резаписи - запись нового блока в СБП и в матрицу 17 адресов, матрицу 18 кодов защиты, матрицу 32 битов изменения, блок 19 замещения, блок 23 коррекции новых значений. Перед записью четвертого двойного слова сбра сывается триггер 15 длинных операций и открывается блок 1 приоритетов для приема нового запроса. Таким образом, второй вариант операции перезаписи занимает четыре такта работы устройства. Для того чтобы операция перезаписи, как правило, выполнялась за k такта, введена операция копирования, которой присваивается приоритет автоматически всегда, когда устрой9718ство свободно. Адрес колонки в этом случае задается счетчиком 13 копирования, значение которого через селектор 3 адресов записывается на регистр 8 адреса матрицы адресов. С выхода блока 19 замещения номер замещаемого блока записывается через селектор 37 на регистр Ч номера строки В соответствии с этим номером из блока 21 СБП считывается из колонки, определяемой счетчиком копирования, блок данных из четырех двойных слов на регистр 3 считанной информации для запиЛ1 его в оперативную память. Выход операции копирования второго дешифратора 2 через элемент ИЛИ 39 разрешает записать бит изменения этого блока данных в матрице 32 битов изменения в нуль, Перед началом каждой новой операции копирования в счетчик копирования прибавляется По запросу буферной секции каналов при наличии информации в блоке СБП имеется возможность чтения и записи блока данных (четырех двойных СЛОВ). В этом случае также устанавливаётся в 1 триггер 15.длинных операций для формирования запрета в блок 1 приоритетов. Номер двойного слова меняется в регистре адреса колонки счетчиком слов. В остальном выполнение операций совпадает с чтением и записью двойного слова при на личии информации в блоке СБП. Имеется возможность по запросу блока обслуживания переписать содержимое блока 21 СБП в оперативную память, чтобы в ОП была последняя копия блоков данных. Для этого на счетчик 16 длинных операций записывается нулевое значение в разряды номера колонки и номера строки, а триггер 15 длинных операций устанавливается в 1 для запрета блока 1 приоритетов. Номер колонки счетчика 16 попадает через селектор 3 адре-сов на регистр 8 адреса матрицы адресов, в соответствии с которым из матрицы 17 адресов считываются адреса блоков в ОП, а из блока 21 СБП двойные слова данных той же колонки. Номер строки со счетчика 16 попадает через селектор 37 номера строки на регистр номера строки, в соответствии с..которым из нулевой колонки блока СБП считывается блок данных нулевой строки на регистр З считанной информации, а из матрицы 17 адресов через мультиплексор 2 адресов - адрес этого блока в ОП. Через четыре такта, когда считаны четыре двойных слова блока данных нулевой строки колонки, в счетчик 16 длинных операций в разряды номера строки прибавляется 1 для считывания блока первой строки нулевой колонки и т.д. После достижения номером стро ки максимального значения прибавляется в разряды номера колонки счетчика 16, Когда считаны все блоки СБП, значение счетчика 16 длинных операций достигают максимальной величины и сигнал переполнения сбрасывает триггер 15 длинных бпераций. Если при обслуживании запроса про цессора во время считывания матрицы 17 адресов появилась ошибка адреса на выходе блока 25 анализа, то сигна ла конца операции выработано не будет и запрос попадает в адаптер связи с процессорами, а затем возвращается в устройство с признаком ошиб ки адреса в регистре 7 идентификаторов матрицы адресов. В соответствии с этим признаком инициируется работа блока 23 коррекции, откорректированный адрес с выхода блока 23 коррекции поступает через селектор 3 адресов на регистр 8 адреса матрицы адресов для записи-его в МА, Кроме то го по сигналам из блока обслуживания предусмотрена возможность отключения половины емкости блока 21 СБП и/или любой строчки блока 21 СБП Таким образом, повышение .быстродействия устройства достигнуто благодаря совмещению во времени ассоциативного поиска в матрице адресов и считыванию или записи данных в СБП Реализованная в устройстве дисциплина обслуживания запросов процес соров и каналов ввода-вывода к двухуровневой оперативной памяти позволя ет сократить среднее время обслуживания, т.е, уменьшить эффективный цикл оперативной памяти. формула изобретения 1, yetроиство для управления све оперативной буферной памятью мульти процессорной ЭВМ, содержащее селек тор адресов, селектор маркеров и се лектор входной информации, управляю щие входы которых объединены и поДключены к выходу блока приоритетов, выход которого является приоритетным выходом устройства, первые входы селекторов являются соответственно канальным адресным, канальным маркерным и канальным информационным входами устройства, первый вход блока приоритетов является канальным входом запроса устройства, выходы селекора маркеров и селектора входной информации соединены соответственно с входами регистра маркеров и регистра входной информации, выходы кото - рых соединены соответственно с выходом маркеров и выходом записываемой информации устройства, а также с входом маркеров и данных блока сверхоперативной буферной памяти, вход разрешения записи которого соединен с выходом триггера разрешения записи, вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом первогоэлемента И, первый входпоследнего соединен с выходом первого элемента ИЛИ, входы которого соединены с входами шифратора, выход которого соединен с первым входом селектора номера строки, выход последнего соединен с входом регистра номера строки, выход которого соединен с входом номера строки блока сверхоперативной буферной памяти и входом номера строки матрицы адресов, вход нового адреса которой соединен с выходом адреса страницы регистра адреса матрицы адресов, который является выходом адреса страницывустройства, а вход регистра адреса матрицы адресов соединен с выходом селектора адресов, вход адреса копирования которого соединен с выходом счетчика копирования; селектор считанной информации, выход которого соединен с входом регистра считанной информации, а выход последнего является выходом считанной информации устройства, и регистр кодов защиты памяти, отличающееся тем, что, с целью повышения быстродействия, устройства,«в него введены селектор идентификаторов, селектор кодов защиты памяти, регистр идентификаторов матрицы адресов, два дешифратора, триггер длинных операций, счетчик длинных операций, матрица кодов защиты памяти, счетчик слов, блок замещения, регистр адреса колонки, регистр идентификаторов буфермой памяти, блок коррекции, муль типлексор адресов, блок анализа, мультиплексор считанной информации, блок управления записью новых данных, матрица битов изменения, мультиплексор битов изменения, второй элемент И, триггер конца операции, третий и четвертый элементы ИЛИ, регистр номера процессора, выход ко торого является выходом номера процессора устройства, а вход соединен с первым выходом регистра идентификаторов буферной памяти, второй выход которого соединен с входом второго дешифратора, первый выход последнего соединен с первым входом четвертого элемента ИЛИ, второй вхо которого соединен с выходом триггер разрешения записи, а выход - с входом разрешения записи матрицы битов изменения, адресный вход которой со динен с адресными входами блока кор рекции, матрицы кодов защиты блока замещения, регистра адреса колонки и с выходом адреса колонки регистра адреса матрицы адресов, который является соответствующим выходом устройства, а выход адреса слова регис ра адреса матрицы адресов, который является выходом адреса слова устройства, соединен с входом счетчика слов, выход которого соединен с управляющим входом регистраадреса колонки, выход последнего соединен с адресным входом блока сверхоператив ной буферной памяти, вход номера ст ки которого соединен с входами номера строки матрицы кодов защиты, матрицы битов изменения, блока замещения и с адресными входами мультиплексора адресов, мультиплексора битов изменения, мультиплексора считан ной информации, вход данных которого соединен с выходом считанной информации блока сверхоперативной буферной памяти, а выход - с первым входом данных селектора считанной информации, управляющий вход которого соединен с входом операции перезаписи блока управления записью новых данных, выход бита изменения активного блока которого соединен с входом данных матрицы битов изменения, выход последней соединен с входом данных мультиплексора битов изме- нения, выход которого соединен с входом бита изменения замещаемых данных блока управления записью новых данных, выход записи адреса которого соединен с входами разрешения записи блока коррекции, матрицы кодов защиты, матрицы адресов, выход которой соединен с входом считанных адресов блока анализа, входом хранимых данных блока коррекции, входом данных мультиплексора адресов, выход которого является выходом адреса страницы замещаемых данных устройства и соединен с входом замещаемых данных блока коррекции, вход ошибки которого соединен с выходом ошибки адреса регистра идентификаторов матрицы адресовI а выход с входом откорректированного адреса селектора адресов, вторые входы селекторов адреса, маркеров и входной информации являются соответственно адресным входом, входом маркеров и информационным входом связи с процессорами устройства, группа входов селектора адресов, селектора маркеров и селектора входной информации является соответственно группой входов адресов процессоров устройства, группой входов маркеров процессоров устройства и группой входов информации процессоров устройства, третий вход селектора адресов соединен с первым выходом сметчика длинных операций, вход которого соединен с установочным входом триггера длинных операций и с первым выходом первого дешифратора, второй выход .которого соединен с входом счетчика копирования, а вход соединен с выходом кода операции регистра идентификаторов матрицы адресов, выход идентификаторов которого является соответствующим выходом устройства и соединен с входом регистра идентификаторов буферной памяти, а вход соединен с выходом селектора идентификаторов, группа входов селектора идентификаторов является группой входов идентификаторов процессоров устройства, первой вход селектора является канальным входом идентификаторов устройства, второй вход селектора является входом связи с процессорами устройства, управляющий вход селектора идентификаторов соединен с выходом блока приоритетов и управляющим входом селектора кодов защиты, группа входов блока приоритетов и его первый, второй и третий входы являются соответственно группой входов запросов процессоров устройства, входом запроса блока рбслуживания устройства, входом запроса .канала и входом запроса связи с процессорами устройства, управляющий вход блока приоритетов соединен с выходом триггера длинных операций и с входом продолжительности длинных операций блока управления за писью новых данных, вход переполнения которого соединен с выходом пере носа счетчика длинных операций и вхо дом сброса триггера длинных операций вход четвертого такта блока управления записью Соединен с вторым, выхо- дом счетчика д/1инных операций, вход операции записи - с вторым выходом второго дешифратора и с вторым вхог дом первого эле|« ента И, выход записи новых данных - с вторым входом второго элемента ИЛИ, а выход конца операции - с первым входом .третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход - с установочным входом триггера конца операции, выход которого является выходом конца операции устройства и соединен с входом разрешения записи блока замещения, выход которого соединен с вто рым входом селектора номера строки, третий вход которого соединен с третьим выходом счетчика длинных операций, а управляющий вход - с третьим выходом второго дешифратора четвертый выход которого соединен с входом операции перезаписи блока управления записью, второй вход данных оперативной селектора считанных данных соединен с входом данных блока сверхоперативной буферной памяти группа входов селектора кодов защиты является группой входов кодов защиты процессоров устройства, вход селектора кодов защиты является канал ным входом кодов защиты устройства, выход селектора кодов защиты соединен с входом регистра кодов защиты, выход которого соединен с входом кода защиты новых данных матрицы кодов защиты и входом кода защиты запроса блока анализа, вход считанных кодов защиты которого соединен с выходом матрицы кодов защиты, вход адреса запроса - с входами нового адреса матрицы адресов и блока коррекции, вход операции чтения с третьим выходом первого дешифратора, выход ошибки адреса является выходом устройства, а выходы сравнения соединены с входами первого 72k элемента ИЛИ, .выход которого является выходом наличия информации устройства и соединен с первыми входами первого и второго элементов И, второй вход второго элемента И соединен с третьим выходом регистра иденуификаторое буферной памяти. 2. Устройство по п. 1, о т л и чаю щ«е е с я тем, что блок анализа содержит первую группу из m (m - целое число).элементов И, вторые и первые входы которых соединены соответственно с выходами уи блоков свертки по модулю два кодов защиты и с выходами уу схем сравнения кодов защиты, первые входы которых объединены и являются входом кода, защиты запроса блока, а вторые входы соединены с входами блоков свертки по модулю два кодов защиты и являются входом считанных кодов защиты блока, вторую группу из ; элементов И, выходы которых являются выходом сравнения блока, первые и вторые входы соединены соответственно с выходами П блоков свертки по модулю два адресов и с выходами Wi схем сравнения адресов, первые входы которых соединены с входами блоков свертки по модулю два адресов и являются входом считанных адресов блока, а вторые входы объединены и являются входом адреса запроса блока,m элементов ИЛИ, выходы которых соединены с соответствуюлдими третьими входами элементов И второй группы, первые входы соединены с выходами элементов И первой группы, а вторые входы объединены и являются входом операции чтения блока, элемент И, кп входов которого соединены с соответствующими первыми входами элементов И второй группы, а выход - с входом элемента НЕ, выход которого является выходом ошибки адреса блока. 3. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок управления записью новых данных содержит три элемента НЕ, четыре триггера, два элемента ИЛИ, уетыре элемента И, причем вход четвертого такта блока соединен с установочным входом первого триггера и первым входом первого элемента И, второй вход которого соединен с выходом первого триггера и входом третьего элемента НЕ, информационный вход первого три|- гера соединен с входом первого эле25

мента НЕ и с входом бита изменения замещаемого слова блока, выход первого элемента НЕ соединен с первым входом четвертого элемента И, второй вход которого соединен с входом операции перезаписи блока и с информационным входом второго триггера, установочный вход которого сое динен с установочным входом третьего триггера и выходом второго элемента НЕ, вход которого является входом продолжительности длинной операции блока, информационный вход третьего триггера является входом операции записи блока, а выход - выходом бита изменения активного блока, вход переполнения блока соединен с первым входом второго элемента И, второй вход которого соединен с третьим входом первого элемента И и первым входом третьего элемента И и выходом второго триггера, выход третьего эле мента НЕ соединен с третьим и вторым входами второго и третьего элементов И соответственно, выход третьего, элемента И является выходом записи

8009726

блока, выход первого элемента И соединен с первыми входами первого и второго элементов ИЛИ, выход второго элемента И соединен с вторым входом 5 первого элемента ИЛИ, выход которого соединен с входом четвертого триг гера, выход последнего является выходом записи адреса блока выход четвертого элемента И соединен с

10 вторым входом второго элементэ ИЛИ, выход которого является выходом конца операции блока.

Источники информации, принятые во внимание при экспертизе

1.Патент Великобритании (Г 13702191 кл. G « А, опублик. IS.

2.Авторское свидетельство СССР № , кл. G 06 F 13/06, 1979 (прототип).

3.Авторское свидетельство СССР № , кл. G 06 F 13/06, 1979.

Ц, Авторское свидетельство СССР по заявке Н 29l23 3/l8-2lt, кл. F 11/22, 1980.

80 79

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Устройство сопряжения контролируемого процессора с основной памятью | 1980 |

|

SU877550A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

0fff.2

вг dfr

ff

ffZ.J

гго

90

flff

fV/

/2У

гг4

fe

f

Sff

//y

fjff

ff.

т т 7ffi Чтение л ifff efW/ jff ffHtar JSfffTpOC CS/7 .7 Sa eoffjffiffffewmiwAoeff ffjfffaf /VKfyffff/XMfffoffmaf

Авторы

Даты

1982-12-07—Публикация

1981-06-05—Подача