(54) УСТРОЙСТВО ДЛЯ СОРТИРОВКИ ДАННЫХ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки данных | 1973 |

|

SU486316A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2025796C1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Запоминающее устройство | 1989 |

|

SU1711229A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Ассоциативное запоминающее устройство | 1984 |

|

SU1234880A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1080213A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1996 |

|

RU2107955C1 |

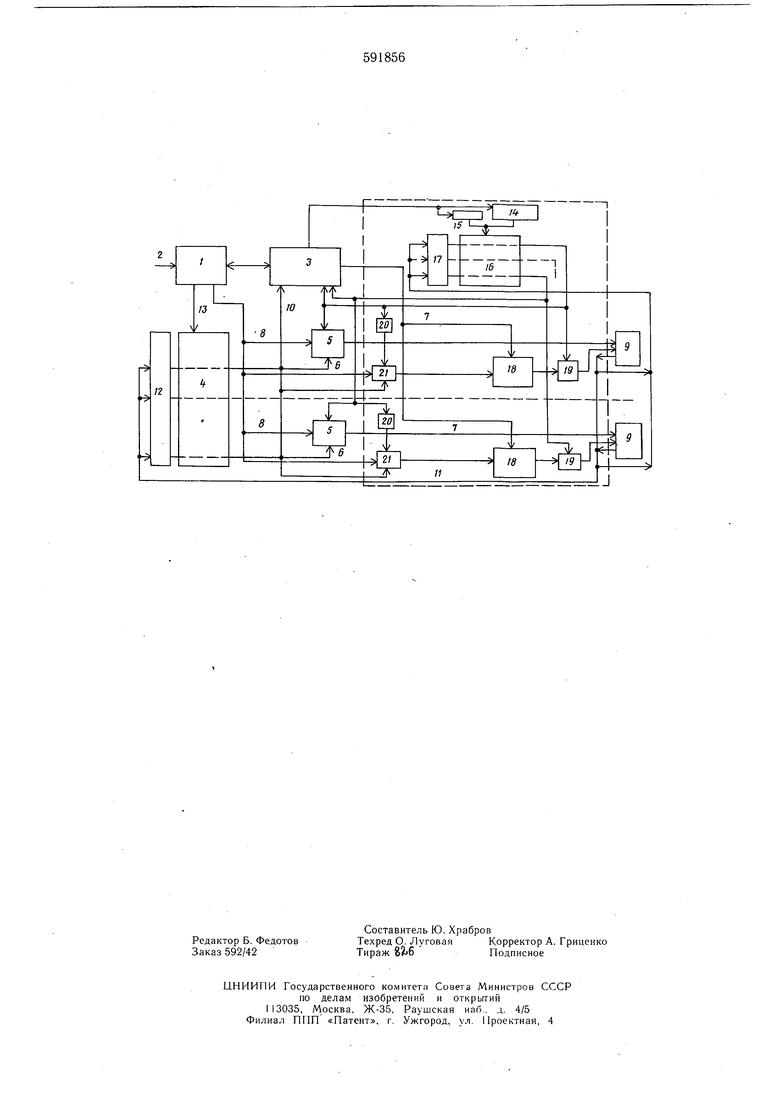

Изобретение относится к вычислительной технике. Известно устройство для сортировки данных 1. Это устройство не может сортировать по заданным моментам времени при упорядоченном во времени поступлении данных разного характера в запоминающие блоки. Цель изобретения - повышение гибкости работы устройства при сортировке по заданным моментам времени. Поставленная цель достигается тем, что в устройство введены генератор, регистр, блок ассоциативной памяти, узел записи, две группы элементов И, группу элементов НЕ, группу блоков буферной памяти, причем входы и выходы генератора и регистра соединены соответственно с выходом блока управления и управляющим входом блока ассоциативной памяти, входы которого через узел записи соединены с выходами запоминающих блоков; выходы блока ассоциативной памяти соединены со входами блока управления, ключевых элементов с первыми входами элементов И первой группы и через элементы НЕ группы - с первыми входами элементов И второй группы, выходы которых через блоки буферной памяти группы соединены со вторыми входами элементов И первой группы, которых соединены со входами запоминающих блоков. Вторые и третьи входы элементов И второй группы соединены с выходами соответственно буферного запоминающего блока и ассоциативного запоминающего блока, входы блоков буферной памяти группы соединены с выходом блока управления. На чертеже приведена структурная электрическая схема устройства. Устройство содержит буферный запоминающий блок 1, в котором запоминается поступающий по входному каналу 2 пакет данных, блок 3 управления, ассоциативный запоминающий блок 4 (параллельного действия), ключевые элементы 5 по количеству запоминающих ячеек блока 4, одни входы которых подключены к выходам 6 соответствующих ячеек блока 4, а выходы 7 и другие входы 8 - соответственно к запоминающим блслам 9 и выходу блока 1. Выходы ячеек блока 4 связаны каналом 10 с блоком управления 3. Выходы блоков 9 соединены кана.юм 11 со входами блока записи 12. По каналу 13 из блока 1 в блок 4 поступают слова для опроса. Устройство также содержит генератор 14, регистр 15, блок 16 ассоциативной памяти. узел 17 записи, блоки 18 буферной памяти, элементы И 19 первой группы, элементы НЕ 20, элементы И 21 второ-й группы. Устройство работает следуюш,им образом. По каналу 2 поступает очередной пакет данных. Блок 3 управляет приемом пакета и пословно записывает его в блок 1. С окончанием приема каждое слово из блока 1 направляется для опроса в блок 4, одновременно по сигналу с блока 3 код из регистра 15 направляется, в блок 16. Если на одном или нескольких выходах ячеек блока 4 появляется сигнал совпадения, он по каналу 10 поступает в блокЗ, управляюихий выдачей из блока 1 всего пакета данных в ключевые элементы 5 и эле.менты И 21. Одновременно сигналы из блока 4 подготавливают к открыванию по выходам 6 соответствующие ключевые элементы 5 и элементы И 21. При этом открываются только те ключевые элементы, на которые с ячеек блока 16 поступает сигнал совпадения от опроса по условному коду. Тот же сигнал совпадения через эле.менты НЕ 20 закрывает соответствующие элементы И 21. Те из них, на которые поступил сигнал совпадения с запоминающих блоков 4 и 16, открываются. Пакет данных из запоминающего блока 1 через открытые ключевые элементы 5 поступает в соответствующие запоминающие блоки 9., а через открытые элементы И 21 - в соответствующие им блоки 18 буферной па.мяти. Таким образом, из каждой пары ключевых элементов 5 и элементов И 21, подключенных к одним и тем же выходам ячеек блока 16, одновре.менно может быть открыт только один эле.мент, а пакет данных может поступить или только в блок 9, или только в блок 18. При этом в каждом из блоков 18 могут накапливаться данные определенного характера. Генератор 14 с установленным интервалом г и установленной точностью ff, которые можно регулировать, выдает в блок 16 для опроса реальные .мо.менты времени. Сигналы совпадения на выходах ячеек блока 16 открывают соответствующие эле.менты И 19; при этом блок 3 управляет выдачей данных из блоков 18 буферной па.мяти через открытые эле.менты И 19 в запоминающие блоки 9. Сигнал считывания вырабатывается блоком 3 управления только при поступлении сигнала совпадения с блока 16 и отсутствии сигнала совпадения с блока 4. Блок 3 синхронизирует работу генератора 14 и регистра 15, исключая одновремеппую выдачу опросов в блок 16. Коды моментов времени записываются в ячейки блока 16 узлами 17, куда поступают с блоков 9. Для каждого из блоков 18 (или блоков 9) число различных моментов выдачи, заранее записываемых в блок 16, равно числу запоминающих ячеек блока 16, запараллельных на выходе и подключенных к соответствующему эле.менту И 19. Устройство позволяет быстро и просто реализовать и перестраивать различные процессы сортировки (распределения) по заданным моментам времени данных различного характера в соответствующие им запоминающие блоки, что необходимо при обработке данных в вычислительных комплексах автоматизированных систем управления как при аппаратном, так и при программном путях реализации различных процессов функционирования вычислительных комплексов, и особенно при реализации процессов выдачи данных на оконечные устройства системы и в каналы связи. Формула изобретения Устройство для сортировки данных по авт. св. № 486316, отличающееся тем, что с целью повыщения гибкости, в него введены генератор, регистр, блок ассоциативной памяти, узел записи, две группы элементов И, группу элементов НЕ, группу блоков буферной памяти, причем входы и выходы генератора и регистра соединены соответственно с выходом блока управления и управляющим входом блока ассоциативной памяти, входы которого через узел записи соединены с выходами запоминающих блоков, выходы блока ассоциативной памяти соединены со входами блока управления, ключевых схем, с первыми входами элементов И первой группы и через элементы НЕ группы с первыми входами элементов И второй группы, выходы которых через блоки буферной памяти группы соединены со вторыми входами элементов И первой группы, выходы которых соединены со входами запоминающих блоков, вторые и третьи входы элементов И второй группы соединены с выходами соответственно буферного запоминающего блока и ассоциативного запоминающего блока, входы блоков буферной памяти группы соединены с выходом блока управления. Источники информации, принятые во внимание при экспертизе: 1. Авторское свидетельство СССР № 486316, кл. G 06 F 7/06, 1973.

Авторы

Даты

1978-02-05—Публикация

1976-10-19—Подача