и ю

Изобретение относится к вычислительной технике и может быть использовано при построении безадресной буферной памяти в устройствах с потоковой обработкой информации.

Цель изобретения - упрощение устройства и повышение быстродействия.

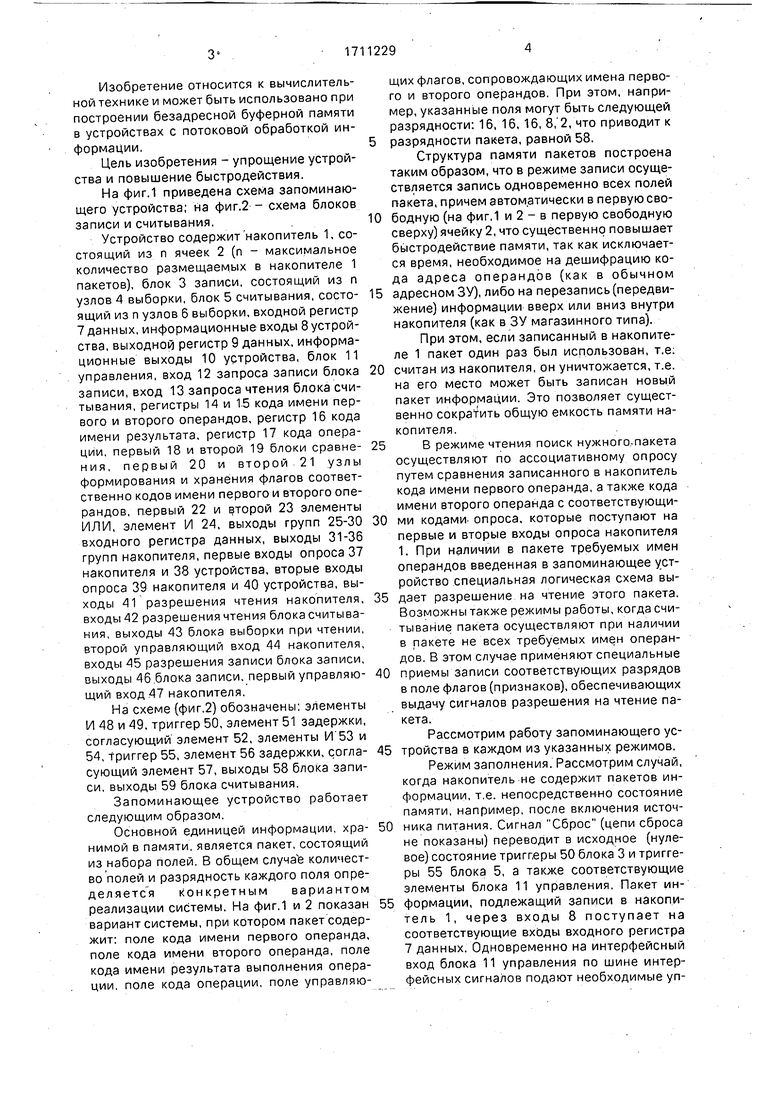

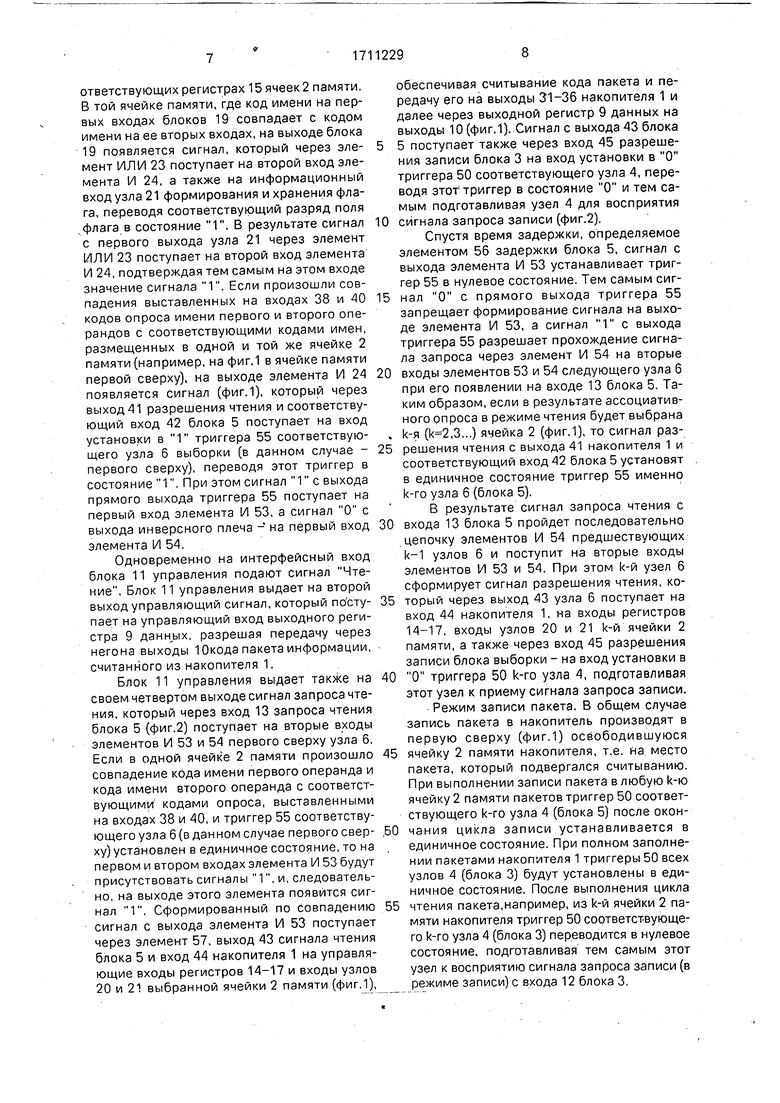

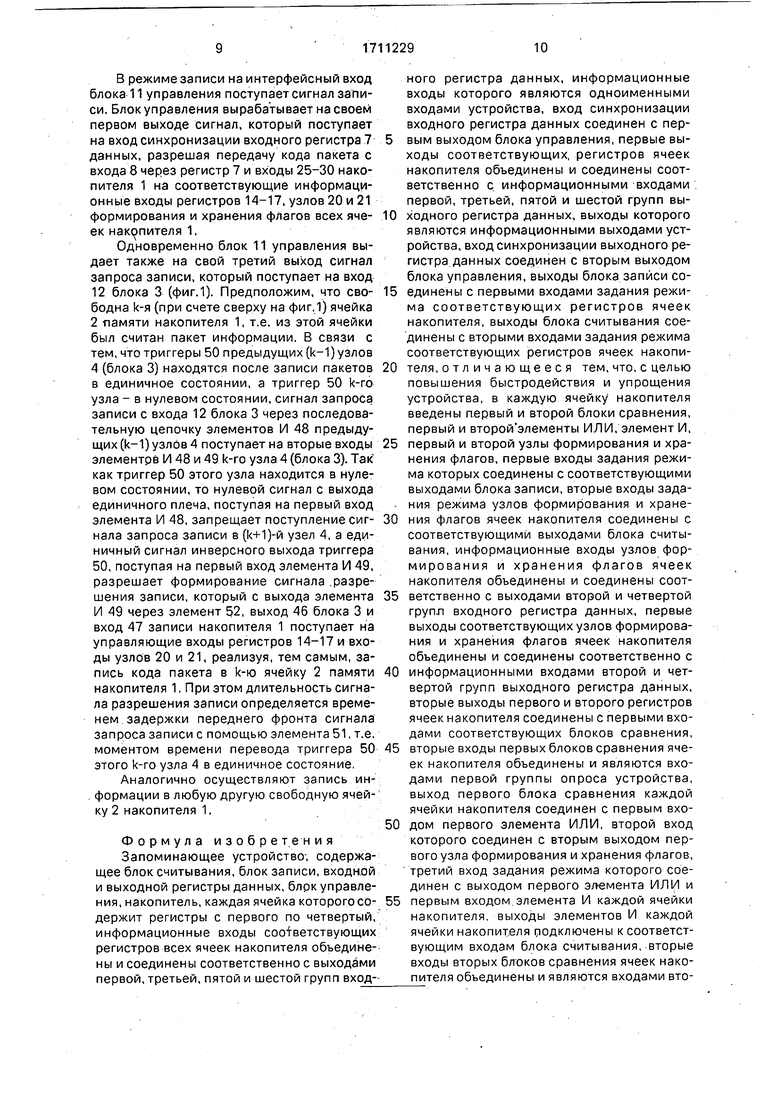

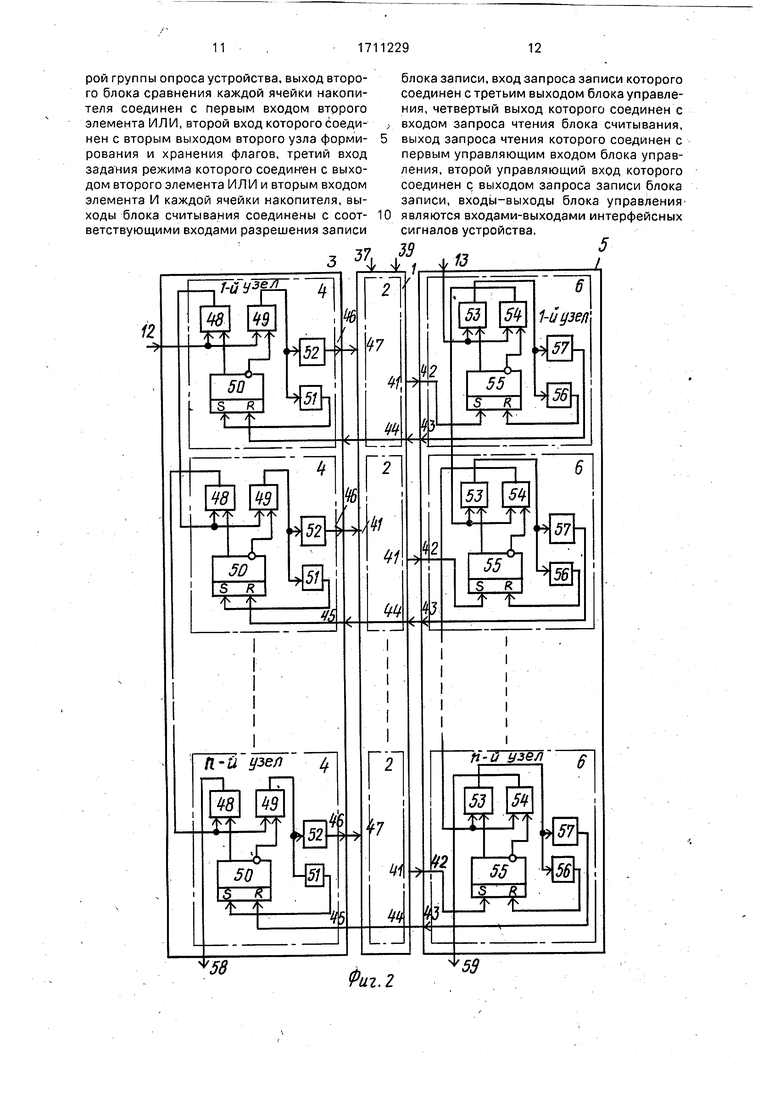

На фиг.1 приведена схема запоминающего устройства; на фиг.2 - схема блоков записи и считывания.

Устройство содержит накопитель 1, состоящий из п ячеек 2 (п - максимальное количество размещаемых в накопителе 1 пакетов), блок 3 записи, состоящий из п узлов 4 выборки, блок 5 считывания, состоящий из п узлов 6 выборки, входной регистр 7 данных, информационные входы 8 устройства, выходной регистр 9 данных, информационные выходы 10 устройства, блок 11 управления, вход 12 запроса записи блока записи, вход 13 запроса чтения блока считывания, регистры 14 и 15 кода имени первого и второго операндов, регистр 16 кода имени результата, регистр 17 кода операции, первый 18 и второй 19 блоки сравнения, первый 20 и второй 21 узлы формирования и хранения флагов соответственно кодов имени первого и второго операндов, первый 22 и второй 23 элементы ИЛИ, элемент И 24, выходы групп 25-30 входного регистра данных, выходы 31-36 групп накопителя, первые входы опроса 37 накопителя и 38 устройства, вторые входы опроса 39 накопителя и 40 устройства, выходы 41 разрешения чтения накопителя, входы 42 разрешения чтения блока считывания, выходы 43 блока выборки при чтении, второй управляющий вход 44 накопителя, входы 45 разрешения записи блока записи, выходы 46.блока записи, первый управляющий вход 47 накопителя.

На схеме (фиг.2) обозначены: элементы И 48 и 49, триггер 50, элемент 51 задержки, согласующий элемент 52, элементы И 53 и 54, триггер 55, элемент 56 задержки, согласующий элемент 57, выходы 58 блока записи, выходы 59 блока считывания.

Запоминающее устройство работает следующим образом.

Основной единицей информации, хранимой в памяти, является пакет, состоящий из набора полей, В общем случае количество полей и разрядность каждого поля определяется конкретным вариантом реализации системы. На фиг.1 и 2 показан вариант системы, при котором пакет содержит: поле кода имени первого операнда, поле кода имени второго операнда, поле кода имени результата выполнения операции, поле кода операции, поле управляющих флагов, сопровождающих имена первого и второго операндов. При этом, например, указанные поля могут быть следующей разрядности: 16, 16, 16, 8,2, что приводит к

разрядности пакета, равной 58.

Структура памяти пакетов построена таким образом, что в режиме записи осуществляется запись одновременно всех полей пакета, причем автоматически в первую сво0 бодную (на фиг.1 и 2 - в первую свободную сверху) ячейку 2, что существенно повышает быстродействие памяти, так как исключается время, необходимое на дешифрацию кода адреса операндов (как в обычном

5 адресном ЗУ), либо на перезапись (передвижение) информации вверх или вниз внутри накопителя (как в ЗУ магазинного типа).

При этом, если записанный в накопителе 1 пакет один раз был использован, т.е:

0 считан из накопителя, он уничтожается, т.е. на его место может быть записан новый пакет информации. Это позволяет существенно сократить общую емкость памяти накопителя.

5В режиме чтения поиск нужного-пакета

осуществляют по ассоциативному опросу путем сравнения записанного в накопитель кода имени первого операнда, а также кода имени второго операнда с соответствующи0 ми кодами- опроса, которые поступают на первые и вторые входы опроса накопителя 1. При наличии в пакете требуемых имен операндов введенная в запоминающее устройство специальная логическая схема вы5 дает разрешение на чтение этого пакета. Возможны также режимы работы, когда считывание пакета осуществляют при наличии в пакете не всех требуемых имен операндов. В этом случае применяют специальные

0 приемы записи соответствующих разрядов в поле флагов (признаков), обеспечивающих выдачу сигналов разрешения на чтение пакета.

Рассмотрим работу запоминающего ус5 тройства в каждом из указанных режимов. Режим заполнения. Рассмотрим случай, когда накопитель не содержит пакетов информации, т.е. непосредственно состояние памяти, например, после включения источ0 ника питания. Сигнал Сброс (цепи сброса не показаны) переводит в исходное (нулевое) состояние триггеры 50 блока 3 и триггеры 55 блока 5, а также соответствующие элементы блока 11 управления. Пакет ин5 формации, подлежащий записи в накопитель 1, через входы 8 поступает на соответствующие входы входного регистра 7 данных. Одновременно на интерфейсный вход блока 11 управления по шине интерфейсных сигналов подают необходимые управняющие сигналы. Шина интерфейсных сигналов содержит управляющие сигналы (чтение-запись, обращение и т.д.), поступающие на вход блока управления, и сигналы, поступающие на входы процессора (сигнал окончания цикла, сигнал занятости и т.д.): Блок 11 управления вырабатывает управля- .. ющий сигнал, который с его первого выхода поступает на управляющий вход регистра 7, разрешая передачу пакета информации с входа 8 через соответствующие входы 25- 30 накопителя 1 на одноименные информационные входы соответствующих регистров 14-17, узлов 20 и 21 формирования и хранения флагов всех ячеек 2 памяти накопителя 1. Одновременно блок 11 управления вырабатывает управляющий сигнал запроса записи, который с третьего выхода этого блока через вход 12 запроса записи блока 3 поступает на вторые входы первого 48 и второго 49 элементов И первого (на фиг.1 и 2 самого , верхнего) узлы 4. Так как триггер 50 нахо7, дится в нулевом состоянии, то происходит совпадение двух сигналов на первом и втором входах элемента И 49..,

Сформированный элементом И 49 вы- хдцной сигнал поступает через элемент 52 на выход 46 сигнала записи блока 3 и далее через адресный вход 47 записи накопителя Л- на управляющие входы регистров 14-17, а также на.управляющие входы узлов 20 и 21 формирования и хранения флагов (фиг.1), реализуя тем самым запись пакета в первую ячейку 2 памяти накопителя (на фиг.1 и 2 - первую ячейку памяти сверху) хранения пакетов накопителя 1. При этом длительность сигнала записи, поступающего на вход 47, определяется длительностью сигнала запроса записи на втором входе элемента И 49 и промежутком времени от переднего фронта этого сигнала до момента установки триггера 50 в состояние 1 (фиг.2). В это состояние триггер 50 переводит сигнал, поступающий на вход установки в 1 с вых ода элемента И 49 через элемент 51 задержки. Тем самым с помощью элемента 51 задержки можно выбрать требуемую длительность сигнала разрешения записи.

Сигналы на выходах триггера 50 после установки его в состояние 1 запрещают прохождение сигнала через второй элемент И 49 и разрешают прохождение сигнала записи с входа 12 запроса записи блока 3 через элемент И 48 первого узла 4 на вторые входы элементов 48 и 49 следующего (в,то- рого сверху) узла 4.

Запись второго пакета осуществляют в следующую (на фиг.1 и 2 вторую сверху) ячейку 2 памяти хранения пакетов.

Аналогично выполняют запись в накопитель 1 третьего, четвертого и т.д. пакетов информации, причем при записи n-го пакета сигнала запроса записи с входа 12 блока 3

проходит последовательно (п-1) элементов И 48 и поступает на вторые входы элементов И 48 и 49 n-го узла блока 3. После перевода триггера 50 n-го узла в единичное состояние сигналом с выхода элемента И 49 сигнал с

0 выхода элемента И 48 этого блока через выход 58 блока 3 поступает на второй вход блока 11 управления, указывая на окончание заполнения всего накопителя 1 пакетами информации.

5 В режиме записи пакета информации блок 11 управления сигнал запроса чтения не вырабатывает, при этом.триггеры 55 всех узлов 6 блока 5 после действия сигнала сброса находятся в нулевом состоянии. В

0 результате сигнал разрешения чтения от- сутствует на управляющих входах регистров 14-17 и входах узлов 20 и 21, и поэтому чтение пакетов информации при реализации режима записи не происходит. При слу5 чайном появлении сигнала запроса чтения

на входе 13 блока 5 этот сигнал проходит

через все п элементов И 54 на выход 59 и

далее в блок 11 управления, подтверждая

. режим записи.

0 Режим чтения. В этом режиме на вход 38 подают код опроса имени первого операнда, который через вход 37 накопителя 1 поступает параллельно (по столбцу) на вторые входы блоков 18 сравнения всех ячеек

5 2 памяти накопителя 1. На первые входы этих же блоков 18 сравнения поступают коды имени операндов, находящихся в соответствующих регистрах 14 ячеек 2 памяти. В той ячейке 2 памяти, где код имени на

0 первых входах блока 18 совпадает с кодом имени на ее вторых входах, на выходе блока 18 появляется сигнал, который через элемент ИЛИ 22 поступает на первый вход элемента И 24, а также на информационный

5 вход узла 20 формирования и хранения флагов, переводя соответствующий разряд флага в состояние 1. Далее это значение разряда флага поступает с первого выхода узла 20 через элемент ИЛИ 22 на первый

Q вход элемента И 24, подтверждая тем самым на этом входе значение сигнала 1.

Одновременно (или с соответствующим сдвигом во времени) на вход 40 подают код опроса имени второго операнда, который

5 через входы 39 опроса имени накопителя 1 поступает параллельно (по столбцу) на вторые входы блоков 19 сравнения всех ячеек 2 памяти хранения пакетов. На первые входы этих же блоков 19 сравнения поступают коды имени операндов, находящихся в соответствующих регистрах 15 ячеек 2 памяти, В той ячейке памяти, где код имени на первых входах блоков 19 совпадает с кодом имени на ее вторых входах, на выходе блока

19появляется сигнал, который через эле- мент ИЛИ 23 поступает на второй вход элемента И 24, а также на информационный вход узла 21 формирования и хранения флага, переводя соответствующий разряд поля флага в состояние 1, В результате сигнал с первого выхода узла 21 через элемент ИЛИ 23 поступает на второй вход элемента

И 24, подтверждая тем самым на этом входе значение сигнала 1. Если произошли совпадения выставленных на входах 38 и 40 кодов опроса имени первого и второго операндов с соответствующими кодами имен, размещенных в одной и той же ячейке 2 памяти (например, на фиг.1 в ячейке памяти первой сверху), на выходе элемента И 24 появляется сигнал (фиг.1), который через выход 41 разрешения чтения и соответствующий вход 42 блока 5 поступает на вход установки в 1 триггера 55 соответствующего узла 6 выборки (в данном случае - первого сверху), переводя этот триггер в состояние 1. При этом сигнал 1 с выхода прямого выхода триггера 55 поступает на первый вход элемента И 53, а сигнал О с выхода инверсного плеча - на первый вход элемента И 54.

Одновременно на интерфейсный вход блока 11 управления подают сигнал Чтение. Блок 11 управления выдает на второй выход управляющий сигнал, который по сту- пает.на управляющий вход выходного регистра 9 данных, разрешая передачу через негона выходы Юкода пакета информации, считанного из накопителя 1.

Блок 11 управления выдает также на своем четвертом выходе сигнал запроса чтения, который через вход 13 запроса чтения блока 5 (фиг.2) поступает на вторые входы элементов И 53 и 54 первого сверху узла 6. Если в одной ячейке 2 памяти произошло совпадение кода имени первого операнда и кода имени второго операнда с соответствующими кодами опроса, выставленными на входах 38 и 40, и триггер 55 соответствующего узла 6 (в данном случае первого свер- ху)установлен в единичное состояние, то на первом и втором входах элемента И 53 будут присутствовать сигналы 1, и, следовательно, на выходе этого элемента появится сигнал 1. Сформированный по совпадению сигнал с выхода элемента И 53 поступает через элемент 57, выход 43 сигнала чтения блока 5 и вход 44 накопителя 1 на управляющие входы регистров 14-17 и входы узлов

20и 21 выбранной ячейки 2 памяти (фиг.1),

обеспечивая считывание кода пакета и передачу его на выходы 31-36 накопителя 1 и далее через выходной регистр 9 данных на выходы 10 (фиг, 1). Сигнал с выхода 43 блока 5 поступает также через вход 45 разрешения записи блока 3 на вход установки в О триггера 50 соответствующего узла 4, переводя этот1 триггер в состояние О и тем самым подготавливая узел 4 для восприятия сигнала запроса записи (фиг.2).

Спустя время задержки, определяемое элементом 56 задержки блока 5, сигнал с выхода элемента И 53 устанавливает триггер 55 в нулевое состояние. Тем самым сигнал О с прямого выхода триггера 55 запрещает формирование сигнала на выходе элемента И 53, а сигнал 1 с выхода триггера 55 разрешает прохождение сигнала запроса через элемент И 54 на вторые входы элементов 53 и 54 следующего узла 6 при его появлении на входе 13 блока 5. Таким образом, если в результате ассоциативного опроса в режиме чтения будет выбрана k-я (,3...) ячейка 2 (фиг.1), то сигнал разрешения чтения с выхода 41 накопителя 1 и соответствующий вход 42 блока 5 установят в единичное состояние триггер 55 именно k-ro узла 6 (блока 5).

В результате сигнал запроса чтения с входа 13 блока 5 пройдет последовательно цепочку элементов И 54 предшествующих k-1 узлов 6 и поступит на вторые входы элементов И 53 и 54. При этом k-й узел 6 сформирует сигнал разрешения чтения, который через выход 43 узла 6 поступает на вход 44 накопителя 1, на входы регистров 14-17, входы узлов 20 и 21 k-й ячейки 2 памяти, а также через вход 45 разрешения записи блока выборки - на вход установки в О триггера 50 k-ro узла 4, подготавливая этот узел к приему сигнала запроса записи.

Режим записи пакета. В общем случае запись пакета в накопитель производят в первую сверху (фиг.1) освободившуюся ячейку 2 памяти накопителя, т.е. на место пакета, который подвергался считыванию. При выполнении записи пакета в любую k-ю ячейку 2 памяти пакетов триггер 50 соответствующего k-ro узла 4 (блока 5) после окончания цикла записи устанавливается в единичное состояние. При полном заполнении пакетами накопителя 1 триггеры 50 всех узлов 4 (блока 3) будут установлены в единичное состояние. После выполнения цикла чтения пакета,например, из k-й ячейки 2 памяти накопителя триггер 50 соответствующего k-ro узла 4 (блока 3) переводится в нулевое состояние, подготавливая тем самым этот узел к восприятию сигнала запроса записи (в режиме записи) с входа 12 блока 3.

В режиме записи на интерфейсный вход блока 11 управления поступает сигнал записи. Блок управления вырабатывает на своем первом выходе сигнал, который поступает на вход синхронизации входного регистра 7 данных, разрешая передачу кода пакета с входа 8 через регистр 7 и входы 25-30 накопителя 1 на соответствующие информационные входы регистров 14-17, узлов 20 и 21 формирования и хранения флагов всех ячеек накопителя 1,

Одновременно блок 11 управления выдает также на свой третий выход сигнал запроса записи, который поступает на вход 12 блока 3 (фиг.1). Предположим, что свободна k-я (при счете сверху на фиг.1) ячейка 2 памяти накопителя 1, т.е. из этой ячейки был считан пакет информации. В связи с тем, что триггеры 50 предыдущих (к-1) узлов 4 (блока 3) находятся после записи пакетов в единичное состоянии, а триггер 50 к-го узла - в нулевом состоянии, сигнал запроса записи с входа 12 блока 3 через последовательную цепочку элементов И 48 предыдущих (к-1) узлов 4 поступает на вторые входы элементрб И 48 и 49 k-го узла 4 (блока 3). Так как триггер 50 этого узла находится в нулевом состоянии, то нулевой сигнал с выхода единичного плеча, поступая на первый вход элемента И 48, запрещает поступление сигнала запроса записи в ()-й узел 4, а единичный сигнал инверсного выхода триггера 50, поступая на первый вход элемента И 49, разрешает формирование сигнала .разрешения записи, который с выхода элемента И 49 через элемент 52, выход 46 блока 3 и вход 47 записи накопителя 1 поступает на управляющие входы регистров 14-17 и входы узлов 20 и 21, реализуя, тем самым, запись кода пакета в к-ю ячейку 2 памяти накопителя 1. При этом длительность сигнала разрешения записи определяется временем . задержки переднего фронта сигнала запроса записи с помощью элемента 51, т.е. моментом времени перевода триггера 50 этого k-го узла 4 в единичное состояние,

Аналогично осуществляют запись ин- , формации в любую другую свободную ячейку 2 накопителя 1.

Формула изобретения Запоминающее устройство; содержащее блок считывания, блок записи, входной и выходной регистры данных, блрк управления, накопитель, каждая ячейка которогосо- держит регистры с первого по четвертый, информационные входы соответствующих регистров всех ячеек накопителя объединены и соединены соответственно с выходами первой, третьей, пятой и шестой групп входного регистра данных, информационные входы которого являются одноименными входами устройства, вход синхронизации входного регистра данных соединен с первым выходом блока управления, первые выходы соответствующих, регистров ячеек накопителя объединены и соединены соответственно с информационными входами, первой, третьей, пятой и шестой групп вы0 ходного регистра данных, выходы которого являются информационными выходами устройства, вход синхронизации выходного регистра данных соединен с вторым выходом блока управления, выходы блока записи со5 единены с первыми входами задания режима соответствующих регистров ячеек накопителя, выходы блока считывания соединены с вторыми входами задания режима соответствующих регистров ячеек накопи0 теля, о т л и ч а ю ще е с я тем, что, с целью повышения быстродействия и упрощения устройства, в каждую ячейку накопителя введены первый и второй блоки сравнения, первый и второй элементы ИЛИ, элемент И,

5 первый и второй узлы формирования и хранения флагов, первые входы задания режима которых соединены с соответствующими выходами блока записи, вторые входы зада- ния режима узлов формирования и хране0 ния флагов ячеек накопителя соединены с соответствующими выходами блока считывания, информационные входы узлов формирования и хранения флагов ячеек накопителя объединены и соединены соот5 ветственно с выходами второй и четвертой групл входного регистра данных, первые выходы соответствующих узлов формирования и хранения флагов ячеек накопителя объединены и соединены соответственно с

0 информационными входами второй и четвертой групп выходного регистра данных, вторые выходы первого и второго регистров ячеек накопителя соединены с первыми входами соответствующих блоков сравнения,

5 вторые входы первых блоков сравнения ячеек накопителя объединены и являются входами первой группы опроса устройства, выход первого блока сравнения каждой ячейки накопителя соединен с первым вхо0 дом первого элемента ИЛИ, второй вход которого соединен с вторым выходом первого узла формирования и хранения флагов, третий вход задания режима которого соединен с выходом первого эл-емента ИЛИ и

5 первым входом.элемента И каждой ячейки накопителя, выходы элементов И каждой ячейки накопителя подключены к соответствующим входам блока считывания, вторые входы вторых блоков сравнения ячеек накопителя объединены и являются входами второй группы опроса устройства, выход второго блока сравнения каждой ячейки накопителя соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с вторым выходом второго узла формирования и хранения флагов, третий вход задания режима которого соединен с выходом второго элемента ИЛИ и вторым входом элемента И каждой ячейки накопителя, выходы блока считывания соединены с соответствующими входами разрешения записи

0

блока записи, вход запроса записи которого соединен с третьим выходом блока управления, четвертый выход которого соединен с входом запроса чтения блока считывания, выход запроса чтения которого соединен с первым управляющим входом блока управления, второй управляющий вход которого соединен q выходом запроса записи блока записи, входы-выходы блока управления являются входами-выходами интерфейсных сигналов устройства.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для сопряжения каналов связи с ЭВМ | 1985 |

|

SU1278873A1 |

| Кольцевая пакетная сеть передачи информации | 1987 |

|

SU1555888A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении безадресной буферной памяти в устройствах с потоковой обработкой информации. Цель изобретения - упрощенце устройства и повышение быстродействия. Запоминающее устройство содержит накопитель 1, состоящий из п ячеек 2, блок 3 записи, блок 5 считывания, входной 7 и выходной 9 регистры данных, информационные входы 8 и вы ходы 10, блок 11 управления, регистры 14, 17, блоки 18, 19 сравнения, блоки 20, 21 формирования и хранения флагов, элементы ИЛИ 22,23, элемент И 24, входы 38, 40 опроса. Быстродействие устройства повышается за счет параллельного поиска и ассоциативной выборки нужного пакета в режиме чтения и, во-вторых, за счет того, что в режиме записи все поля пакета записывают одновременно в автоматически выбранную безадресным способом свободную ячейку памяти. 2 ил.

| Запоминающее устройство | 1984 |

|

SU1247946A1 |

| Запоминающее устройство с одновременным считыванием нескольких слов | 1986 |

|

SU1310899A1 |

Авторы

Даты

1992-02-07—Публикация

1989-08-02—Подача