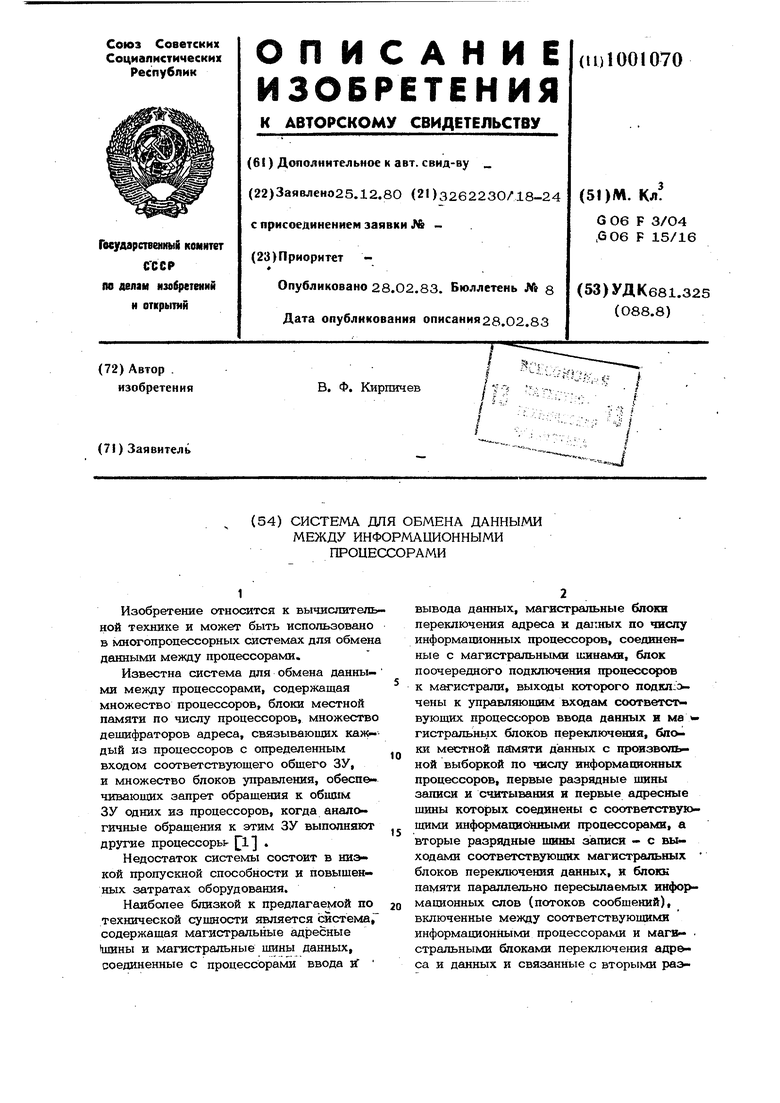

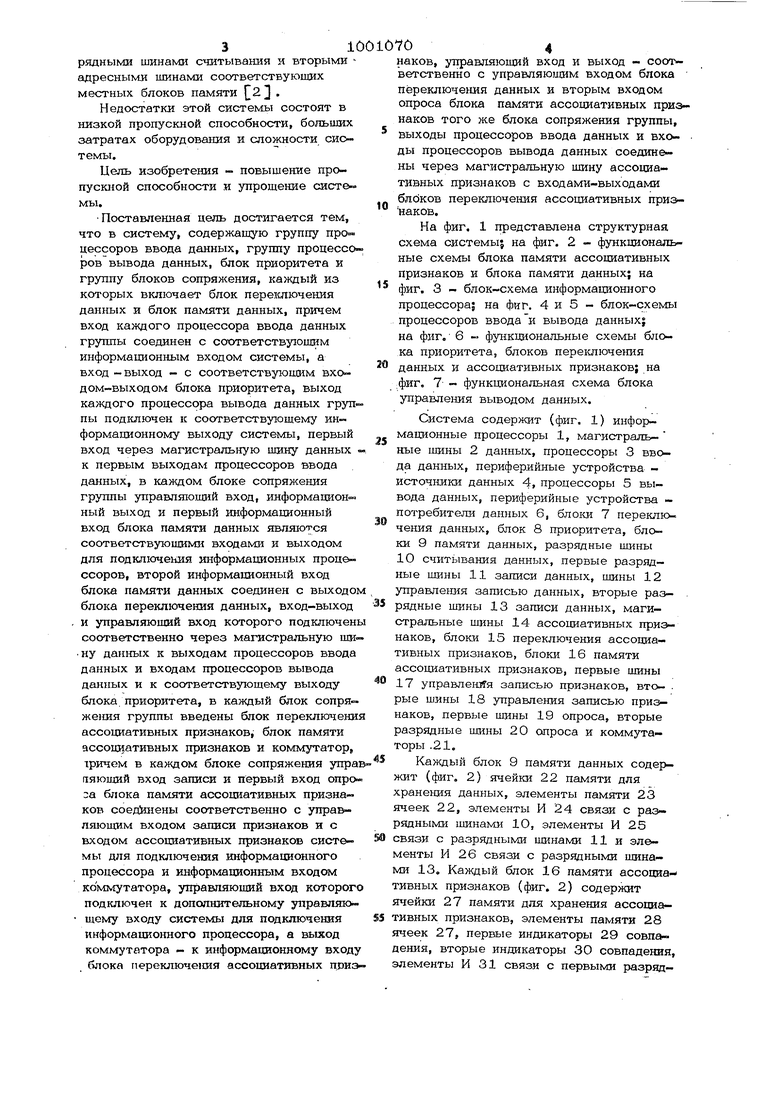

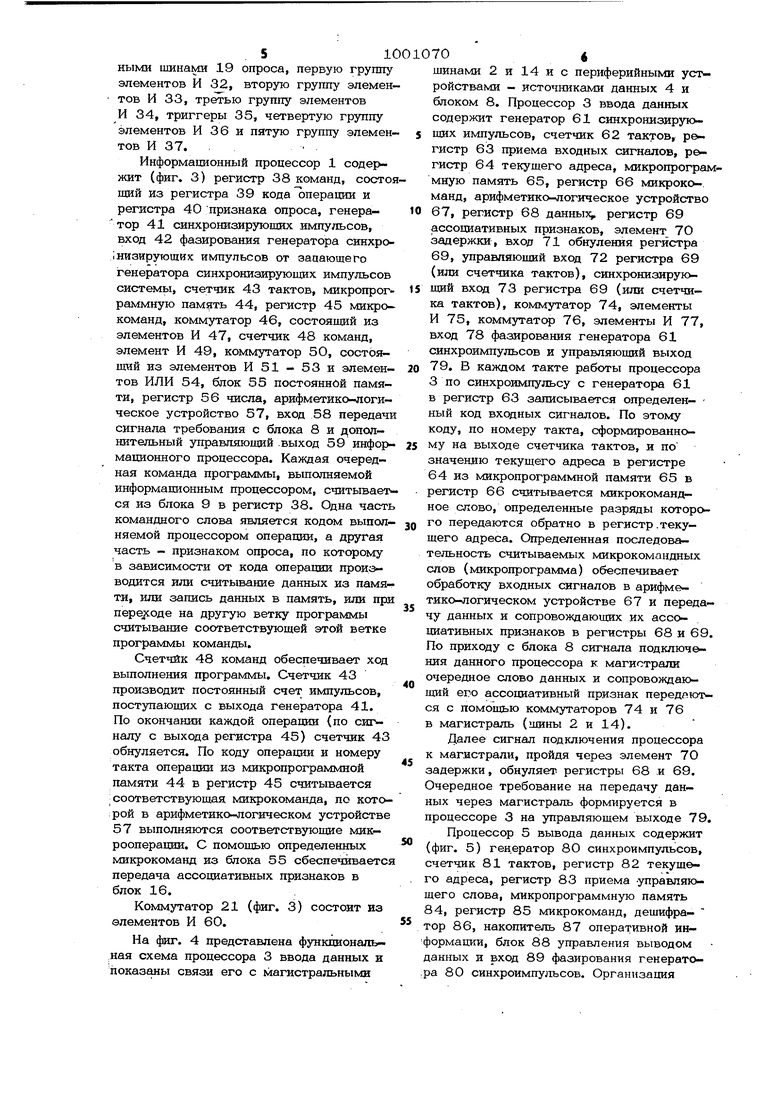

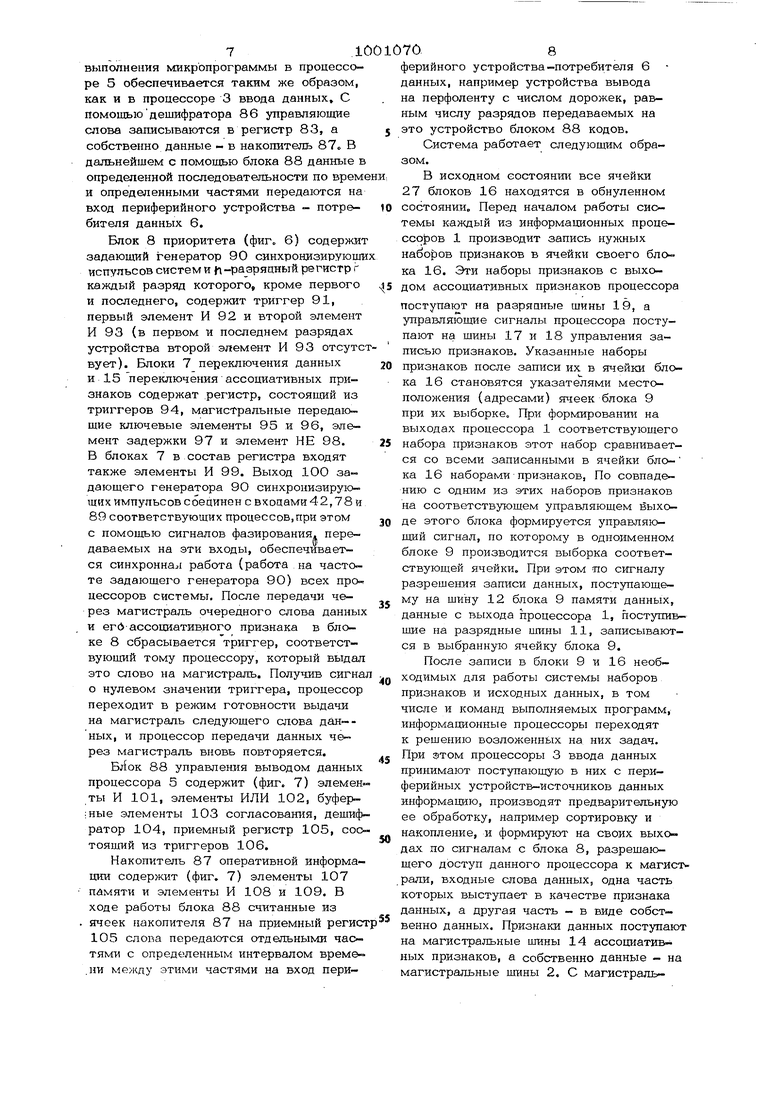

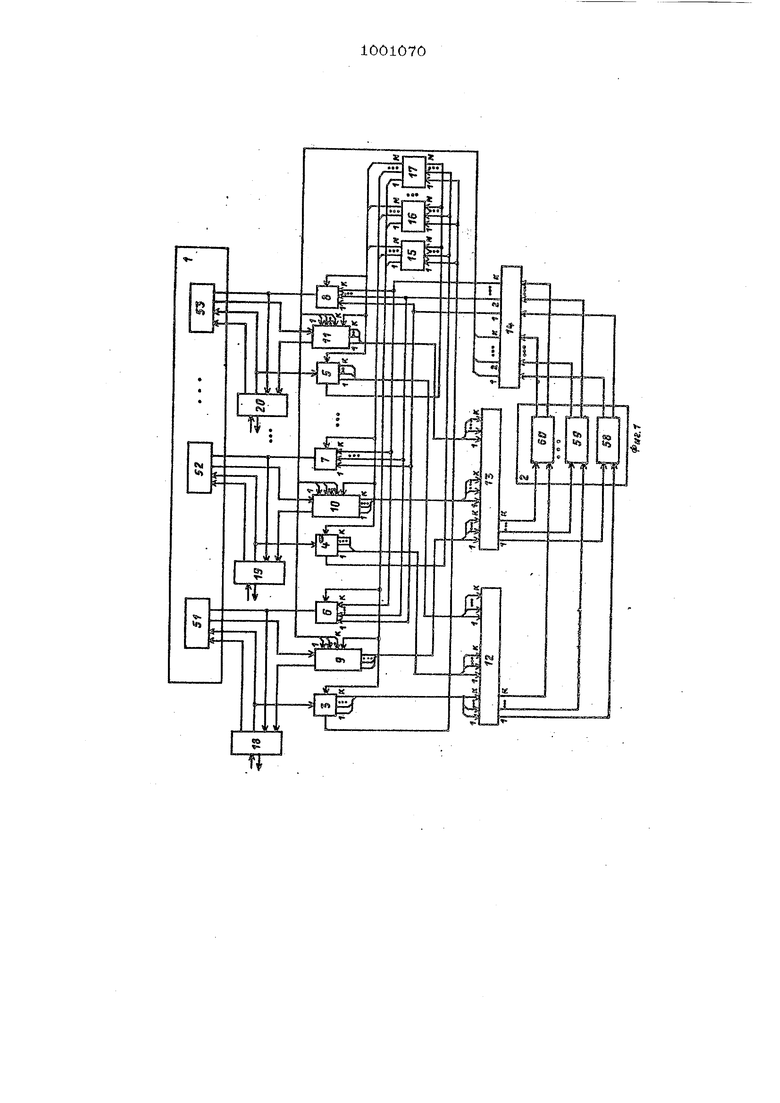

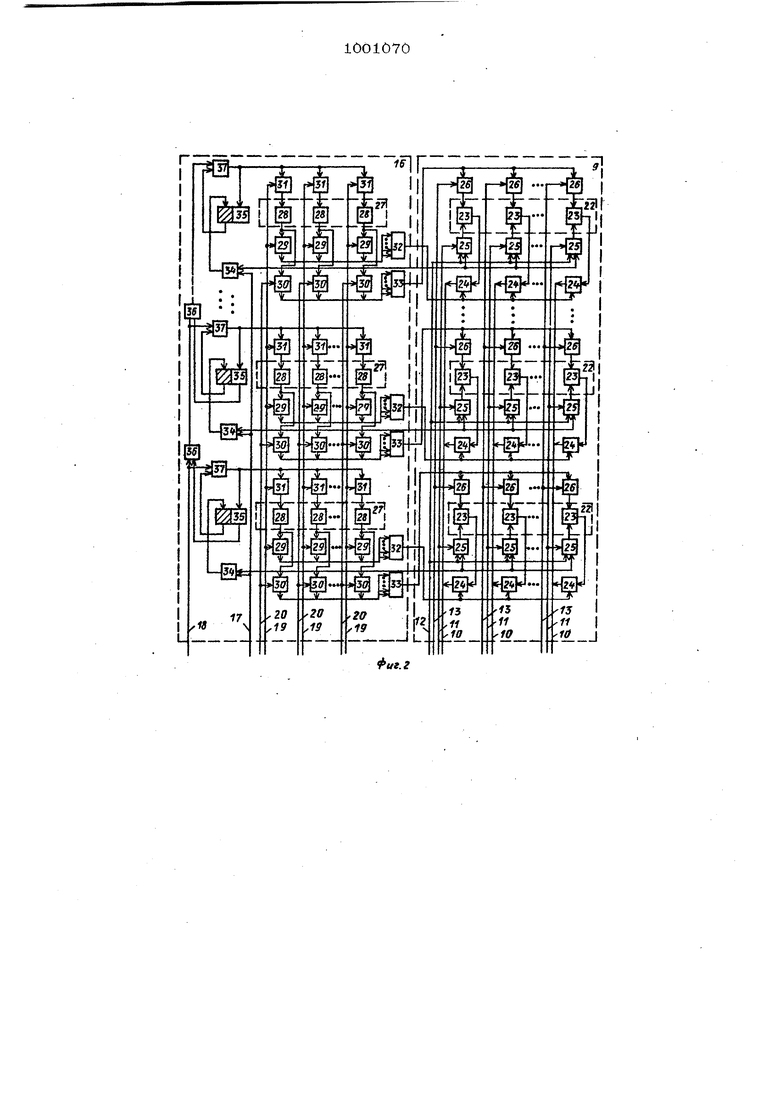

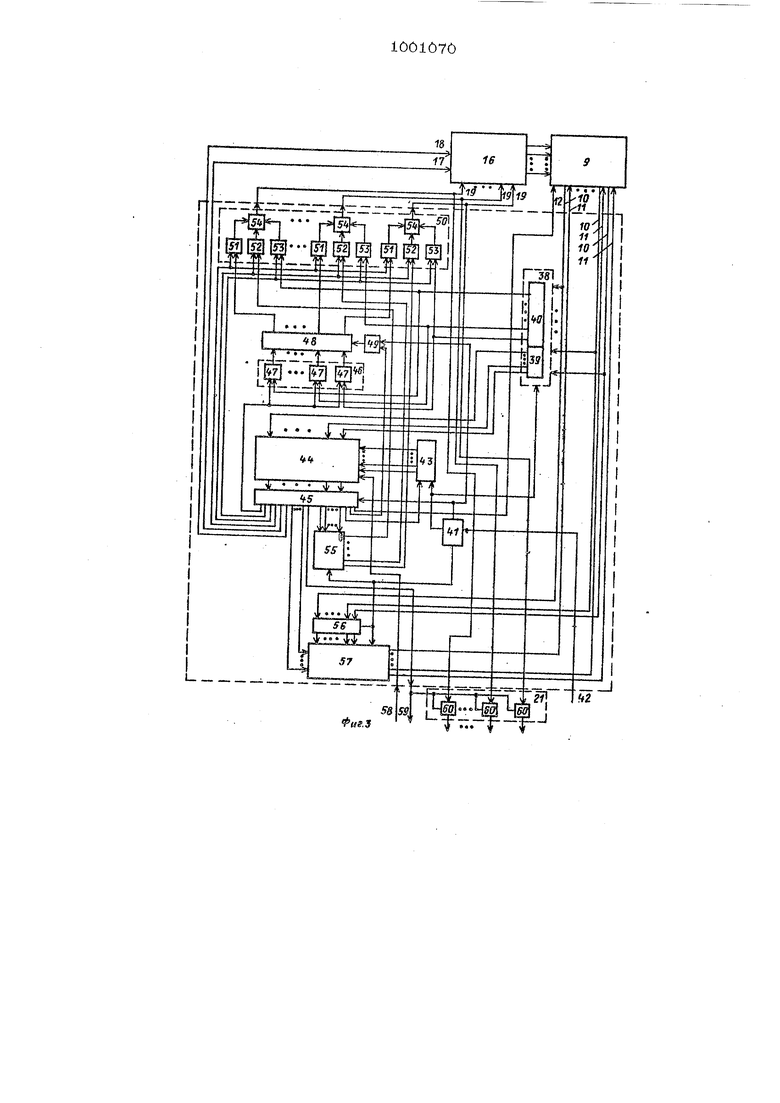

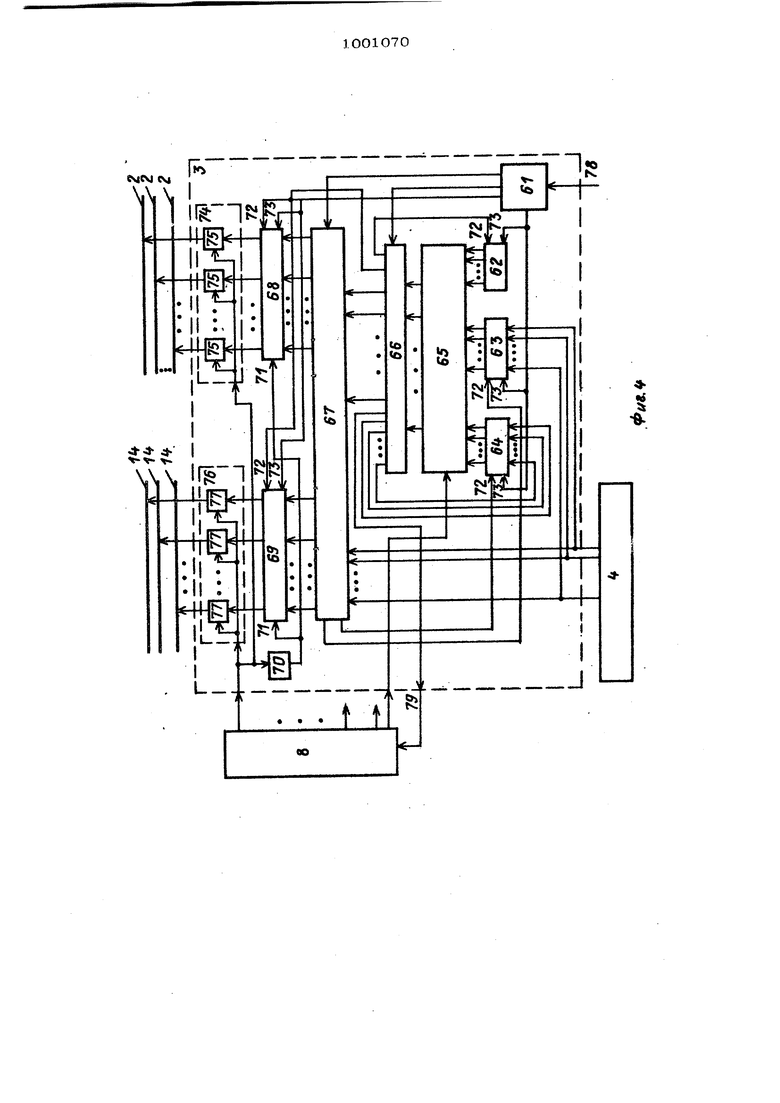

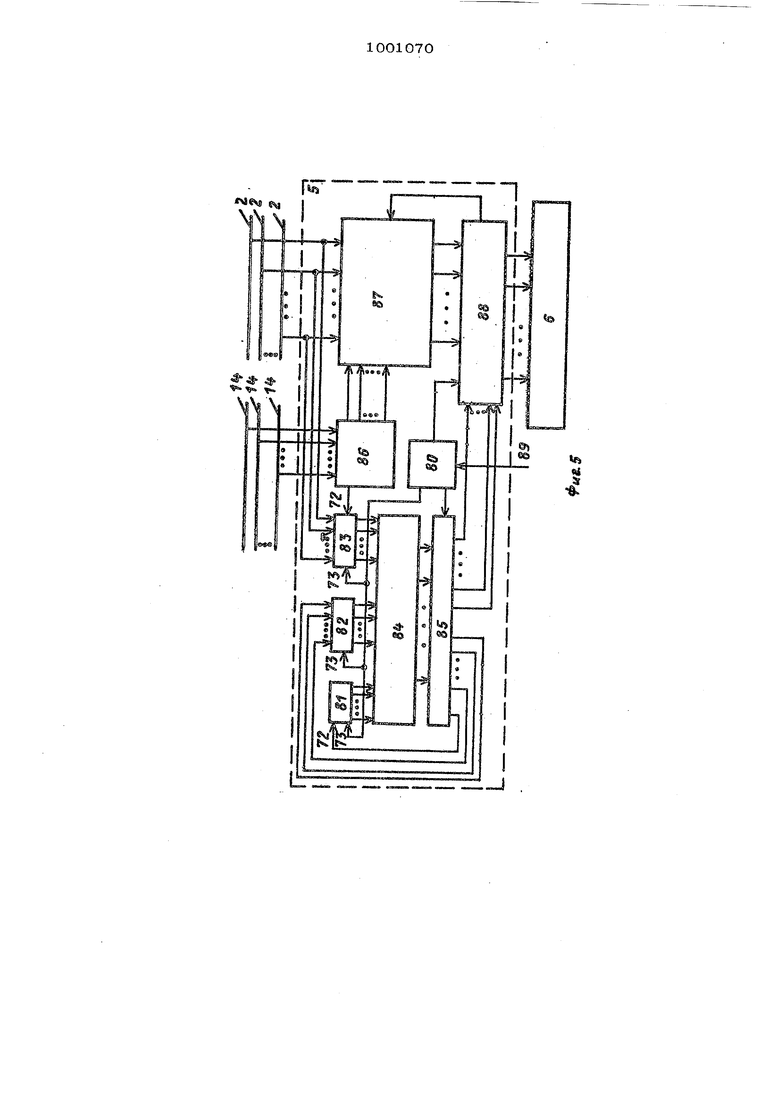

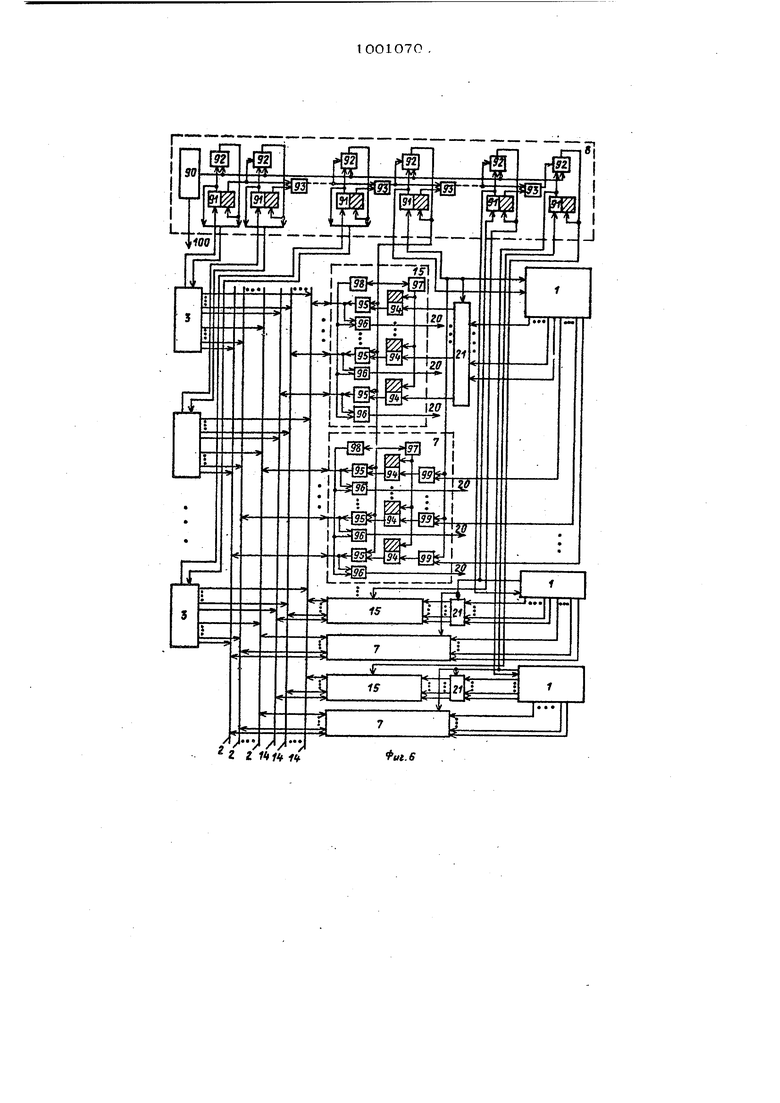

рядными шинами считывания и вторыми адресными шинами соответствующих местных блоков памяти Sj . Недостатки этой системы состоят в низкой пропускной способности, больших затратах оборудова1шя и сложности системы. Цель изобретения - повышение пропусшюй способности и упрощение системы, Поставленная цель достигается тем, что в систему, содержашую группу про цессоров ввода данных, группу процессо ров вывода данных, блок приоритета и группу блоков сопряжения, каждый из которых включает блок пере1слючения данных и блок памяти данных, причем вход каждого процессора ввода данных группы соединен с соответствующим информационным входом системы, а вход -выход с соответствующим входом-выходом блока приоритета, выход каждого процессора вывода данных груп пы подключен к соответствующему информационному выходу системы, первый вход через магистральную шину данных к первым выходам процессоров ввода данных, в каждом блоке сопряжения группы управляющий вход, информационный выход и первый информационный вход блока памяти данных являются соответствуюшими входами и выходом для подключения информационных процессоров, второй информационный вход блока памяти данных соединен с выходо блока переключения данных, вход-выход и управляющий вход которого подключен соответственно через магистральную шк ну данных к выходам процессоров ввода данных и входам процессоров вывода данных к к соответствующему выходу блока приоритета, в каждый блок сопря- же1шя группы введены блок переключени ассоциативных признаков блок памяти ассотсиативных признаков и коммутатор, тричем в каждом блоке сопряжения упра гтяюишй вход записи и первый вход опро эа блока памяти ассоциативных признаков соед инены соответственно с управляющим входом записи признаков и с входом ассоциативных признаков системы для подключения информационного процессора и информационным входом коммутатора, управляющий вход которог подключен к дополнительному управляоо щему входу системы для подключения информацио1шого процессора, а выход коммутатора - к информационному вход блока переключе1шя ассоциативных njDHs наков, управляющий вход и выход - соответственно с управляюЕЩМ входом блока пёреключеьшя данных и вторым входом опроса блока памяти ассоциативных признаков того же блока сопряжения группы, выходы процессоров ввода данных и вхо- . ды процессоров вывода данных соедин9 ны через магистральную шину ассоциативных признаков с входами-выходами блбков переключения ассоциативных признаков. На фиг. 1 представлена структурная схема системы на фиг. 2 - функциональные схемы блока памяти ассоциативных признаков и блока памяти данных; на фиг. 3 - блок-схема информационного процессора; на фиг. 4 и 5 - блок-схемы процессоров ввода и вывода данных; на фиг. 6 - функциональные схемы блока приоритета, блоков пере1шючения данных и ассоциативных признаков; на ;фиг. 7 - функциональная схема блока управления выводом данных. Система содержит (фиг. 1) информагшонные процессоры 1, магистральные шины 2 данных, процессоры 3 ввода данных, периферийные устройства источники данных 4, процессоры 5 вывода данных, периферийные устройства - потребители данных 6, бло1Ш 7 переключения данных, блок 8 приоритета, блоки 9 памяти данных, разрядные шины 10 считывания данных, первые разрядные шины 11 записи данных, шины 12 управления записью данных, вторые разрядные щины 13 записи данных, магистральные шины 14 ассоциативных при&наков, блоки 15 переключения ассоциативных признаков, блоки 16 памяти ассоциативных признаков, первые шины 17 управлешГя записью признаков, вто- . рые шины 18 управления записью признаков, первые шины 19 опроса, вторые разрядные шины 20 опроса и коммутаторы .21. Каждый блок 9 памяти данных соде1 жит (фиг. 2) ячейки 22 памяти для хранения данных, элементы памяти 23 ячеек 22, элементы И 24 связи с разрядными шинами 1О, элементы И 25 связи с разрядными шинами 11 и элементы И 26 связи с разрядными шинами 13. Каждый блок 16 памяти ассоциаивных признаков (фиг. 2) содержит ячейки 27 памяти для хранения ассоциаивных признаков, элементы памяти 28 чеек 27, первые индикаторы 29 совпадения, вторые индикаторы 30 совпадения, лементы И 31 связи с первыми разрвдными шинами 19 опроса, первую группу элементов И 32, вторую группу элементов И 33, третью группу элементов И 34, триггеры 35, четвертую группу элементов И 36 и пятую группу элемен- тов И 37. Информационный процессор 1 содержит (фиг. 3) регистр 38 команд, состоя щий из регистра 39 кода операции и регистра 40 признака опроса, генератор 41 синхронизирующих импульсов, вход 42 фазирования генератора синхро1низирующих импульсов от аапающего генератора синхронизирующих импульсов системы, счетчик 43 тактов, микропрограммную память 44, регистр 45 микро команд, коммутатор 46, состоящий из элементов И 47, счетчик 48 команд, элемент И 49, коммутатор 50, состоящий из элементов И 51 - 53 и элементов ИЛИ 54, блок 55 постоянной памяти, регистр 56 числа, арифметико-логическое устройство 57, вход 58 передачи сигнала требования с блока 8 и дополнительный управляющий .выход 59 инфор- мационного процессора. Каждая очередная команда программы, выполняемой информационным процессором, считывается из блока 9 в регистр 38. Одна часть командного слова является кодом выпопняемой процессором операции, а другая часть - признаком опроса, по которому в зависимости от кода операции производится или считывание данных из памяти, или запись данных в память, ияи при переходе на другую ветку программы считывание соответствующей этой ветке программы команды. Счетчик 48 команд обеспечивает ход выполнения программы. Счетчик 43 производит постоянный счет импульсов, поступающих с выхода генератора 41. По окончании каждой операции (по сигналу с выхода регистра 45) счетчик 43 обнуляется. По коду операции и номеру такта операции из микропрограммной памяти 44 в регистр 45 считывается I соответствующая микрокоманда, по которой в арифметико-логическом устройстве 57 выполняются соответствующие микрооперации. С помощью определенных микрокоманд из блока 55 обеспечиваетс передача ассоциативных признаков в блок 16. Коммутатор 21 (фиг. 3) состоит из элементов И 60. На фиг. 4 представлена функциональная схема процессора 3 ввода данных и показаны связи его с магистральными щинами 2 и 14 и с периферийными устройствами - источниками данных 4 и блоком 8. Процессор 3 ввода данных содержит генератор 61 синхронизирующих импульсов, счетчик 62 тактов, рен. гистр 63 приема входных сигналов, р&гистр 64 текущего адреса, микропрограммную память 65, регистр 66 микрокоманд, арифметико-логическое устройство 67, регистр 68 данныт регистр 69 ассоциативных признаков, элемент 70 задержки, вход 71 обнуления регистра 69, управляющий вход 72 регистра 69 (или счетчика тактов), синхронизирующий вход 73 регистра 69 (или счетчика тактов), коммутатор 74, элементы И 75, коммутатор 76, элементы И 77, вход 78 фазирования генератора 61 синхроимпульсов и управляющий выход 79. В каждом такте работы процессора 3 по синхроимпульсу с генератора 61 в регистр 63 записывается определен- ный код входных сигналов. По этому коду, по номеру такта, сформированному на выходе счетчика тактов, и по значению текущего адреса в регистре 64 из микропрограммной памяти 65 в регистр 66 считывается микрокоман/ ное слово, определенные разряды которого передаются обратно в регистр.текущего адреса. Определенная последовательность считываемых микрокомандных слов (микропрограмма) обеспечивает обработку входных сигналов в арифметико-логическом устройстве 67 и передачу данных и сопровождающих их ассоциативных признаков в регистры 68 и 69. По приходу с блока 8 сигнала подключения данного процессора к магистрали очередное слово данных и сопровождающий его ассоциативный признак передаются с помощью коммутаторов 74 к 76 в магистраль (шины 2 и 14). Далее сигнал подключения процессора к магистрали, пройдя через элемент 7О задержки, обнуляет регистры 68 .и 69. Очередное требование на передачу данных через магистраль формируется в процессоре 3 на управляющем выходе 79. Процессор 5 вывода данных содержит (фиг. 5) гецератор 8О синхроимпульсов, счетчик 81 тактов, регистр 82 текущего адреса, регистр 83 приема управляющего слова, микропрограммную память 84, регистр 85 микрокоманд, дешифратор 86, накопитель 87 оперативной ин- формации, блок 88 управлен 1я выводом данных и вход 89 фазирования генерато- .ра 80 синхроимпульсов. Организация выполнения микропрограммы в процессоре 5 обеспечивается таким же образом, как и в процессоре 3 ввода данных, С помощьюдешифратора 86 управляющие слова записываются в регистр 83, а собственно данные - в накопитель 87.. В дальнейшем с помощью блока 88 данные в определенной последовательности по врем и определенными частями передаются на вход периферийного устройства - потребителя данных 6. Блок 8 приоритета (фиг. 6) содержит задающий генератор 90 синхронизирующи испульсов систем и .аъЛ регистр г каждый разряд которого, кроме первого и последнего, содержит триггер 91, первый элемент И 92 и второй элемент И 93 (в первом и последнем разрядах устройства второй элемент И 93 отсутс вует). Блоки 7 переключения данных и 15 переключения ассоциативных признаков содержат регистр, состоящий из триггеров 94, магистральные передающие ключевые элементы 95 и 96, элемент задержки 97 и элемент НЕ 98. В блоках 7 в состав регистра входят также элементы И 99. Выход 1ОО задающего генератора 9О синхронизирующих импульсов соединен с входами 42,78 и 89 соответствующих процессов,при этом с помощью сигналов фазирования, передаваемых на эти входы, обеспечивается синхроннал работа (работа на частоте задающего генератора 9О) всех процессоров системы. После передачи через магистраль очередного слова данных и ег6 ассоциативного признака в блоке 8 сбрасывается триггер, соответствующий тому процессору, который выдал это слово на магистраль. Получив сигна о нулевом значении триггера, процессор переходит в режим готовности выдачи на магистраль следующего слова дан-ных, и процессор передачи данных через магистраль вновь повторяется. ВЛок 88 управления выводом данных процессора 5 содержит (фиг. 7) элемен ты И 101, элементы ИЛИ 102, буфер:ные элементы 103 согласования, дещиф ратор 1О4, приемный регистр 105, соо тоящий из триггеров 106. Накопитель 87 оперативной информации содержит (фиг. 7) элементы 107 памяти и элементы И 108 и 109. В ходе работы блока 88 считанные из . ячеек накопителя 87 на приемный регис 105 слова передаются отдельными час тями с определенным интервалом време.ии между этими частями на вход пери- ферийного устройства-потребителя 6 данных, например устройства вывода на перфоленту с числом дорожек, равным числу разрядов передаваемых на это устройство блоком 88 кодов. Система работает следующим образом. В исходном состоянии все ячейки 27 блоков 16 находятся в обнуленном состоянии. Перед началом работы системы каждый из информационных процессоров 1 производит запись нужных наборов признаков в ячейки своего блока 16. Эти наборы признаков с выходом ассоциативных признаков процессора поступают на разрядные щины 19, а управляющие сигналы процессора поступают на щины 17 и 18 управления записью признаков. Указанные наборы признаков после записи их в ячейки блока 16 становятся указателями местоположения (адресами) ячеек блока 9 при их выборке. При формировании на выходах процессора 1 соответствующего набора признаков этот набор сравнивается со всеми записанными в ячейки блока 16 наборами признаков. По совпадению с одним из этих наборов признаков па соответствующем управляющем выходе этого блока формируется управляющий сигнал, по которому в одноименном блоке 9 производится выборка соответствующей ячейки. При этом -по сигналу разрешения записи данных, поступающему на щину 12 блока 9 памяти данных, данные с выхода процессора 1, поступившие па разрядные шины 11, записываются в выбранную ячейку блока 9. После записи в блоки 9 и 16 необходимых для работы системы наборов признаков и исходных данных, в том числе и команд выполняемых программ, информахшонпые процессоры переходят к решению возложенных на них задач. При этом процессоры 3 ввода данных принимают поступающую в них с периферийных устройств-источников данных информацию, производят предварительную ее обработку, например сортировку и накопление, и формируют на своих выходах по сигналам с блока 8, разрешающего доступ данного процессора к магистрали, входные слова данных, одна часть которых выступает в качестве признака даппых, а другая часть - в виде собственно данных. Признаки данных поступают па магистральные шины 14 ассоциатив- ных признаков, а собственно данные - на магистральные щины 2. С магистраль- ных шин входные слова данных, пройдя через блоки 7 и 15, находящиеся в от рытом по отношению к сигналам с маги стральных шин состоянии (единичные значения на их управляющие входы с блока 8 в этот момент не. подаются), поступают на разрядные шины 13 и 20 каждого из блоков 9 и 16. Все блоки 16 производят сравнение записанных в них признаков с признаками передава мых с процессора 3 данных и по совпадению формируют на своих выходах управляющие сигналы, по которым в соответствующие ячейки связанных с этими блоками блоков 9 производится запись поступивших на их входы кодов. В блоках 16, связанных с теми проце- ссорами, в функцию которых обработка данных, передаваемых процессорами вв да данных, не входит, совпадение поступившего из магистрали признака ни с одним из записанных в них признаков не происходит, вследствие чего информация в одноименных блоках 9 не изме- няется Промежуточные результаты задач, решаемых информационными процессорами, передаются ими друг другу аналогичным образом. При этом те из них которые после их получения нужны данному процессору в дальнейшем, передаю ся им как в собственный блок 9, так и через магистральные шины 2 в блок памяти данных других процессоров. Для этого информационный процессор формирует на своих шинах 19 код признака отправляемого в память результата. Пр чем запись результата в собственный блок 9 осуществляется по сигналу упра ления записью данных, поступающему с процессора по шине 12., а запись результата в блоки 9 других процессоров по сигналу разрешения записи данных через магистраль, поступающему на управляющий вход связанного с данным процессором коммутатора 21, на вход блока 7 и на вход блока 8. По этому сигналу код признака и код результата записываются в регистры соответствующих блоков 15 и. 7 и хранится в них до тех пор, пока с выхода блока в не поступит сигнал подключения данного процессора к магистрали. Этот сигнал формируется на выходе блока 8 сразу в том случае, когда на его вход в оч&редный момент времени сигнал разр&шения записи данных через магистраль поступает только от одного из процеосоров. Есяи указанные сигналы поступа на его вход от нескольких процессоров одновременно, то в соответствии с заданным приоритетом блок 8 производит поочередное подключение указанных процессоров к магистрали. В процессе поочередного подключения информационных процессоров к магистрали каждый из них в определенные моменты времени обращается в блок 9, записывая или считывая соответствующую информацию, а после подключения указанного процессора к магистрали на соответствующем выходе блока 8 формируется сигнал, по которому этот процессор 1 при подготовке им очередного результата, необходимого другим процессорам, отправляет его через магистраль в их памяти аналогичным описанному выше способом. При этом по сигналу подключения процессора к магистрали, поступающему на управляюдие входы соответствующих блоков 7 и 15, инсЬормация, записанная в регистры . этих блоков, вьщается в магистраль, а все остальные процессоры принимают поступающую с магистрали информацию и передают ее на выходы своих штоков 7 и 15. Так как блоки 9 каждого из процессоров 1 имеют два тракта записи информации, а блоки 16 памяти ассоциативных признаков имеют две группы шин опроса 19 и 20 то каждый из информационных процессоров 1 в гот момент, когда в его блок 9 записывает свой очередной результат какой- ибо другой процессор 1, может одновременно записать в этот блок в соответствуюпяую ячейку свой промежуточный результат или списать из нужной ячейки требуемую для его вычислений информацию. При этом все записываемые в блоки 9 системы данные сопровождаются при их записи такими кодами признаков, которые соответствуют функциональной роли этих данных в алгоритме решаемых системой задач, а именно тем участкам программы и, соответственно процессорам 1, находящимся на этих участках, на которых эти данные отправляются в блок 9 на хранение. Окончательные результаты решаемых системой задач передаются соответствуюш 1ми информационными процессорами 1 в процеосоры 5 вывода данных. Передача этих данных осуществляется аналогично п&редаче данных между информационными процессорами1. Процессоры 5 вывода данных реагируют на поступление соот ветствующих им кодов признаков данных и направляют эти данные на периферийные устройства-потребители 6. цанньтк. Запись в из блоков 16 в ходе работы системы производится 5саждым из информапионных процессоров 1 еле дуюихим образом. В тот момент, когда процессор 1 производит считывашю из соответствую щей ячейки по коду признака ее опроса той информации, которая ему бояъше не нужна в последующих вычислениях, он формирует на шине 17 блока единичное значение сигнала. По этому сигналу срабатывает тот элемент И 34, на другой вход которого подается сигнал с выхода элемента И 32, срабатывающего по совпадению значения на выходе всех элементов 28 памяти соответствующей, ячейки 27 со значе шями, поступивщими на разрядные ишны 19. Сигнал с выхода элемента И 34 сбрасывает соответст вующий выбранной ячейке триггер , 35, установленный ранее при записи информ ции в эту ячейку в единичное состояние переводя его в нулевое состояние. В дальнейшем при выполнешш аналогичного считывания из других ячеек.27, расположенных в блоке 16 в произвольном месте, тр.иггеры 35 этих ячеек та же переводятся в нулевое состояние. При записи в блок 16 новых наборов признаков камодый из них при появлегош ед11;ничного сигнала на шине 18 запи- сьшается в ту ячейку блока .16, триггер 35 которой находится в нулевом состоянии, а триггеры 35 всех преды™ душих ячеек - в единичном состоянии. При этом по единичному значению этих триггеорв и по едишганому сигналу на шине 18 срабатывают все элементы И 36, связанные с данны ди триггерами, В результате срабатывает элемент И 37,, относящийся к ячейке, в которую производится запись очередного набора поступающ1-1х по 1Ш-1нам 19. По сигналу с выгода элемента И 37 эти признаки через элементы И 31 связи с разрядными ij, спроса записываются в эле- менть 28 памяти соответствующей ячей ки 27о Выборка соответствующей ячейга блока 16 при обращении к нему со сто-. роны магистрал.и, т.е, со стороны чужо го процессора, производится по совпадегию значе)шй на выходе всех элементов памяти 28 этой ячейки 27 со значениями, поступившими на разрядные шины 2 При. этом срабатывают индикаторы 30, стояите на выходе элементов 28 памят данной яче11Ш1 27 и соответствующий лемент И 33, формирующий на управляющем выходе блока 16 сигнал разрешения выборки соответствующей ячейки блока 9 памяти данных. Таким образом, в предлагаемой системе обмен информацией между информационными процессорами осуществляется без непосредственного участия в самом сеансе связи процессоров-приемников, что и обеспечивает повыщецие производительности системы. Формула изобретения Система для обмена данными между информационными процессорами, содержащая группу процессоров ввода данных, группу процессоров вывода данных, блок приоритета и группу блоков сопряжения, каждый из которых включает блок переключения данных, и блок памяти данных, причем вход камодого процессора ввода данных группы соединен с соответствующим информационным входом системы, а вход-выход - с соответствующим входом-выходом блока приоритета, выход каждого процессора вывода данных группы подключен к соответствующему информационному выходу системы, первый вход через магистральную шину данных - к первым выходампроцессоров ввода данных, в каждом блоке сопряжения группы управляющий вход, информационный выход и первый информационный вход блока памяти данных являются соответствующими входами и выходом для подключения информационных процессоров, второй информационный вход блока памяти данных соединен с выходом блока переключения данных, вход-выход и управляющий вход которого подключены соответственно через магист ральную щину данных к выходам процессоров ввода данных и входам процессоров вывода данных и к соответствующему выходу блока приоритета, отличающаяся тем, что, с целью повыщения пропус1сной способности системы, в калодый блок сопряжения группы введены блок переключения ассоциативных признаков, блок памяти ассоциативных признаков и коммутатор, причем в каждом блоке сопряжения управляющий вход записи и первый вход опроса блока памяти ассош1ативных признаков соединены соответственно с управляющим входом записи признаков и с входом ассоциативных признаков системы для

подтслючения информационного процессора и информационным входом коммутатора, управляющий вход которого подключен к дополнительному входу систе мы для подключения информационного

процессора , а выход коммутатора - к информационному входу блока переключения ассоциативных признаков, управляющий вход и выход соединены соответс вено с управляющим входом блока переключения данных и вторым входом опроса блока памяти ассоциативных признаков

того же блока сопряжения группы, выходы процессоров ввода данных и входы процессоров вывода данных соединены через магистральную шину ассоциативных признаков с:Эходами- выходами оков переключения ассоциативных признаков.

Источники информашш, принятые во внимание при экспертизе

1.Патент США № 4065809, кл. 364-2ОО опублик. 1977.

2.Патент США № 4172283,

кл. 364-;2бб, опублик. 1979 (прототип).

Г

еч|

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для сопряжения цвм с каналами передачи данных | 1978 |

|

SU744541A1 |

| Ассоциативное запоминающее устройство | 1976 |

|

SU651416A1 |

| Ассоциативное запоминающее устройство | 1978 |

|

SU771719A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2037215C1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

4-4 44

ft.

tf)

.«

Авторы

Даты

1983-02-28—Публикация

1980-12-25—Подача