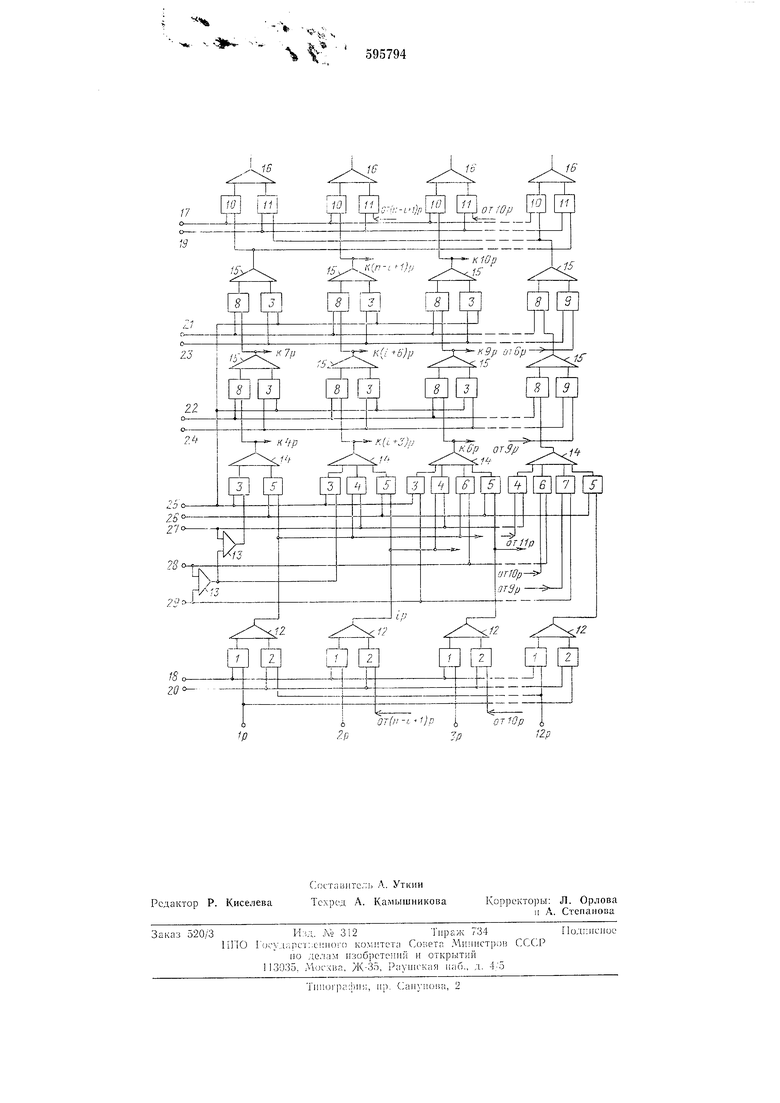

элемента ИЛИ, первые входы кроме того, элементов И в К етарших коммутаторов каждого /-ГО яруса соединены первым входолг с шиной знака числа, а вторым входом элементов И всех ярусов соединен, с COOTISCTCTByioHicft Ш1Н10Й сдБнга. Сущность предлагаемого нзобретсння ноясняется чертежом, где представлена схема 12-разрядного реверсивного параллельного регистра сдвига, содержагцая блок спмметрпчного перекрестного прнема кода, собранного на элементах 1, 2, 12; многостуненчатый блок сдвнга внраво положительных н отрнцательных чисел, состоящпй из первой переменной ступени сдвнга на О, 1, 2, 3 разряда, собранной на элементах 3-9, 13, 14; второй н третьей ностоянных ступеней сдвнга на 3 и 6 разрядов, собранных на элементах 3, 8, 9, 15, в которые входнт блок формирования обратного кода числа, собранного на элементах 3, 13- 15; блок перекрестной выдачи кода, собранного на элементах 10, 11, 16, шины сдвигов кода внраво 17, 18, шнны сдвпга кода влево 19, 20, шнны разрешения сдвнга кода соответственно третьей и второй стуненей 21, 22, шппы нередачп кода без сдвига, соответствепно через третью п вторую ступепь регнстра сдвига 23, 24, Н1ина знака числа 25, шнны разрешения сдвнга на О, 1, 2, 3 разряда переменной стуненн регнстра -сдвига 26, 27, 28, 29; означают соответстБуюш,пй разряд I р, 2 р, ..., 12 р (i+k)p, (n-i+l)p. В каждом разряде однн вход элементов И- liE 1 н И-НЕ 2 блока симметричного нрнема кода подключен соответственно к шине сдвнга вправо 18 п к шнне сдвпга влево 20, а вторые входы этих элементов подключепы к кодовой шнне числа соответственно t-ro п (/;-1+1)-го разрядов. Выходы И-НЕ 1 н Н- НЕ 2 соедниеиы с входом элемента НЕ-ИЛИ 12. Выход элемента ИЛИ-НЕ 12 /-го разряда соединяется с одним входо.м элементов И-НЕ 5, 4, 6, 7 неремепной ступени регистра сдвига соответственно в i-oM, i+1, г + 2, i+3 разрядах. Вторые выходы этих элементов соединены соответственно с шннами сдвнга 26, 27, 28, 29 неременной ступени на О, 1, 2, 3 разряда. Выходы элементов И-НЕ 5, 4, 6, 7 соединены поразрядно с входами элемента ИЛИ-НЕ 14. Выход элемента ИЛИ-НЕ 14 t-ro разряда соединяется с входом элемента И-НЕ 8 н И-НЕ 7, второй днскретной ступенн регнстра сдвига соответственно в i-ом н t+3 разрядах. Вторые входы элементов И-НЕ 8 соединены с шнной передачи кода без сдвпга 22, а у элементов И-НЕ 9-с шиной разрешения сдвпга второй ступени 24. Выходы элементов И-НЕ 8 и И-НЕ 9 подключены к входам элемента ИЛИ-НЕ 13. Выход элемента ИЛИ-НЕ 15 1-го разряда второй ступени соединен с элементами И-НЕ 8, 9 третьей стуненн регистра сдвнга соответственно в I-M н f-|-6 разрядах. Вторые входы элементов И-НЕ 8 н 9 аналогнчно второй ступепн соеднпены соответственно с Н1ННОЙ нередачп кода без сдвнга через ступень 21 н с ппной разрешения третьей ступени 23. Выход элемента НЕ 15 третый (последней) CTVHCHH ресдинга соединяется с входом элсмен1Е И (П-Tiioii вьдаВторыеИ -НЕ И) еоединеиы с шшюи сдвн1-а вн;1аво I Л а элемента И---НЕ 11 --с Н1ИНОЙ сдвига 19. Выходы элементов И - НЕ 0 н И --НГг 11 подключены к входу элементг. ИЛИ --I-1E К;. Однн вход элемента И-НЕ 3 блока формнровання обратного кода подключен к шнне знака числа 25. Второй вход И-НЕ 3 у элементов днскретных ступеней блока сдвнга соед :нен с соотвстстзуюн1ей раз;) едв1н-а 23 н 2-1, а у элементов неремсн о:-: ступенн - с выходом cooTp cTCTByiOiHeio элсМ, ИЛИ -НЕ 13, на входы которых нодключешд шнны сдвнга неременной етуненн. Выходы элемента И-НЕ 3 в дискретных ступенях подключены ко входам элементов ИЛИ-НЕ 15, а в переменной етупепп-к входам элеMeiiTOB ИЛИ 14. Рассмотрнм работу нредлагаемого устройства на конкретных нрнмерах. Нрнмер 1. От нцатсльное число 1, 011 0011 11001, записанное в обратном коле, единнем внра;50 на 8 разрядов. Ирн тако.м уеловнп разреп1аюн1не нотендналы будут нметь нлнны сдвнга вправо 17 п )8, П1нна знака чнсла Io, шнна сдврна на два разряда неременной етуненн 28, шнна нерсдачн кода без сдвн1-а через вторую стунень 22 г ншна разрен ення сдвига третьей стунс-ни 23. Суммарный сдвиг на 8 разрядов набирается из сдвнга на G третьей стуненн н сдв;н-а на 2 переменной ступенн. В -соответствии с этнм сигналы кода проходят по следуюн,11м 1г;н1ям. В блоке снм.метрнчного нрнема код нроходнт через Н---НЕ 1, ИЛИ-НЕ 12 без нзменення. В неременной ступен блока сдвнга код нройд п через И - НЕ 6, начнная с третьего разряда, а is нерзых двух етарш1 х разрядах будут сформнрованы снгналы еднннп элементами ИЛИ--НЕ 3 н И-НЕ 13, к результате чего -на выходе первой ступени будет код 1,110 11 00 11110. Этот код нередается без нзменення через э.чемснт И-НЕ 8, ИЛ PI 15 второй стуленн на вход третьей стуненн, которая осунтествнт модифннированный сдвиг на 6 разрядов, т. е. в 6 старшнх разряах будут сформнрованы снгналы едпннн, а ноступнвшнй код со сдвигом на 6 разрядов нройдет через элемент И-НЕ 9 остальных естн разрядов. На выходе третьей етупенн будет код 1,111 1111 10110, который без г-змеения нройдет через элементы И-НЕ 10 н ИЛИ-НЕ 16 на выход блока нерекрестной выдачн. Н р н мер 2. Отрнцательное число 1,0110011 11001, заннсанное в обратном коде, двннем влево па 5 разрядов. Нрп таком услонн разренгаюшне лотенпналы будут нметь едвнга влево 19 н 20, ниша знака чнсла 25, нчша едвнга па 2 )азряда 28, нгнна разрешсния сдвига второй ступени 24 и mHiia передачи кода без сдвига через третью ступень 21. В блоке симметричного приема кода код пройдет через элемент И-НЕ 2 и на выходе будет нметь вид 1,100111100110, далее как и в первом примере, пройдет по тем же цепям переменной ступепи блока сдвига и на выходе ее будет код 1,1110011 11001. Во второй стуненн блока сдвига осуществится модифнцированный едвнг «а 3 разряда, т. е. в трех старших разрядах через элемент И-ME 3 сформируются сигналы единиц, а в остальных разрядах код пройдет через элемент И-НЕ 9 и будет иметь вид 1,111 111001111. Через третью ступень код передается без изменения. В блоке перекрестной выдачи код пройдет через элемепты И-НЕ II, ИЛИ-НЕ 16 и на выходе ее будет представлятьискомый результат 1,111 1001 11111, т. е. мы осуществим сдвиг влево отрицательного числа на 5 разрядов. При сдвиге положительных чисел шипа зпака числа ис имеет разрешающего потенциала, поэтому в освобождаемые разряды при сдвиге будет записываться код нуля. Разработанный регистр сдвига позволяет осуществлять симметрпчную перекрестную выдачу числа при различных сдвигах. Для выявлепия преимуществ предлагаемого реверсивного параллельного регнстра сдвига проведем сравнительную оценку по объему оборудовайпя с региетром сдвпга, имеющп:, отдельные цени для сдвига влево и внраво. Предлагаемую структуру многоступенчатого регистра сдвига следует применять с учетом количества разрядов. В частностн, для 8 и 12 целесообразно строить двухстуиенчатый, для 12 и 32 - трехступенчатый, для 32 - четырехступепчатый. Например, для трехступенчатого регистра сдвига из чертежа наглядно видно, что экоиомия оборудования определяется переменной ступенью сдвига н в пересчете па двухвходовые элементы Н-НЕ для /г 16опа равна 114 элементам; она равна 234 элементам; « 32 она равиа 397 элементам. Эти сдвигатели имеют соответственно следующие стуиепи сдвига: 4- -4-1-8; 6-1-6+12; 8+8+16. Для четырехетупенчатого сдвигателя экономия оборудования увеличится на Зп элементов, необходимых для одной дискретной ступени. 6 Формула изобретения Реверсивный параллельный регистр сдвига, содержащий блок еимметричного приема кода, еоетоящий из п коммутаторов, управляюии1е входы которых соединены с шииами раз кмпе:п я сдвига кода, причем входная шипа (-го коммутатора ( еоедииепа со входом г-го и (и-г+1)-го разряда сдвигаемого кода, блок перекрестной выдачн кода, состояluini из п коммутаторов, блок сдвнга, состоящий нз несколькг1х ярусов коммутаторов, по /г коммутаторов в каждом яр}ее, причем входы всех коммутаторов соединены с соответствуюпи ми шинамн разрен1е 1пя сдвига ола от О до /2 разрядов, а выход г-го коммутатора /-го яруса соединен со входами /-го и (i + + )-ro коммутаторов (/+)-го яруса блока сдвига, о т л и ч а ю щ с я тем, что, е целью обеспечения сдзша чисел любого знака в обоих направлениях и упрощеппя устройства, в регистре выход г-го разряда г-го коммутатора блока симметричного приема кода соединен с входамп /-го коммутатора г-го разряда и с входами К коммутаторов К младших разрядов первого блока сдвига, выхо;; А; ЖДОГО /-го коммутатора пос.чедпего яруса блока сдвига соединеп е входами /-ГО и (л-/+1)-го коммутаторов блока перекрестной выдачи кода, другие входы которых соедпнеиы с шинами разрешения кода п иппюй знака числа. 2. Регистр по п. 1, о т л и ч а ю пд и и с я тем. что каждый коммутатор выполнен на логических элементах И-НЕ, НЛН-НЕ, причем / входов элемента НЛН соедпнспы с выходами / элементов Н-НЕ, входы которых являются входами коммутатора, а его выхолом - выход элемента НЛН, первые входы элементов М в К старших коммутаторов каждого /-ГО ярхса блока едвнга соединены с шиHOi зпака числа, вторые входы элементов Н всех ярусов - с соответств юще1 И1ино 1 сдвпИсточннкп информации, принятые во внимание нрн экснсртнзе 1. Патент Японни До 48-23868, кл. 97 (7) Е42. 1974. 2. Авторекое свидетельство СССР ,9 439017, кл. G ПС 19/00, 1974 (прототпп).

- it s

. & . i

%595794

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравлений | 1974 |

|

SU526905A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1973 |

|

SU430369A1 |

| Формирователь сигналов кода морзе | 1975 |

|

SU574862A1 |

| Устройство для извлечения квадратного корня | 1973 |

|

SU544960A1 |

| Устройство для учета цемента | 1978 |

|

SU737390A1 |

| УСТРОЙСТВО для УСКОРЕННОГО УМНОЖЕНИЯ ЧИСЕЛ | 1970 |

|

SU269607A1 |

| УСТРОЙСТВО для СЖАТИЯ СООБЩЕНИЙ | 1973 |

|

SU365847A1 |

| Устройство для сдвига информации | 1983 |

|

SU1109807A1 |

| Устройство для сдвига информации | 1975 |

|

SU643864A1 |

| Устройство для перемножения многочленов | 1973 |

|

SU495663A1 |

Р

Ъ

Авторы

Даты

1978-02-28—Публикация

1975-03-03—Подача