ИзобрСТСППО относится к области Б 1Ч СЛИтельной TexiiiiKU и может быть использовано нри nocTpocHHi цифровых вычислительных машин на основе больших интегральных схем. Известны устройства для перемножения многочленов, равных произведению многоi

i X на

мноточлен

лева Го

где Ai 1 и Lij 1, содержаш,ие регистрь

IB; блсКИ су мирования и блок правленля.

Однако известные устройства имеют иебольшую скорост) вы-лкления, так ка;к время, необходимое д.ля формирования коэффициентов указанн;;го многочлена с помощью таких устройств, состав./лет ;г-. -.- («--Hi) (т-|-1) г-( МКС, где f V -- время сложения двух операндов, г - количество разрядов в регистрах оиераНдов.

С целью повьлнсния быстродействия, сокращения в,;емели, необходимого для формирования коэффициентов многочлена, равного

У /1г

многочлена

произве.дению

i о

многочлен V Bj Х , где и В:,

J--0

I Н))едлаг; емое устройство введены коммутатор, блок сдвига и блок анализа разрядов операндов, одна группа входов которого сос9

динсца с выходами регистров одного .многочлена, а выходы ---со входами регистров другого многочлена, выходы которых соединены с однимн входами блоков суммирования, их выходы соединены со входами блока сдвига, выходы которого соединены с одними входами регистров результата, выходы последних соединены со входами коммутатора, выходы которого соединены с другими входами блоков суммирования, причем вход коммутатора, блока сдвига и другие входы регистров резул1 тата соединены с соответствуюи,ими выходами блока управления.

Быстродействие иредлагаемого устройства

-1

r-f- МКС.

опреде;1яется выражением -

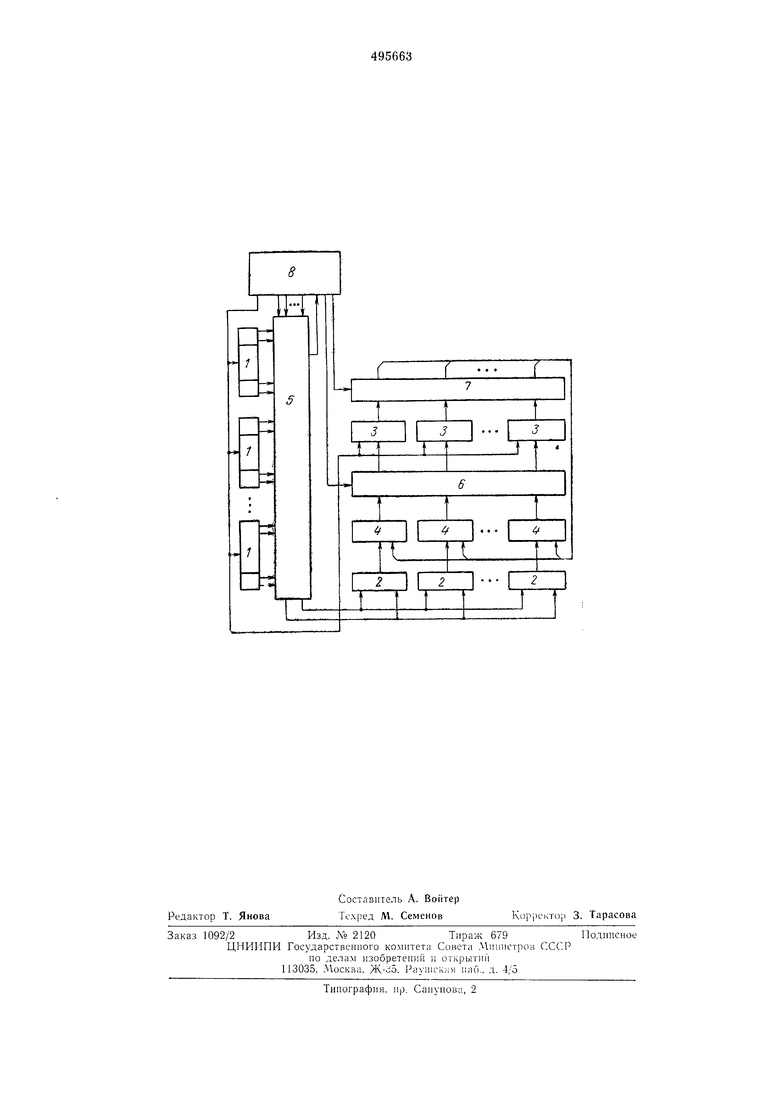

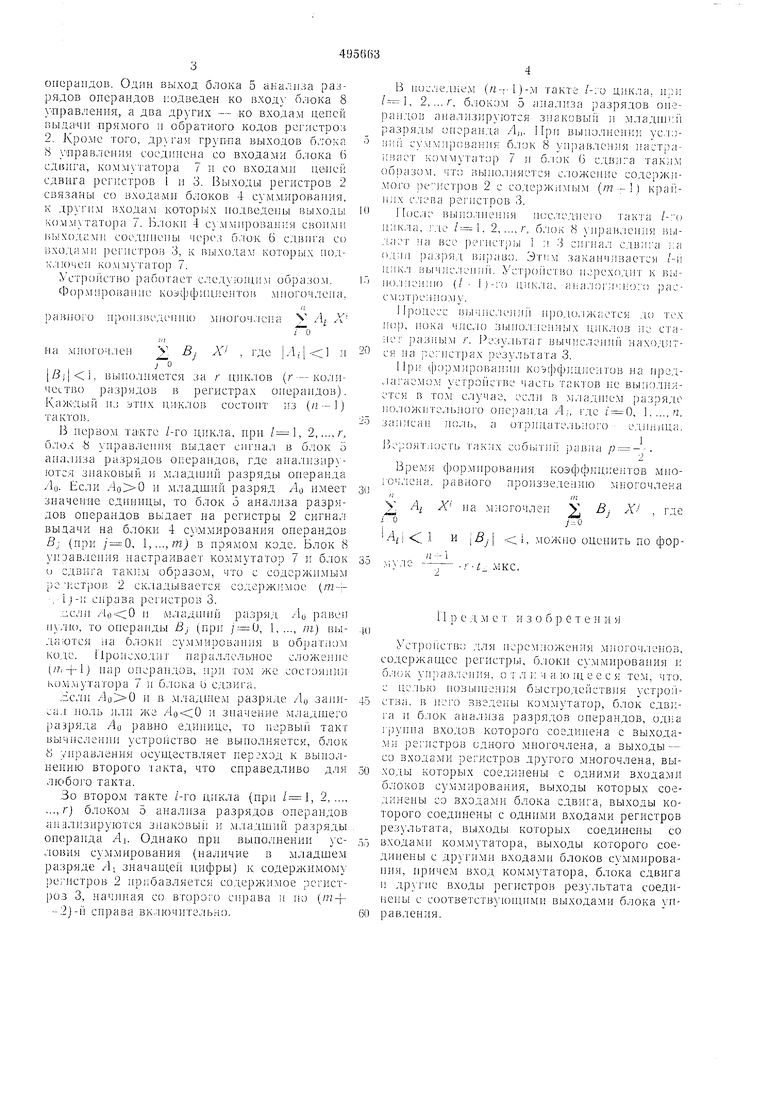

На чертеже изображена схема предлагаемого устройства для леремнол ения многочленов.

стройство состоит нз (/;--- ;-го регистров 1 коэффициентов Л,-, где г 0, ....,п, ()го регистров 2 коэ{)(.:111ииентов В;, где ,l,... ...,, (i-r-m-1)-го регистров 3 результата, (;н-1)-го блоков 4 суммирования, блока 5 анализа разрядов операндов, блока 6 сдвига, коммутатора 7 и блока 8 управления.

Прямые и инверсные выходы знаковых н м,1адших разрядов региетров 1, а также одна ;з выход1)в блока 8 управления иодключс.Ы ко входам блока 5 аналнза разрядов

0

3

операндов. Один выход блока 5 анализа разрядов операндов подведен ко вход} блока 8 т1|)авления, а два другнх - ко входам ценен выдаЧ прямого и обратного кодов регистроз 2. Кроме то.го, грунпа выходов блока 8 правлеиия еоедннена со входами блока (J сдвнга, коммхтатора 7 i со входами ueiHei; сдвнга регистров 1 и 3. Выходы регистров 2 связаны со входами б а о ко в 4- суммл-грования, к другим входам которых нодведеиы выходы коммутатора 7. Блоки 4 сулшировавия своими | ыходами соединены б.кж 6 сдвнга со 1 ход;мн регистров 3, к вв1ходам которых иодк;1К)чеи коммутато 7.

Устр{и 1с1ти) работает следуклцим образом. (орАгирог аиио коэффии.иентов миогочлсна.

( V /Ь Л

У

где Го

1/3;j i. ввгнолияетея за г Цик.тов

чеггво разрядов в регистрах онерандов).

Кал ДЬ1Й из этнх .тов состоит (;j -1)

TaicTOB.

13 нервом таа-:те 1-го цикла, нрн , 2,..., г, бло. 8 унравлеини выдает сигна.л в блок 5 анализа разрядов оиерандов, где ана;п1зируютс.я зиаковый и младишй разряды онеранда Ло. Если и младш.ий разряд Ло имеет значеиие едиинцы, то блок о анализа разрядов операндов выдает на регистры 2 сигнал выдачи на блоки 4 суммирования онерандов В; {нри , 1,...,п) в ирямом кодс. Блок 8 унэавления настраивает коммутатор 7 и блок о сдвига таким образом, что с содержимвш ре licTiJOB. 2 складывается , 1)-и ciipaBa регистров 3. .с.ели и млади1ин нулю, то онеранды Bj (нрн i--(i, 1, даются на блоки су.ммироваиия в ко.те. Происходит иараллельтюе ( нар оггсрандов, ирн гом же )M.iyTaTopa 7 и б.тока б сдвига.

dcjiu н в младшем разряде Лу заннсал иолв или же и значение младшего разряда Ло равно единице, то иервый такт вычислен)Н1 уетронетво не вынолняется, блок 8 унравлення осунхествляет иер.ход к вынолненню второго такта, что снраведдиво для любого такта.

Зо втором такте /-го цикла (при , 2,..., ...,rj блоком 5 анализа разрядов онерандов анализируются зиаковын и .м,тадш11Й разряды оиераида Ль Однако .при вынолненин сло1 ня сум.мирования (наличие в младшем разряде Ai значащей цифры) к содержимому ре;иетров 2 нрибавляется содержимое рсгистроз 3, нач) со второго сн)ава н но (m-f -2)-и сирава вклк)ч ггельно.

4

В последнем (н-г-1)-м такте /-го цикла, и;;; 1, 2, ...г, блоком 5 анализа })азрядов оиераидои аиализируются зиаковый и младнггГ разря.чы онгранда Л,,. При вынолиени) уе/юiiiiii суммирования 6;ioK 8 уирав;1емия iiacTjia1П ает к()ммутат;)р 7 и б.тэк 6 сдвига таким образом, что выио.лняется с:южсиис содержимого е:ч стров 2 с содержимым (m-l) Kpaiiиих слева регистров 3.

()слс .1иения И(}е,ле;1него такта /-го

и,икла, че / L 2г, 8 уи)зав;1еиия libiл, на все регистры 1 и 3 слв;|;-а :а о.чии раз|1яд 1 нраво. Этим закаич; ваетсм /-и

иолисник) (/ 1)-го цикла, а1|алог;1чи():-о расе 1;)тр;е;1И(..

Процесс вычисленн нродолжается .ю тех нор, нока число 31)1иоллеиных 11нкл()з ие етаНС рави1 м /. Результат вв1чиеленни находится на ileriieTpax результата 3.

При (рормироваиии коэффцщ еитов иа предлагаемом усгронстве часгв тактов не выиг)лняется в том ел уча г, если в млади ем разряде |и).1ожите;1ьиого оне)анда Л;, где (, ...., п. заи}(саи HO.;IIJ, а отрицательиого единица.

У Л; X иа многочлен Bj А - , где

г О;;-0

Л( I С. i И ii, .ОЖ1ю оценить по форп -1

Устройство для неремиожения многочлоюв, содержащее р;егиетры, блоки суммироваиня л блок ун;)авления. о т л i: ч а ю нд е е е я тем, что. с целью новыи1е 1ия быст)юдействия устро;|ства, li i::ro З1згдены коммутато, 6;ioK сдвига и б.лок анализа разрядов онерандов, од1;а Г|)унна входов которого соединена с ввьхода.м.и регистров одного многочлена, а выходы - со входами регистров другого многочлена, выходы которых соединены с одними входами блоков суммирования, выходы которых соединены со входами блока сдвига, выходы которого соединены с одними входами регистров результата, выходы которых соединены со входами коммутатора, выходы которого соединены с другими входами блоков суммироваиия, нричем вход коммутатора, блока сдвига н другие входы регистров результата соединеиы с с()ответству10Н1нмн ввьходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующее устройство | 1974 |

|

SU517894A1 |

| Устройство для умножения многочленов | 1979 |

|

SU783791A1 |

| Устройство для решения дифференциальных уравлений | 1974 |

|

SU526905A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для вычисления значений полиномов вида | 1972 |

|

SU451088A1 |

| Устройство для вычисления функции х= а + в | 1976 |

|

SU646330A1 |

| Устройство для умножения двух @ -разрядных чисел | 1981 |

|

SU964632A1 |

| Устройство для быстрого преобразования Фурье | 1984 |

|

SU1206802A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Устройство для деления | 1976 |

|

SU662938A1 |

Авторы

Даты

1975-12-15—Публикация

1973-03-13—Подача