1

Изобретение относится к электросвязи и может использоваться в системах передачи данных, использующих фазовую или относительную фазовую модуляцию.

Известен адаптивный корректор сигналов с фазовой модуляцией, содержащий широкополосный фазовращатель, источник тактовых колебаний, сумматор, два косинусных преобразователя, выходы которых соединены с входами соответствующих корреляторов, два синусных преобразователя, выходы которых через соответствующие корреляторы соединены с управляющими входами аттенюаторов, первый и второй блоки задержки, фазовый детектор 1.

Однако известный адаптивный корректор имеет иизкую скорость настройки и невысокую помехозащии1,енность.

Цель изобретения - ускорение адаптивной настройки и повыщеиие помехозащищенности.

Для этого в адаптивный корректор сигналов с фазовой модуляцией, содержащий щирокополосный фазовращатель, источник тактовых колебаний, сумматор, два косинусных преобразователя, выходы которых соединены с входами соответствующих корреляторов, два сииусных преобразователя, выходы которых через соответствующие корреляторы соединены с управляюилими входами аттенюаторов, первый и второй блоки задержки, фазовыи детектор, введены отсчетный блок амплитуды, отсчетный блок фазы, первый и второй ограничители амплитуд, три перемножителя, два фазовращателя, фильтр нижних частот и источник опорных колебаний, причем входы широкополосного фазовращателя, первого ограничителя амплитуд и источника тактовых колебаний объединены i являются входом устройства, выходы источника тактовых колебаний ц первого ограничителя амплитуд через отсчетный блок фазы соединены с первым входом первого фазовраи1ателя, первый выход отсчетного блока фазы через второй блок задержки соединен с первым входом второго фазовращателя, а второй выход - с первым входом отсчетного блока амплитуды, выход которого соединен с сигнальным входом первого аттенюатора и через первый блок задержки - с сигнальным входом второго аттенюатора, выходы обоих аттенюаторов через нервый и второй перемножители соединены с первым п вторым входами сумматора соответственно, выход которого через последовательно соединенные фильтр нижних частот п второй ограничитель амнлитуд соединен с первым входом фазового детектора и с первыми входами косинусных и синусных преобразователей, вторые входы которых соединены с выходами соответствующих фазовращателей, соединенными также с другими входами неремножителеи, причем вторые входы оооих фазовращателей соединены с выходами соответствующих корреляторов, другие входы зсех корреляторов соединены с одним из выходов фазового детектора, другой выход которого является выходом устройства, а второй вход фазового детектора через источник опорных колебаний соединен с выходом второго ограничителя амилитуд, ири этом дополнительный выход первого и второго блоков задержки через третий иеремножитель соединен с третьим входом сумматора.

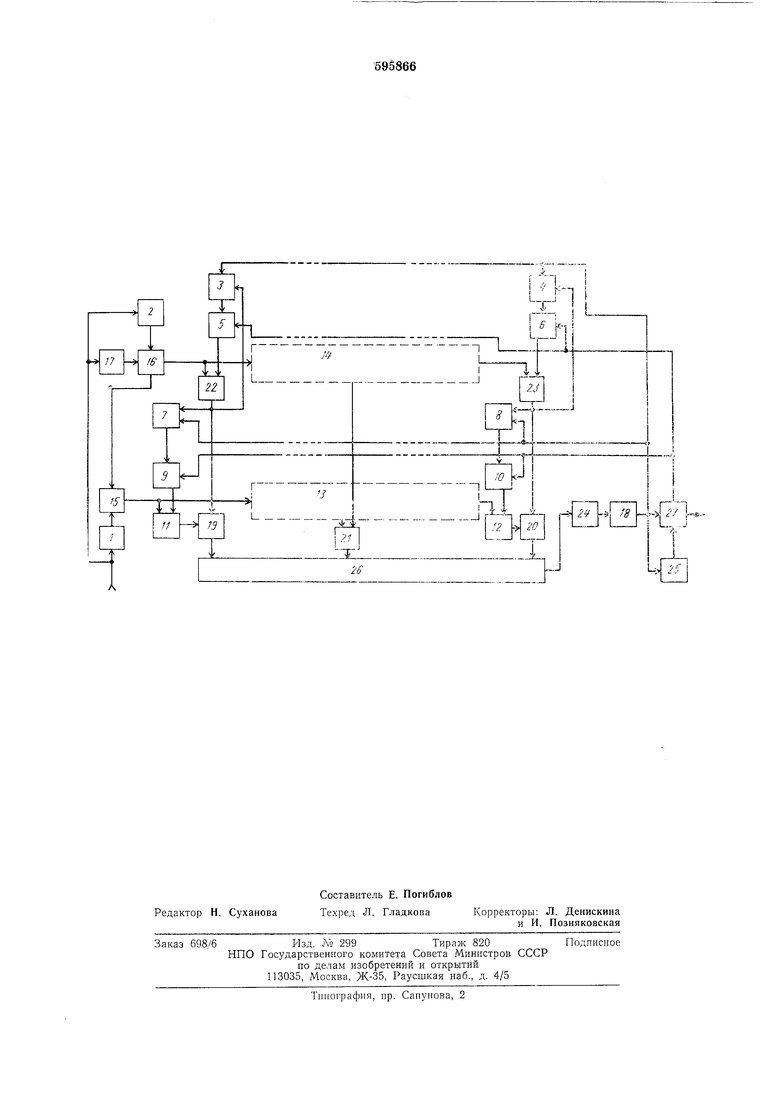

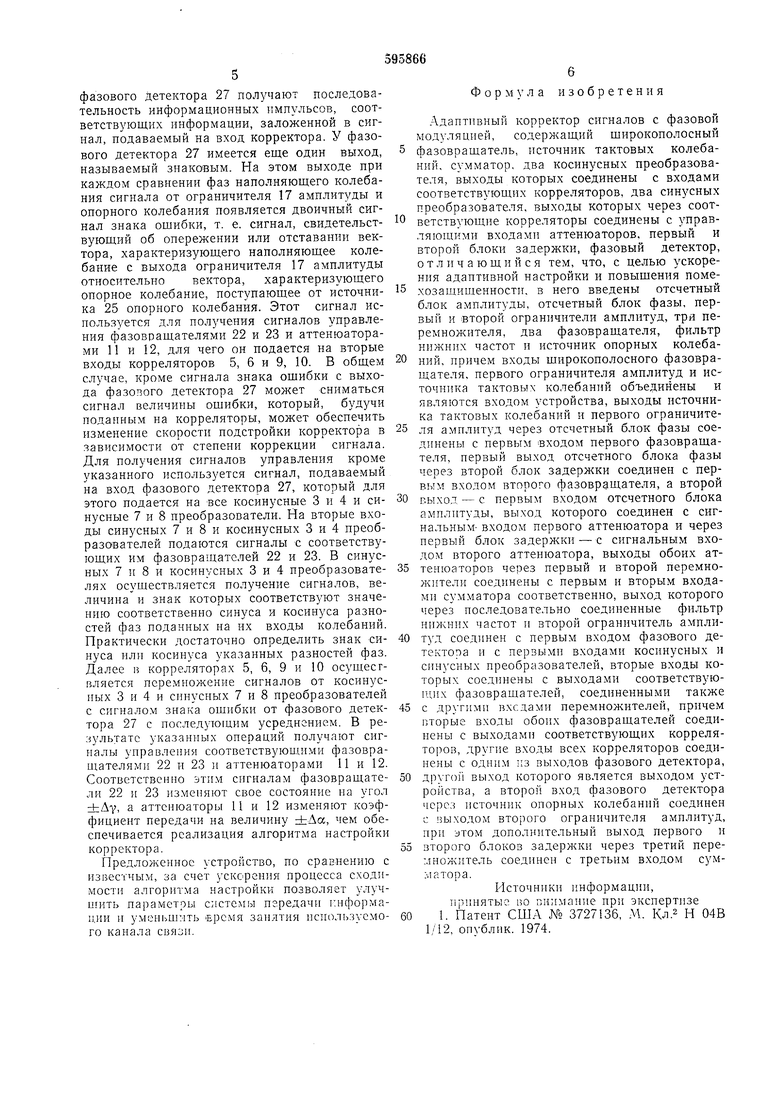

На чертеже изображена структурная электрическая схема предложенного адаптивного корректора.

Адаптивный корректор содержит щирокополосный фазовращатель 1, источник 2 тактовых колебаний, два косинусных преобразователя 3 и 4, выходы которых соединены с входами соответствуюнщх корреляторов 5 и 6, два синусных преобразователя 7 и 8, ВЕЛХОды которых через соответствующие корреляторы 9 и 10 соединены с управляющими входами аттенюаторов И и 12, первый 13 и вто рой 14 блоки задержки, отсчетный блок 15 амплитуды, отсчетный блок 6 фазы, первый 17 и второй 18 ограиичители амплитуд, перемножители 19-21, фазовращатели 22 п 23, с1|ИЛ /гр 24 иижних частот (ФНЧ), источиик 25 опорных колебаний, сумматор 26 и фазовый детектор 27, причем входы щирокоиолосного фазоврап1ателя 1, первого 17 ограничителя акилитуд п источника 2 тактовых колебаний объединены и являютея входом устройства, выходы источиика 2 тактовых колебаний и иервого 17 ограиичителя амплитуд через отсчетиый блок 16 фазы соедииеиы с иервым входом фазовращателя 22, первый выход отсчетпого блока 16 фазы через второй 4 блок задержки соединен с перзым входом фазовраихателя 23, а второй выход- -с nepisbiM входом отсчетного блока 15 амплитуды, выход которого соединен с спгпальиым i3xo;i,oM аттенюатора 11 и через пер)ый 13 блок задержки - с с 1Гнал1)Ным вхолом irroporo аттенюатора 12. выходы обоих атте1 1оато|)ов 11 п 12 через первый 19 и зтоpoii 20 )геремножители соединены с первым и иторым входами сумматора 26 соответствеппо, |;ыход которого через носледонателыга соеди ;еп11ые ФПЧ 24 и второй ограиичитель 18 амплитуд соединс с иервым входом фазового детектора 27 и с первыми входами косинусных 3 и 4 1 синусных 7 и 8 преобразователей, вторые входы которых соединены с выходами соответствуюнщх фазовращателей 22 и 23, сосдиненнымн также с другими входами перемножителей 19 и 20, причем вторые входы обоих фазовращателей 22 и 23 соединены с 1:.ыходами соотвстствуюпнх корреляторов 5 и G, другие входы корреляторов 5, 6 и 9, 10 соедииеиы е одиим з выходов фазового детектора 27, другой которого является выходом устройства, а второй вход фазового детектора 27 через источник 25 онорных колебаНИИ соединен с выходом второго ограиичителя 18 амплитуд, при этом дополнительный выход иервого 13 и второго 14 блоков задерж1 и через третий иеремиож1 тель 21 соедииен с третьим входом сумматора 26.

Адаптивный корректор работает следуюП1ИМ образом.

Входной сигиал подается па отсчетпый блок 16 фазы и отечетный блок 15 амплитуды че)ез ограничитель 17 амплитуды и шнрокополосный фазоврап1ател-з 1 соответственно. Эти блоки по импульсу, поданному от источиика 2 тактовых колебаиий, осущ.еетвляют отсчет указанных параметров сигна.та. Отсчет значений фазы сигнала осупестзляетси путем регистрапии нулевых переееченнй напряжения сигнала, которые следуют сразу после начала тактового нмпульеа. При регистраиии нулевого иересечения отсчетный блок 16 фазы создает имнулье на своем выходе, подключенном к отсчетному блоку 15 амплитуды. Си иалы, соответетвуюн1ие отсчетам входного сигнала, проходят через блоки 13 и 14 задержки с замедлеиием на время одного тактового интервала в каждом элементе. Ма выходах блока 13 задержки ирисутспзуют ciirnajibi постоянпого токи с амп.1иту,;,ой, npcjnopnnojia.union величине модуля амплитуды отсчетов, а на выходах 14 задер/и-си присутствуют сигналы 1) ви;е ирямоу1ольпых имну.1ьсо:5 с частотой следования, рапной частоте necynieго колебкип/; сигнала, екважиостью, равной 2, и с фазами, равными фазам сигнала в соответствующие отсчетные мо.менты времени. Сигиалы с выходов блока 14 задержки, через фазо1)ан.1,атели 22 и 23 открывают и закрывают ключи, которые выиолияют фуикции иеремножнтелей 19---21. Ма входы иеремножителей 19-21 через аттенюаторы 11 и 12 подаютея потеии,иалг)1 е выходов блока 13 задержки. Эти иотеиниалы н юходят па выход перемножнтелей 19- -2 в моменты. ;-.;()Гда они открыты. В результате па их выходах лояв.тяются нрямоуго.л:-:пые лолебан1 я с амжчитудами иервой гармо1П;ки, еоо ветству10И ими амилитудам отсчетов входного сигнала, умио кенн) на ко фгЬиллюипл нередачи аттенюаторов 11 | 12, и с фазами, еоогвотстн Ю Иим1Г ()азам i;xo;iiioro сигнала а моменты отсчетов, со сдвнгам ;, ():1ределием1хми параметрами фазовра :,ателе | 22 и 23. Эти колебания складываются L сумматоре 26. Далее с помоиило фильтра 24 нижних частот ()еущест)ляетея иодаьленне ме иа ОН1мч гар юнич;ских составляющих iiecyn.i.ero колебания. Затем иодвергается ограиичению по амглмтуде i ограничителе 17 амплитуд и ноис.л.ает на фазо1 ый детектор 27 и нсточннк 25 oncjpHbix колебании. В фазозом дет(м :торе 27 происходит сравнение фаз нанолняющего кслебапия сигнала, нос1унаюн1его от огра1 1 Ч1Ггеля 17 амнлитуд н опорного колебания, гюстуиаюндего от источ1нгка 25 онорного колебания. Сравнеине осу1нест15ляется /ю ноложе1иио нулевых 1сч1есечений указанных енгиалов. На выходе

фазового детектора 27 получают последовательность информационных импульсов, соответствующих информации, заложенной в сигнал, подаваемый на вход корректора. У фазового детектора 27 имеется еще один выход, называемый знаковым. На этом выходе при каждом сравнении фаз наполняющего колебания сигнала от ограничителя 17 амплитуды и опорного колебания появляется двоичный сигнал знака ощибки, т. е. сигнал, свидетельствующий об опережении или отставании вектора, характеризующего наполняющее колебание с выхода ограничителя 17 амплитуды относительно вектора, характеризующего опорное колебание, поступающее от источника 25 опорного колебания. Этот сигнал используется для получения сигналов управления фазовращателями 22 и 23 и аттенюаторами И и 12, для чего он подается на вторьте входы корреляторов 5, 6 и 9, 10. В общем случае, кроме сигнала знака ощибки с выхода фазового детектора 27 может сниматься сигнал величины ощибки, который, будучи поданным на корреляторы, может обеспечить изменение скорости подстройки корректора в зависимости от степени коррекции сигнала. Для получения сигналов управления кроме указанного используется сигнал, подаваемый на вход фазового детектора 27, который для этого подается на все косинусные 3 и 4 и синусные 7 и 8 преобразователи. На вторые входы синусных 7 и 8 и косинусных 3 и 4 преобразователей подаются сигналы с соответствующих им фазовращателей 22 и 23. В синусных 7 и 8 и косинусных 3 и 4 преобразователях осуществляется получение сигналов, величина и знак которых соответствуют значению соответственно синуса и косинуса разностей фаз поданных на их входы колебаний. Практически достаточно определить знак синуса или косинуса указанных разностей фаз. Далее в корреляторах 5, 6, 9 и 10 осущесгвляется перемножение сигналов от косинусных 3 и 4 и синусных 7 и 8 преобразователей с сигналом знака ошибки от фазового детектора 27 с последующим усреднением. В результате указанных операций получают сигналы управления соответствующими фазовращателями 22 и 23 и аттенюаторами 11 и 12. Соответственно этим сигналам фазовращатели 22 и 23 изменяют свое состояние на угол +AY, а аттенюаторы И и 12 изменяют коэффициент передачи на величину ±Да, чем обеспечивается реализация алгоритма настройки корректора.

Предложенное устройство, по сравнению с известным, за счет ускорения процесса сходимости алгоритма настройки позволяет улучпить параметры системы передачи информации и уменьшить ьрсмя занятия используемого канала связи.

Формула изобретения

Адантивный корректор сигналов с фазовой модуляцией, содержащий щирокополосный фазовращатель, источник тактовых колебаний, сумматор, два косинусных преобразователя, выходы которых соединены с входами соответствующих корреляторов, два синусных преобразователя, выходы которых через соответствующие корреляторы соединены с управ.тяющими входами аттенюаторов, первый и второй блоки задержки, фазовый детектор, отличающийся тем, что, с целью ускорения адаптивной настройки и повыщения помехозашишенности. в него введены отсчетный блок амплитуды, отсчетный блок фазы, первый и второй ограничители амплитуд, три перемножителя, два фазовращателя, фильтр нижних частот и источник опорных колебаНИИ, причем входы щирокополосного фазовращателя, первого ограничителя амплитуд и источника тактовых колебаний объединены и являются входом устройства, выходы источника тактовых колебаний и первого ограничителя амплитуд через отсчетный блок фазы соединены с первым ВХОДОМ первого фазовращателя, первый выход отсчетного блока фазы через второй блок задерл ки соединен с первым входом второго фазовращателя, а второй

выход - с первым входом отсчетного блока амплптуды, выход которого соединен с сигнальным- входом первого аттенюатора и через первый блок задержки - с сигнальным входом второго аттенюатора, выходы обоих аттенюаторов через первый и второй перемножители соединены с первым и вторым входами сумматора соответственно, выход которого через последовательно соединенные фильтр нижних частот и второй ограничитель амплитуд соединен с первым входом фазового детектора и с первыми входами косинусных и синусных преобразователей, вторые входы которых соединены с выходами соответствующих фазовращателей, соединенными также

с другими входами перемножителей, причем пторые входы обоих фазовращателей соединены с выходами соответствующих корреляторов, другие входы всех корреляторов соединены с одним из выходов фазового детектора,

другой выход которого является выходом устройства, а второй вход фазового детектора через источник опорных колебаний соединен с выходом второго ограничителя амплитуд, при этом дополнительный выход первого и

второго блоков задержки через третий перемножитель соединен с третьим входом сумматора.

Источники информации, принятые 150 пнимание при экспертизе

1. Патент США № 3727136, М. Кл. Н 04В 1/12, опублик. 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный корректор | 1979 |

|

SU866756A2 |

| Адаптивный корректор | 1979 |

|

SU790353A1 |

| Адаптивный корректор | 1977 |

|

SU657626A1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОДНОВРЕМЕННОЙ АМПЛИТУДНОЙ И ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 1991 |

|

RU2019039C1 |

| Селектор эхо-сигнала движущихся целей для двухчастотного радиолокатора | 1984 |

|

SU1841292A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| РАДИОЛИНИЯ СВЯЗИ С ПРОСТРАНСТВЕННЫМ РАЗДЕЛЕНИЕМ СИГНАЛА | 1999 |

|

RU2149506C1 |

| МОДЕМ QPSK, МОДИФИЦИРОВАННЫЙ С ЦЕЛЬЮ СУЩЕСТВЕННОГО ПОВЫШЕНИЯ ЧУВСТВИТЕЛЬНОСТИ ПРИЁМНИКА | 2015 |

|

RU2636577C2 |

| СПОСОБЫ И УСТРОЙСТВА ПОВЫШЕНИЯ ИНДЕКСА УГЛОВОЙ МОДУЛЯЦИИ | 2012 |

|

RU2493646C2 |

Авторы

Даты

1978-02-28—Публикация

1975-07-14—Подача