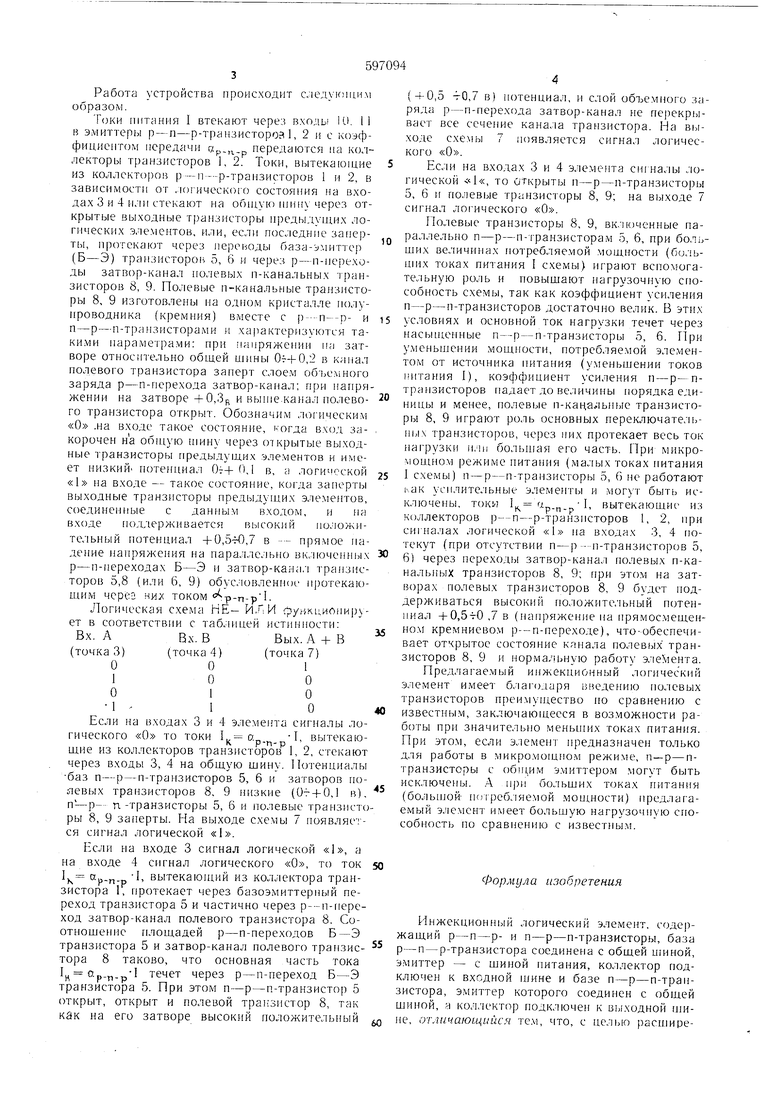

Изобретение относится к области микроэлек троники, а именно к интегральным ннжекционным логическим элементам, выполняющим функцию НЕ-ИЛИ. Известны интегральные полупроводниковые элементы, выполняюпще логические функции, реализуемые как на биполярных транзисторах (IJ, так и на униполярных транзисторах 2), а также комбинированные, содержащие биполярные и униполярные транзисторы 3J, (41 Все указанные известные логические элементы имеют один общий недо.статок - большую потребляемую мошпость. Наиболее близким к предлагаемому техническому решению является инжекционный лоПчческий элемент НЕ-ИЛИ, содержащий р-п-р-транзисторы с общей базой, коллек торы которых являются входами схемы, и п-р-п-траизисторы с общим эмиттером, базы которых соедииены с коллекторами р- -п-ртранзисторов, а коллекторы объединены и являются вь1ходом схемы. Токи питания схемы поступают в эмиттеры р- п--р-траизисторов (5). Недостаток указанного усгройства заключается в том, что потребляемая им моп1ноеть не обеспечивает возможности работы от маломощных источников питания. Цель изобретения расншреиие диапазона рабочих токов в область малых значений и тем самым уменьшение потребляемой мощности. Ностсшленная цель достигается тем, что логический элемент дополнительно содержит полевой п-канальный транзистор с напряжением отсечки, большим нуля, причем нолевой транзистор подключен параллельно п- р- птранзистору. На чертеже представлена принципиальная электрическая схема логического элемента НЕ-ИЛИ, выполненного согласно данному изобретению. Устройство содержит р- п р транзисторы 1, 2, включенные по схеме с общей базой, коллекторы которых являются входами 3 и 4, схемы; п-р--п транзисторы 5 и 6, включенные по схеме с обшим эмиттером, базы которых соедииены с коллекторами р- п- р-транзисторов 1, 2, а коллекторы объединены и являются выходом устройства 7 (А-Ь В), полевые п-каналькые тpaflзиcтopы 8 и 9 с затворами, изолированными р-п переходами, истоки которых соединен- с обшей пп{иой. а затворы со входами 3 и 4 соответственно, а истоки .-- с выходом 7 устройства, эмиттеры р пртранзистором I, 2 являются входами 10, II токов питания устройства.

Работа устройства происходит с;1едук)И1Им образом.

Токи питания I втекают через входь 1U. II в эмиттеры р - п-р-траизистороз 1, 2 и с коэффициентом передачи г/р,,.р передаются на коллекторы транзисторов 1, 2. Токи, вытекающие из коллекторов р-п--р-траизисторов 1 н 2, в зависимости от ,101ическо1Т) состояния на входах 3 и 4 или гтекают на оГ)И1ую через открытые выходные транзисторы 11редыдун1их логических элементов, или, если ноеледние заперты, протекают через переводы база-эмиттер (Б-Э) TpaH3HCTOpOii 5, 6 и через р-п-иереходы затвор-канал нолевых и-канальных транзисторов 8, 9. Полевые н-кана.пьные транзисторы 8, 9 изготовлены иа одном кристалле иолупроводника (кремиия) вместе с р - п--р- и п-р-п-транзисторами и характеризуются такими параметрами: при панряжеиии иа затворе относительно общей илшы Of+0,2 в канал полевого траизистора заперт слоем обьемного заряда р-п-иерехода затвор-каиал; при напряжении на затворе+0,3g и выи1е-канал иолевого траизистора открыт. Обозначим логическим «О .иа входе такое соетояние, когда вход закорочен на общую Н1ину через открытые выходные транзисторы предыдущих элементов и имеет низкий потенциал ОтЧ- Г),1 в, а логической «1 па входе - такое состояиие, когда заперты выходные транзисторы предыдущих элементов, соединеиные с д,анным входом, и па входе поддерживается р,ысокин иоложительный потенциал +0,,7 в -- прямое иадение напряжения на параллельно включенн1)1х р-п-переходах Б-Э и затвор-кана.1 транзисторов 5,8 (или 6, 9) обусловленное протекающим черев НИ.Х током -p-n-pl.

Логическая схема НЕ- Й,ПИ функционирует в соответствии с таблицей истиьиости: Вх. АВх. ВВых. А + В

(точка 3)(точка 4)(точка 7)

0О1

1ОО О 1О

1 1О

Если на входах 3 и 4 элемеша сигналы логического «О то токи 1 к I, вытекающие из коллекторов транзисторов 1, 2, стекают через входы 3, 4 на общую щину. Потенциалы баз п--р - п-транзисторов 5, 6 и затворов полевых транзисторов 8. 9 низкие (От + 0,1 в). .- тт. -транзисторы 5, 6 и полевые транзисторы 8, 9 занерты. На выходе схемы 7 ноявляется сигнал логической «1.

Если на входе 3 сигнал логической «1, а на входе 4 еигнал логичеекого «О, то ток 1 ар.„ -I, вытекающий из коллектора транзистора 1, протекает через базоэмиттерпый переход транзистора 5 и частично через р--п-переход затвор-канал полево1о транзистора 8. Соотноще(И1е площадей р-п-переходов Б-Э транзистора 5 и затвор-канал полевого трапзистора 8 таково, что основная часть тока Ij o. I течет через р-п-нереход Б-Э транзистора 5. При этом п-р-п-транзистор 5 открыт, открыт и нолевой транзистор 8, так как на его затворе высокий положительный

(-fO,o -гО,7 в) нотенциал, и слой объемного заряда р-п-иерехода затвор-канал не перекр)вает все сечение канала транзистора. На выходе схемы 7 появляется сигнал логического «О.

Если на входах 3 и 4 элемента сигналы логической «1«, то открыты и-р-п-транзисторы 5, б и по.;1евые транзисторы 8, 9; на выходе 7 сигнал ло|-ического «О.

Нолевые транзисторы 8, 9, вк.поченные параллельно п-р-п-транзисторам 5, 6, при больших величинах потребляемой мощности (больших токах питания 1 схемы) играют вспомогательную роль и повыщают иагрузочиую енособность схемы, так как коэффициент уеиления п-р-п-транзиеторов достаточно велик. В этих условиях и основной ток нагрузки течет через насыщенные п-р - п-транзиеторы 5, 6. Г1ри уменыиении мощиости, потребляемой элементом от источника нитания (уменьщении токов питарщя I), коэффициент усиления п - р-птранзисторов иЯлтает до величины порядка единицы и менее, полевые п-качальп1;1е транзисторы 8, 9 играют роль основных переключательных транзисторов, через них протекает вееь ток нагрузки иль- большая его часть. При микромощпом режиме иитания (малых токах питания I схемы) и-р-п-траизисторы 5, 6 не работают как усилите.1ьные элементы и могут быть иеключепы. токи (, р-п-р вытекающие из коллекторов р--п-р-транзисторов 1, 2, ири СИ1 палах логической «1 па входах 3, 4 потекут (при отсутствии п-р - и-транзисторов 5, 6) через переходы затвор-канал полевых п-канальных транзисторов 8, 9; при этом на затворах полевых транзисторов 8, 9 будет иоддерживаться высокий положительный исяенииал +0,5тО ,7 в (напряжение на прямосмещенно.м кремниево.м р---п-переходе), что-обеснечивает открытое состояние канала полевых транзисторов 8, 9 и норма/ ьную работу элемента.

Предлагае.мый инжекциоиный логический элемент имеет благодаря введению полевых транзисторов преимуи ество по сравнению с известным, заключающееся в возможности работы при знaчитeль io меныних токах питания. При этом, если элемент нредназначен только для работы в микро.мощно.м режиме, п -р-птранзисторы с общим э.миттером могут быть исключеиы. А при больщих токах нитания (болыной- погребляемой моиишсти) предлагаемый элемент имеет больщую нагрузочную способность по сравпепию с известпы.м.

Формула изобретения

Инжекционпый логический элемент, содержащий р-п-р- и п-р-п-транзиеторы, база р-п - р-транзистора соединена с общей тиной, эмиттер - с щипой гщтания, коллектор подключен к входной тине и базе п-р-п-транзиетора, эмиттер которого соединен с общей щиной, а коллектор подключен к в1мходной тине, отличающийся те.м, что, с целью paemnpeНИИ диапазона рабочих токов в область малых значений, он дополнительно содержит полевой п-канальный транзистор с напряжением отсечки, большим нуля, причем полевой транзистор подключен параллельно п-р-п-транзистору.

Источники инфор,мации, принятые во внимание при экспертизе:

1.Авторское свидетельство . Н 03 К 19/00, 1970.

2.«Электроника, Л 8, 1974, с. 1.

3.Авторское свидетельство N° 352399, Н 03 К 19/08, 1970.

кл.

4.Авторское свидетельство № Зо6789, Н 03 К 19/08, 1970.

кл.

5.«Электроника, № 4, 19/4, с. 42, . 12 о.

| название | год | авторы | номер документа |

|---|---|---|---|

| Согласующий усилитель | 1974 |

|

SU660196A1 |

| Интегральная логическая схема | 1977 |

|

SU633395A1 |

| Аналоговый ключ | 1977 |

|

SU684741A1 |

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Триггер | 1974 |

|

SU595847A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕКЛЮЧЕНИЯ ЗНАКОПЕРЕМЕННЫХ АНАЛОГОВЫХ СИГНАЛОВ | 1973 |

|

SU385287A1 |

| Каскодный усилитель типа общий сток - общая база | 2016 |

|

RU2617930C1 |

| Двоичный делитель частоты @ типа | 1983 |

|

SU1112533A1 |

| ИНТЕГРАЛЬНАЯ СХЕМА СИЛОВОГО БИПОЛЯРНО-ПОЛЕВОГО ТРАНЗИСТОРА | 2015 |

|

RU2585880C1 |

| Логический элемент | 1978 |

|

SU729847A1 |

W

Авторы

Даты

1978-03-05—Публикация

1974-11-27—Подача