Изобретение относится к электронике, вычислительной технике и может быть использовано при создании больших интегральных схем на МДП приборах.

Известна преобразующая схема с тремя выходными состояниями на полевых транзисторах, содержащая входной элемент ИЛИ-НЕ, инвертор и выходной формирователь, состоящий из пяти транзисторов 1.

Известна также схема преобразования с трехуровневым выходным сигналом, содержащая входные элементы ИЛИ-НЕ, И-НЕ и выходной формирователь, состоящий из четырех транзисторов 2.

Недостатками преобразующих схем являются сложность выходных формирователей и малое быстродействие.

Наиболее близким к изобретению по технической сущности является формирователь с тремя состояниями, состоящий из КМДМ-инвертора, двух логических схем, выполняющих функцию элементов ИЛИ-НЕ и состоящих из четырех дополняющих транзисторов каждая, выходных транзисторов - биполярного п-р-п и п-канального полевого, причем эмиттер выходного транзистора подключен к стоку полевого выходного транзистора и к выходу устройства, база подключена к выходу первой логической схемы, на входы которой подаются блокирующий и входной сигналы, коллектор подключен к щине питания, исток полевого выходного транзистора подключен к общей щине, а затвор - к выходу второй логической схемы, на входы которой подаются блокирующий сигнал и инвертированный входной сигнал с выхода инвертора 3.

Недостатками известной схемы являются ее сложность и малое быстродействие, так как управление выходными транзисторами осуществляется через два последовательно включенных р-канальных транзистора логических схем.

Цель изобретения - упрощение схемы и повышение быстродействия.

Поставленная цель достигается тем, что в устройство, содержащее КМДП-инвертор, вход которого подключен к первому входу формирователя два блокирующих п-канальных МДП-транзистора, истоки которых соединены с общей шиной, а затворы подключены к второму (блокирующему) входу формирователя, выходной биполярный п-р-п-транзистор, база которого соединена со стоком первого блокирующего транзистора, а коллектор подключен к шине питания, выходной п-канальный МДП-транзистор, затвор которого соединен со стоком второго блокирующего транзистора, исток подключен к общей щине, а сток соединен с эмиттером выходного биполярного п-р-п транзистора и .выходом формирователя, введены две пары КМДП-транзисторов,

СОСТОЯЩИХ из р- и п-канальных транзисторов, причем стойки первой пары КМДПтранзисторов подключены к базе биполярного транзистора, а истоки - к выходу инвертора, затвор р-канального транзистора первой пары КМДП-транзисторов соединен с вторым (блокирующим) входом формирователя, затвор п-канального транзистора этой же пары КМДП-транзисторов соединен с третьим входом формирователя стоки второй пары КМДП-транзисторов подключены к затвору выходного п-канального КМДП-транзистора, а истоки - к первому входу формирователя, затворы р- и п-канальных транзисторов второй пары КМДП транзисторов подключены соответственно к затворам р-и п-канальных транзисторов первой пары КМДП-транзисторов.

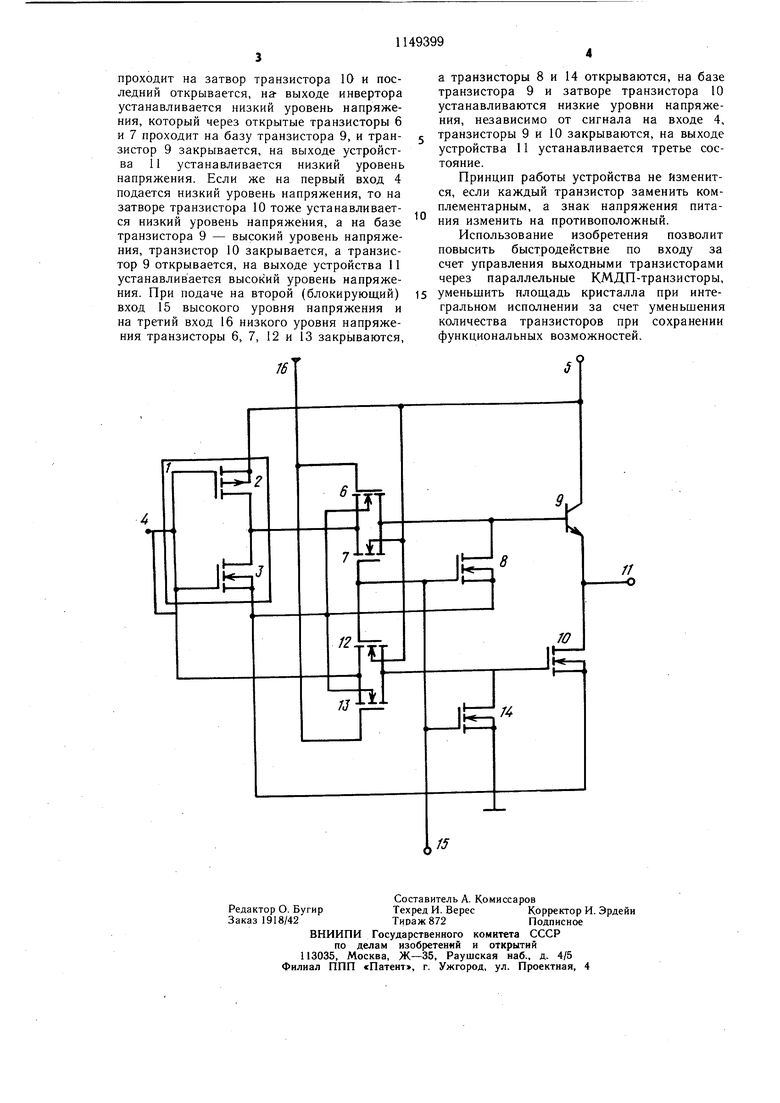

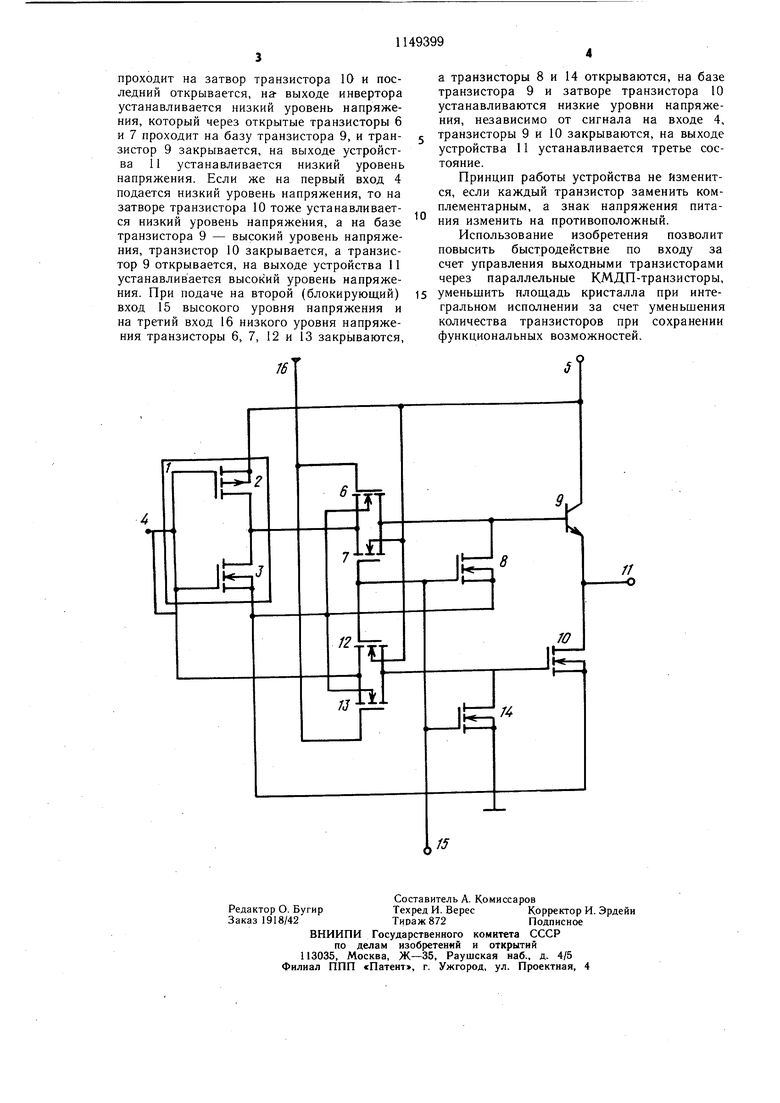

На чертеже представлена принципиальная электрическая схема формирователя с тремя состояниями на выходе.

Устройство содержит КМДП-инвертор 1, выполненный на транзисторах 2 и 3, причем здтворы транзисторов подключены к первому входу устройства 4, сток транзистора 2 подключен к шине 5 питания, а исток соединен со стоком транзистора 3 и является выходом инвертора, подключенным к истокам первой пары КМДП-транзисторов 6 и 7, стоки которых объединены и подключены к стоку первого блокируюш,его транзистора 8 и к базе биполярного п-р-птранзистора 9, коллектор которого подключен к шине 5 питания, а эмиттер соединен со стоком выходного п-канального МДП транзистора 10 и подключен к выходу устройства И. Истоки второй пары КМДПтранзисторов 12 и 13 подключены к первому входу устройства 4, а их стоки объединены и подключены к затвору выходного п-канального МДП-транзистора 10 и к стоку второго блокирующего транзистора 14, затвор которого соединен с затворами рканальных транзисторов 7 и 12, с затвором транзистора 8 и подключен к второму входу устройства 15, затворы п-канальных транзисторов б и 13 подключены к третьему входу устройства 16, истоки транзисторов 3, 8, 14, 10 подключены к общей шине, подложки транзисторов 12 н 7 подключены к шине 5 питания, а подложки транзисторов 13 и 6 подключены к общей шине.

Устройство работает следующим образом.

При подаче на второй (блокирующий) вход 15 низкого уровня напряжения и на третий вход 16 высокого уровня напряжения транзисторы 8 и 14 закрываются, а транзисторы 6, 7, 12, 13 открываются. Если теперь на первый вход 4 подается высокий уровень напряжения, то через открытые транзисторы 12 и 13 этот сигнал

проходит на затвор транзистора 10 и последний открывается, на- выходе инвертора устанавливается низкий уровень напряжения, который через открытые транзисторы 6 и 7 проходит на базу транзистора 9, и транзистор 9 закрывается, на выходе устройства 11 устанавливается низкий уровень напряжения. Если же на первый вход 4 подается низкий уровень напряжения, то на затворе транзистора 10 тоже устанавливается низкий уровень напряжения, а на базе транзистора 9 - высокий уровень напряжения, транзистор 10 закрывается, а транзистор 9 открывается, на выходе устройства 11 устанавливается высокий уровень напряжения. При подаче на второй (блокирующий) вход 15 высокого уровня напряжения и на третий вход 16 низкого уровня напряжения транзисторы 6, 7, 12 и 13 закрываются

а транзисторы 8 и 14 открываются, на базе транзистора 9 и затворе транзистора 10 устанавливаются низкие уровни напряжения, независимо от сигнала на входе 4 транзисторы 9 и 10 закрываются, на выходе устройства 11 устанавливается третье состояние.

Принцип работы устройства не изменится, если каждый транзистор заменить комплементарным, а знак напряжения питания изменить на противоположный.

Использование изобретения позволит повысить быстродействие по входу за счет управления выходными транзисторами через параллельные КМДП-транзисторы,

уменьшить площадь кристалла при интегральном исполнении за счет уменьшения количества транзисторов при сохранении функциональных возможностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Двоичный счетчик | 1984 |

|

SU1282321A1 |

| Устройство согласования уровней напряжения на КМДП-транзисторах | 1985 |

|

SU1483628A1 |

| Преобразователь напряжения | 1978 |

|

SU771817A1 |

| Инвертор | 1991 |

|

SU1817240A1 |

| ЛОГИЧЕСКОЕ (МНОГОФУНКЦИОНАЛЬНОЕ) УСТРОЙСТВО ГЕНИНА А.И. (ВАРИАНТЫ) | 1992 |

|

RU2081509C1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| Тактируемый триггер на комплементарных МДП-транзисторах | 1985 |

|

SU1499435A1 |

| Коммутатор напряжений | 1988 |

|

SU1524168A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

ФОРМИРОВАТЕЛЬ С ТРЕМЯ СОСТОЯНИЯМИ НА ВЫХОДЕ, содержащий КМДПИнвертор, вход которого подключен к первому входу формирователя, два блокирующих п-канальных МДП-транзистора, истоки которых соединены с общей шиной, а затворы подключены к второму (блокирующему) входу формирователя, выходной биполярный п-р-п-транзистор, база которого соединена с6 стоком первого блокирующего транзистора, а коллектор подключен к шине питания, выходной п-канальный МДП-транзистор, затвор которого соединен со стоком второго блокирующего транзистора, исток подключен к общей шине, а сток соединен с эмиттером выходного биполярного п-р-п-транзистора и выходом формирователя, отличающийся тем, что, с целью повышения быстродействия, в него введены две пары КМДПтранзисторов, состоящих из р- и п-канальных транзисторов, причем стоки первой пары КМДП-транзисторов подключены к базе биполярного транзистора, а истоки - к выходу инвертора, затвор р-канального транзистора первой пары КМДП-транзисторов соединен с вторым (блокирующим) входом формирователя, затвор п-канального транзистора этой же пары КМДПi транзисторов соединен с третьим входом формирователя, стоки второй пары КМДП(Л транзисторов подключены к затвору выходного п-канального КМДП-транзистора, а истоки - к первому входу формирователя, затворы р- и п-канальных транзисторов второй пары КМДП-транзисторов подключены соответственно к затворам р- и п-канальных транзисторов первой пары КМДП-транзисторов. 4 оо со Х)

8

Ц|

П

JF

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-04-07—Публикация

1983-01-11—Подача