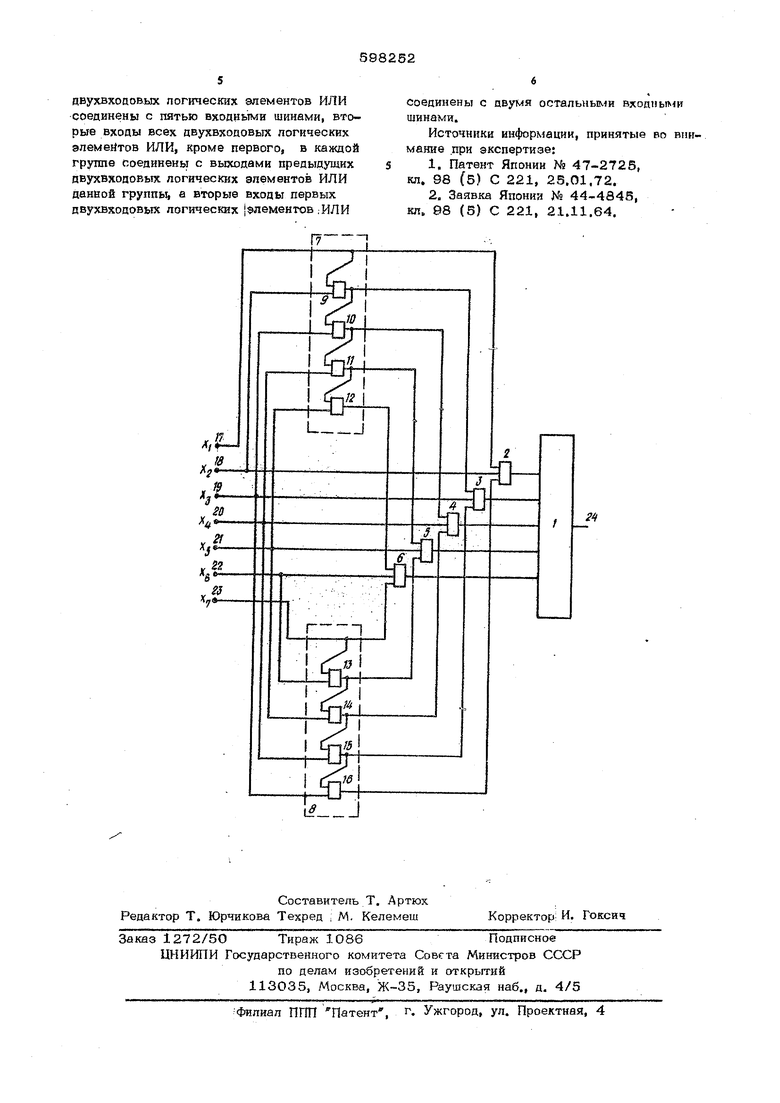

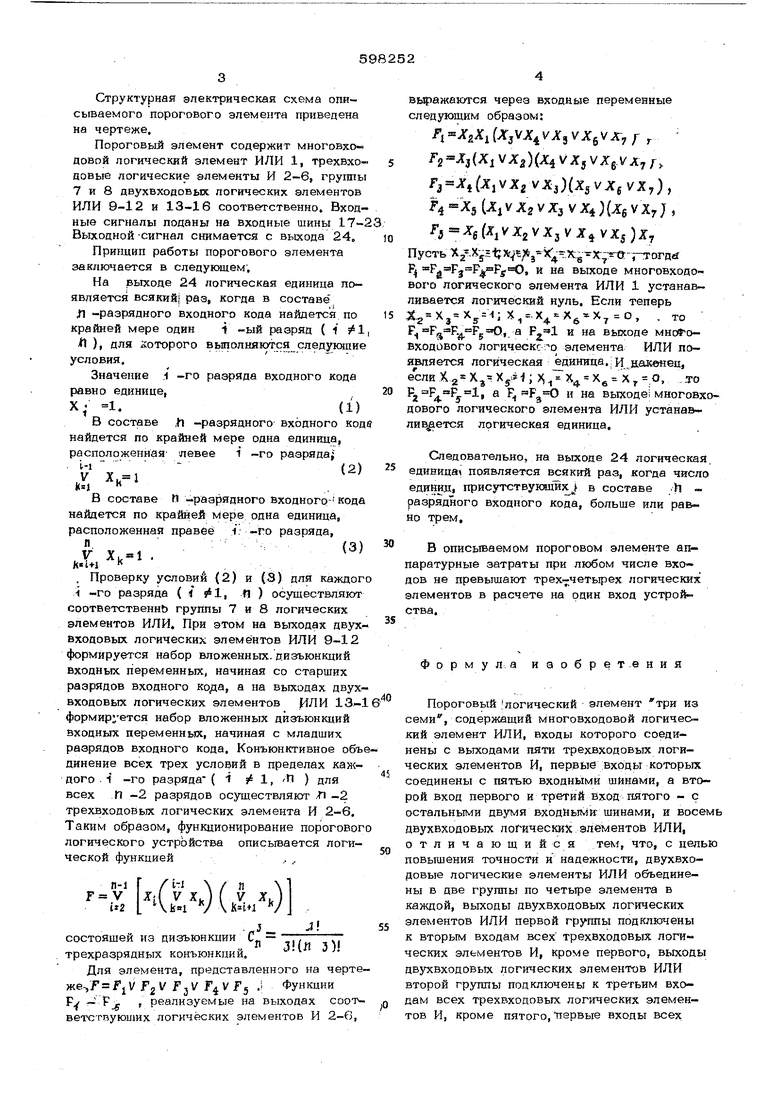

Структурная электрическая схема описываемого порогового элемента приведена на чертеже. Пороговый элемент содержит многовходовой логический элемент ИЛИ 1, трехвходовые логические элементы И , группы 7 и 8 двухвходовьгх логических элементов ИЛИ 9-12 и 13-16 соответственно. Входные сигналы поданы на входные шины 17Выходной -сигнал снимается с выхода 24. При1щип работы порогового элемента заключается в следующем; На рыходе 24 логическая единица появляется всякий, раз, когда в составе Л -разрядного входного кода найдется по крайней мере один i ый разряд ( 1 Л ), для которого вьшолняются следукниие условия. Значение i -го разряда входного кода равно единице, В составе ,li -разрядного входного код найдется по крайней мере одна единица, расположенная- левее i -го разряда; 1-1 -(2) / Ksj В составе П -разрядного входного- кода найдется по крайней мере одна единица, расположенная правее 1- -го разряда, П,(3) . х.,1. К«1+1 . . Проверку условий (2) и (3) для каждог л -го разряда ( , п) осуществляют соответственнЬ группы 7 и 8 логических элементов ИЛИ. При этом на вьгходах двух входовых логических элементов ИЛИ 9-12 формируется набор вложенных, дизъюнкций входных переменных, начиная со старших разрядов входного кода, а на вьпсодах двух входовых логических элементов ИЛИ 13.формируется набор вложенных дизъюнкций Входных переменных, начиная с младших разрядов входного кода. Конъюнктивное объ динение всех трех условий в пределах каждого . i -го разряда- (1 5 1, Я ) для всех П -2 разрядов осуществляют /П -2 трехвходовых логических элемента И 2-6. Таким образом, функционирование пороговог логического устройства описьгоается логической функцией, , П-1 Г /1-J / -У Ut( V Х. ( V Xj i«2 V V J . j. 3(n 3)j состоящей из дизъюнкции трехразрядных конъюнкции. Для элемента, представленного на черте FzV F-jV FS .i Функции Fv - t реализуемые на выходах соответствующих логических элементов И 2-63, вьфажаются через входные переменные следующим образом: FI ад iXjVX /JTj VXg V ЛГу ;- , ()( (jC,VX2 v;C3)Us VXy) , 1-4 «Xj UjVAjVXj VX4)Ug VXyb FS g ( VXj V f VXj )X Пусть 2 Xj.1; j xf -KQ-x- tir ттогдй 4 и на выходе многовходового логического элемента ИЛИ 1 устанавливается логический нуль. Если теперь 3 5i - ТО , а и на выходе мнсГоБходового логичеекс io элемента ИЛИ появляется логическая единица.: и даквнеи, ecnHX2 X. Xg х О, то , а F и на выходе многовходового логического элемента ИЛИ устанавливеется логическая единица. Следовательно, на выходе 24 логическая. единица появляется всякргй раз, когда число единиц, присутствующих в составе /h разрядного входного кода, больше или равно трем, В описьдааемом пороговом элементе аппаратурные затраты при любом числе входов не превышают трех четырех логических элементов в расчете на один вход устройства. Формула изобретения Пороговый .логический элемент три из семи, содержащий многовходовой логический элемент ИЛИ, входы которого соединены с вьтходами пяти трехвходовых логических элементов И, первые -входы которых соединены с пятью входными шинами, а второй вход первого и третий вход пятого - с остальными двумя входными шинами, и восемь двухвхоаовых логических элементов ИЛИ, отличающийся тем, что, с целью повышения точности и надежности, двухвходовые логические элементы ИЛИ объединены в две группы по четьфе элемента в каждой, выходы двухвходовых логических элементов ИЛИ первой группы подключены к вторым входам всех трехвходовых логических элементов И, кроме первого, выходы двухвходовых логических элементов ИЛИ второй группы подключены к третьим входам всех трехвходовых логических элементов И, кроме пятого, первые входы всех

двухвходовых логических элементов ИЛИ соединены с пятью входньУми шинами, вторые входы всех двухвходовых логических элемейтов ИЛИ, кроме первого, в каждой группе соединены с выходами предыдущих пвухвходовых логических элементов ИЛИ данной группы в вторые входы первых двухвходовьгх логических |9лементов .ИЛИ

Соединены с двумя остальными входньгми шинами.

Источники информации, принятые во внимание при экспертизе:

1.Патент Японии Ng 47-2725, кл. 98 (5) С 221, 25.01,72.

2.Заявка Японии № 44-4845, кл. 98 (5) С 221, 21.11.64.

2ii

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля кода "2 из п " | 1976 |

|

SU622085A1 |

| ОДНОТАКТНЫЙ УМНОЖИТЕЛЬ ДВОИЧНЫХ ЧИСЕЛ | 1988 |

|

RU2012039C1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Сумматор-вычитатель | 1988 |

|

SU1536373A1 |

| Матричное устройство параллельного поиска составного образца | 2021 |

|

RU2776602C1 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Устройство для сравнения кодов | 1982 |

|

SU1080134A1 |

| Управляемый двигатель частоты | 1985 |

|

SU1325691A1 |

Авторы

Даты

1978-03-15—Публикация

1976-05-07—Подача