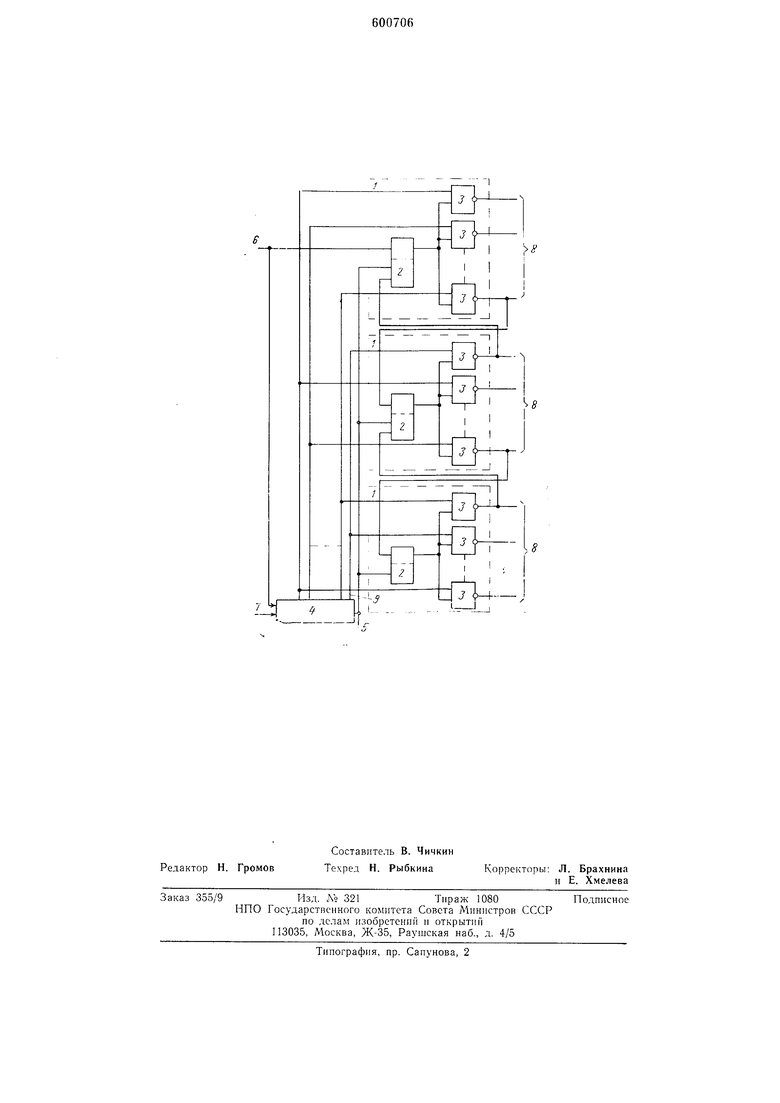

третьей ячейки даны для частного случая, когда опорный распределитель немеет четыре выхода Вмсстс с доиоЛННтельным.

Сигнал -сброса, подаваемый по шине 5, устанавливает в исходное состояние опорный распределитель 4, а также триггеры 2 выходных ячеек I. Переключаясь но сигналу сброса, все триггеры 2 снимают разрешающие сигналы с вентилей 3. Орн ноступле«ии« по шине 6 сигнала запуска выключаются опорный распределитель 4 и триггер 2 нер-вой выходной ячейки 1. С выхода триггера на вентили 3 иоступает сигнал, разрешаюший прохождение иа выходные шины 8 иоследовательно распределенных во временИ сигналов опорного распределителя 4. Последни-й в-ыходно-й еигнал первой ячейки включает триггер 2 второй выходной ячейки. Возникаюш;ий велед за этим сигнал «а дополнительном входе 9 опорного распределителя 4 проходит только на выход второй ячейки и через ее первый вентиль выключает тритгер 2 первой ячейки. Появляющийся вслед за этнм на нервом выходе опорного распределителя им пульсов 4 сипнал проходит на второй выход второй ячейки и т. д. Импульсный сигнал па вьгходе первого вентиля каждой выходной ячейки 1 выключает триггер 2 предыдущей ЯЧейки. Таким образом осуществляется последовательное подключение выходных ячеек 1 к опорному распределителю Импульсов 4.

Применение предлагаемого распределителя импульсов повышает надежность устройств и упрощает их схему.

Формула и 3 о б р е т е н И я

Распределитель имиульсов, содержащий V-разрядный опорный распределитель и однотипные вьгходные ячейки, состОЯЩие каждая из триггера и элементов И-ПЕ, подключенных однИМИ входами к единичному выходу триггера, а другими входами - к вьрходам опорного распределителя, отличающийся

тем, что, с целью повышения надежности и упрощения, каждая выходная ячейка содержит (Л-1) двухвходовых элементов И-ПЕ, иричем выход (Л-1)-го элемента И-ПЕ каждой предыдущей ячейки соединен с едиН114 пым входом триггера последующей ячейки, нулевой вход каждого предыдущего триггера подключен к выходу первого элемента И-ПЕ последующей ячейки, входы элементов П-ПЕ иервой ячейки соединены соответственно с первыми (N-1) выходами опорного распределителя, входы элемента И-ПЕ иоследующих ячеек соединены с () выходами опорного распределителя, сдвинутыми по кольцу относительно первого, выхода иа

соответствующее число разрядов так, что вход иервого элемента П-ПЕ второй ячейкн соедине-н с Л-м вькодом оиорного распределителя.

Псточники информации.

принятые во виимание при экспертизе

1.Букреев П. П. и др. Микроэлектронные схемы цифровых устройств. «Советское радио, М., 1973, с. 233, рис. 6,26.

2.Авторское свидетельство СССР №312376. кл. П ОЗК 5/13, 1970.

2-Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки импульсов | 1975 |

|

SU560330A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ | 1970 |

|

SU277841A1 |

| Контрольное устройство приема информации | 1972 |

|

SU469130A1 |

| Распределитель импульсов | 1982 |

|

SU1050105A1 |

| Специализированная электронная машина для анализа определителей | 1969 |

|

SU481037A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| УСТРОЙСТВО для ПОИСКА ПРАДЕРЕВЬЕВ НАПРАВЛЕННОГО ГРАФА | 1968 |

|

SU212633A1 |

| Асинхронный распределитель | 1981 |

|

SU1018245A1 |

| Асинхронный распределитель | 1983 |

|

SU1249714A1 |

| Многофункциональная логическая схема | 1973 |

|

SU490119A1 |

Авторы

Даты

1978-03-30—Публикация

1974-11-18—Подача