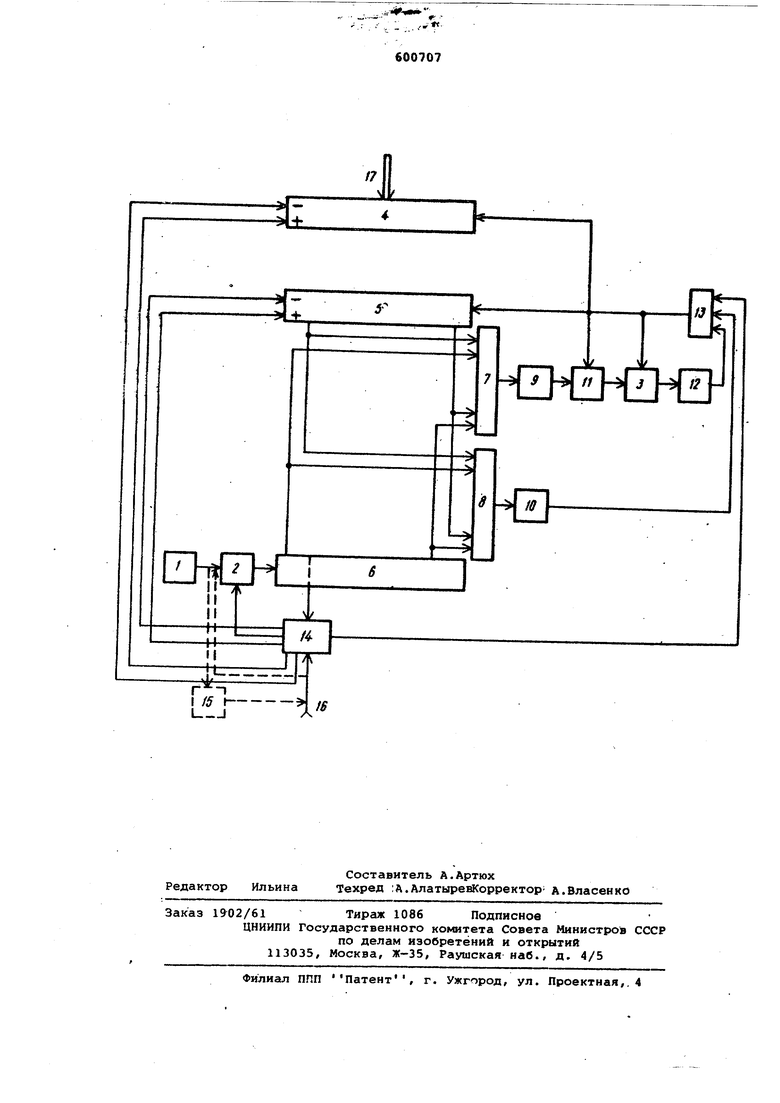

первого делителя частоты соединен с выходом первого из упомянутых блоков логических элементов И, а его выход подключен ко BTOpoNty входу триггера, второй делитель частоты включен между третьим входом логического элемента ИЛИ и выходом второго блока логических элементов И, при этом вторые входы логических элементов И, объединенных в упомянутые блоки,соединены с выходами разрядов Второго реверсивного счет чика. На чертеже приведена структурная электрическая схема преобразователя. Преобразователь содержит генератор образцовой частоты 1, ключи 2 и 3, реверсивные счетчики 4 и 5, суммирующий счетчик 6, блоки 7 и 8 логических элементов И, делители 9 и 10 частоты импульсов, триггер 11, элемент 12.эадерЖ ки, логический элемент ИЛИ 13, блок 14 управления и делитель 15 частоты.На вход 16 подан сигнал преобразуемой частоты. Источники питания и сигналовна чертеже не,показаны. Работает устройство следующим образом. В исходном состоянии счетчики 5 и 6 и триггер 11 находятся в нулевом состо янии, ключи 2 и 3 закрыты. Блок 14 открывает ключ 2 на время, равное периоду Т, преобразуемой частоты i . В течение этого времени импульсы генерато ра 1 с частотой следования i поступают на вход счетчика б. При поступлении на вход счетчика б числа импуль, сов 1 в течение времени Ч К / сигнал со счетчика б поступает на блок 14 .и импульс с выхода последнего проходит через элемент 13 на вход счетчика 5 и устанавливает его триггеры (не показаны) в единичное состояние. Этот же импульс опрокидывает триггер 11 в единичное состояние, что приводит к ртрыванию ключа 3. Логические элементы блоков 7 и 8 являются двухвходовыкда. Входы каждого из них в блоке 8 подключены к выходам одного из триггеров (не пбказаны) счет чика 5 и одного из триггеров ( не показаны) счетчика б, причем если один из его входов подключен к триггеру младшего разряда счетчика 5, то второй вход подключается к триггеру старшего разряда счетчика б и наоборот. Импульс появляется на выходе того из элементов блока 8 который подключен к находящемуся в единичном состоянии триггеру счетчика 5 и переходящему из нуле вого в единичное состояние триггеру счетчика 6. Средняя частотаГдСледования импульсов на выходе блока 8, опрееляемая частотой ig импульсов,посупающих на вход счетчика б и числом д{-1) , находящимся в счетчике 5, авна . foNjW - коэффициент пересчета счетИмпульсы на выходе блока 8 вызываются импульсами, поступающими на вход счетчика б после установки триггеров счетчика 5 в единичное состояние. Импульсы с частотой ig поступают на вход делителя 10. Частота i (j импульсов, поступающих с выхода делителя 10, определяется выражением je ° где /3 - коэффициент деления делителя 10. Импульсы с частотой f ,(, поступают через элемент 13 на вход счетчика 5 и вызывают появление импульсов на выходе блока 7. Элементы блока 7 подключены аналогично элементам блока 8. Средняя частота j. на выходе блока 7, определяемая частотой f ,j импульсов, поступающих с выхода элемента 13 на вход счетчика 5 и числам N(t находящимся в счетчике б, равна , ,() Импульсы с частотой f поступают на вход делителя 9, частота на выходе которого представляется выражением ) где 00 - коэффициент деления делителя 9 Импульсы с частотой 1 i с выхода элемента 13 поступают через открытый ключ 3 на вход элемента 12 и далее на второй вход элемента 13-до тех пор, пока импульс с выхода делителя 9 не опрокинет триггер Ив нулевое состояние и сигналом с выхода последнего ключ 3 закроется. Перевод триггера 11 в единичное состояние осуществляется очередным импульсом, поступающим на одиночный вход триггера 11с выхода элемента 13, причем этот импульс не проходит через ключ 3 и тем самым исключается из счета. Частота ij импульсов, поступающих с выхода ключа 3, равна разности частот f ,j и iy импульсов, поступающих с выхода элемента 13 и делителя 9, соответственноЧастотами импульсов, поступающих с выхода элемента 13, равна сумме частот, поступающих на ее входы и определяется выражением

,0

IS

или i (t) li- ) Всего на счетчике 6 с учетом первы Kf импульсов к моменту времени t t поступило количество импульсов 4U)--ioi Окончательное выражение для f ,3 примет вид с - о-ХдСО ct KfiCt) / -fo-fc ft -i При работе счетчика 5 в режиме вычитания число в последнем уменьшается с момента времени i j от величины (М) и в момент окончания периода Т часто ты f достигнет величины:()У При работе счетчика 5 в режиме сложения сигнал со счетчика б при пос туплении на его вход К импульсов поступает на вход блока 14 и импульс с выхода последнего пройдет через эле мент 13 на вход счетчика 5 и установи его младший разряд {не показано) в единичное состояние. Дальше устройство будет работать как и в предыдущем случае, но число в счетчике 5 будет увеличиваться. Записав первоначально в счетчик число m в прямом или дополнительное кодах, при работе счетчика 4 в режимах сложения и вычитания получим величины, обратные выходным характеристикам датчиков : W 1 К f w Преобразователь может быть применен и для функционального преобразова ния высоких частот. Для этого в схему устройства должны быть внесены следую щие изменения: выход генератора 1 через делитель 15 подключается ко входу блока 14; преобразуемая частота подается на вход ключа 2. В преобразователе результат получаем за время, равное периоду преобр зуемой частоты при преобразовании ни инфрани ких и VC-) Х К. f ких частот, или за время измерения п образуемой частоты преобразования ср

них и высоких частот,

т.е. повышается быстродействие. Формула изобретения Цифровой,преобразователь частоты, содержащий генератор образцовой частоты, выход которого через первый ключ соединен со входом суммирующего счетчика, выходы разрядов которогоподключены к первым входам логических элементов И, объединенных в два блока, и лохИческиЯ элемент ИЛИ, первый вход которого соединен с выходом блока управления, а второй чере последовательно соединенные элемент задержки и второй ключ соединен с выходом триггера, причем входы триггера и второго ключа соединены с выходом логического элемента ИЛИ, второй выход блока управления соединен со вторым входом первого ключа, а вход блока управления соединен со входом преобразователя, отличающийся тем, что, с целью повышения быстродей-ствия, в него введены два реверсивных счетчика и два делителя частоты импульсов, причем входы Сложение и Вычитание реверсивных счетчиков соединены с дополнительными выходами блс ка управления, а их входы управления объединены и подключены к выходу логи ческого элемента ИЛИ, вход первого делителя частоты соединен с выходом первого из упомянутых блоков логических элементов И, а его выход подключен ко второму входу триггера, второй делитель частоты включен между третьим входом логического элемента ИЛИ и выходом второго блока логических элементов И, при этом вторые входы логических элементов И, объединенных в упомянутые блоки, соединены с выходами разрядов второго реверсивного счетчика . Источники информации, принятые во внимание при экспертизе: 1.Патент США 3573125,кл., 11.06.73. 2.Авторское свидетельство СССР № 300956, кл. Q 01 R 23/02,10.02.69.

1

fS

8

to

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь частоты следования импульсов в код | 1975 |

|

SU554507A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Функциональный преобразователь частоты следования импульсов | 1975 |

|

SU553623A1 |

| Преобразователь частоты в код | 1975 |

|

SU600470A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1989 |

|

RU2028731C1 |

| Цифро-аналоговый преобразователь | 1977 |

|

SU690624A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1979 |

|

SU862150A1 |

| Устройство преобразования медленноменяющейся частоты в код | 1977 |

|

SU687589A1 |

Авторы

Даты

1978-03-30—Публикация

1975-11-14—Подача