Изобретение относится к измерител ной технике и автоматике и может най ти применение в качестве преобразователей сигналов частотных датчиков сигналов аналоговых преобразователей напряжение - код с промежуточным пре образованием в частоту, Известно устройство преобразовани меняющейся частоты в код, которое представляет собой частотомер средне го значения, . содержащее устройство управления, генератор импульсов и счетчики, соединенные с устройством управления 1. Однако код, вырабатьшаел«лй этим устройством, не соответствует мгновенному значению преобразуемой частоты ни в начале, ни в конце интервала преобразования. Наиболее близким по технической сущности к изобретению является преобразователь, содержащий последовательно соединенные элементы И и счет чик импульсов, при этом управляющий вход элемента И подключен ,к устройст ву управления, второй элемент И, одним входом подключенный к источнику преобразуемой.частоты, а вторым - к устройству управления, а также допол нительные счетчик среднего значения, схему переноса кода и функциональный генератор импульсов (2, Однако для нормальной работы этого устройства необходимо знать эаранее скорость изменения преобразуемой частоты для того, чтобы имелась возможность управлять частотой функционального генератора импульсов, а также то, что перед началом фиксированного интервала времени в счетчик среднего значения должно заноситься некоторое число, пропорциональное разностной частоте за этот фиксированный интервал времени. Кроме того отсутствие у устройства управления входов, на которые подавалась бы измеряемая частота, приводит к принципиальной невозможности автоматического определения разностной частоты, а следовательно и невозможности автоматического изменения частоты функционального генератора импульсов. Следовательно известное устройство принципиально не в состоянии при описанных связях обеспечить преобразование медпенноменяющейся частоты в код. Все это .вместе взятое приводит fK сложности процесса подготовки известного устройства к преобразованию и ограничивает;функциональные воз1 йжности ycTpoflctBa преобразованием |частот, меняющихся с постоянной и заранее известной скоростью.

Целью изобретения является упрощение процесса измерения, повышение надежности и расширение диапазона изменения преобразуемых частот.

Достигается это тем, что в устройство для преобразования медленноменяющейся частоты в код, содержащее два элемента И, управляющие входы которых подключены соответственно к первому и второму выходам блока управления, вход первого элемента И подключен к входной шине устройства и реверсивный счетчик, дополнительно введены два элемента И и дешифратор, причем входы второго и двух дополнительных элементов И подключены к входной шине устройства, выходы первого и второго элементов И подключены соответственно к первому и второму суммирующим входам реверсивного счетчика, к вычитающим входам которого подключены выходы дополнительных элементов И, выходы реверсивного счетчика поразрядно соединены с входами дешифратора, выход которого подключен к входу блока управления, третий и четвертый выходы которого соединены с управляющими входами соответственно первого и второго дополнительных элементов И; блок упрайления содержит пять установочных триггеров, счетный триггер, четыре элемента ИЛИ, пять элементов И, два формирователя коротких импульсов, генератор импульсов, пересчетную схемур элемент задержки и элемент НЕ, причем выход генератора импульсов через последовательно соед 1ненные пересчетную схему и первый формирователь коротких импульсов подключен к первым входам первого и второго элементов И и к входу элемента задержкир выход которого соединен с единичным входом первого установочного триггера, один выход которого через второй элемент И соединен с входом счетного триггера и с первым входом третьего элемента И другой выхо первого установочного триггера через первый элемент И подключен к nepaoN входу первого элемента ИЛИ и единичному входу второго установочного триггера, единичный выход которого третьим выходом блока управления, вход генератора импульсов и управляющий вход второго элемента ИЛИ подключены к шике запуска, выход счетного триггера через второй формирователь коротких импульсов подключен к пятой выходной шине блока управления, к единичному аходу третьег установочного триггера и к нулевому входу четвертого устаковочного триггера, единичный выход которого соединен с первой выходной шиной блока управления и с первым входом третьего элемента ИЛИ, второй вход которого соединен с единичным выходом третьего установочного триггера и с четвертым выходом блока управления, выход третьего элемента ИЛИ подключен через элемент НЕ к второму входу третьего элемента И и первому входу четвертого элемента И, и через пятый элемент И - к первому входу четвертого элемента ИЛИ, второй вход которого подключен к ьыходу третьего элемента И и к второму входу первого элемента ИЛИ, выход которого соединен с нулевым входом пятого установочного триггера, единичный выход которого является вторым выходом блока управления, нулевые входы второго и третьего установочных триггеров, а также первый вход пятого и второй вход четвертого элементов И соединены с входной шиной блока управления, выход четвертого элемента ИЛИ подключен к единичному входу четвертого установочного триггера, а выход четвертого элемента через второй элемент ИЛИ соединен с единичным входом пятого установочного триггера.

Такое выполнение устройства дает возможность начинать преобразования в любой момент времени без предварительного значения скорости изменения частоты или начального значения частоты, а также производить преобразование при любых изменениях частоты как в сторону уменьшения, так и в сторону увеличения.

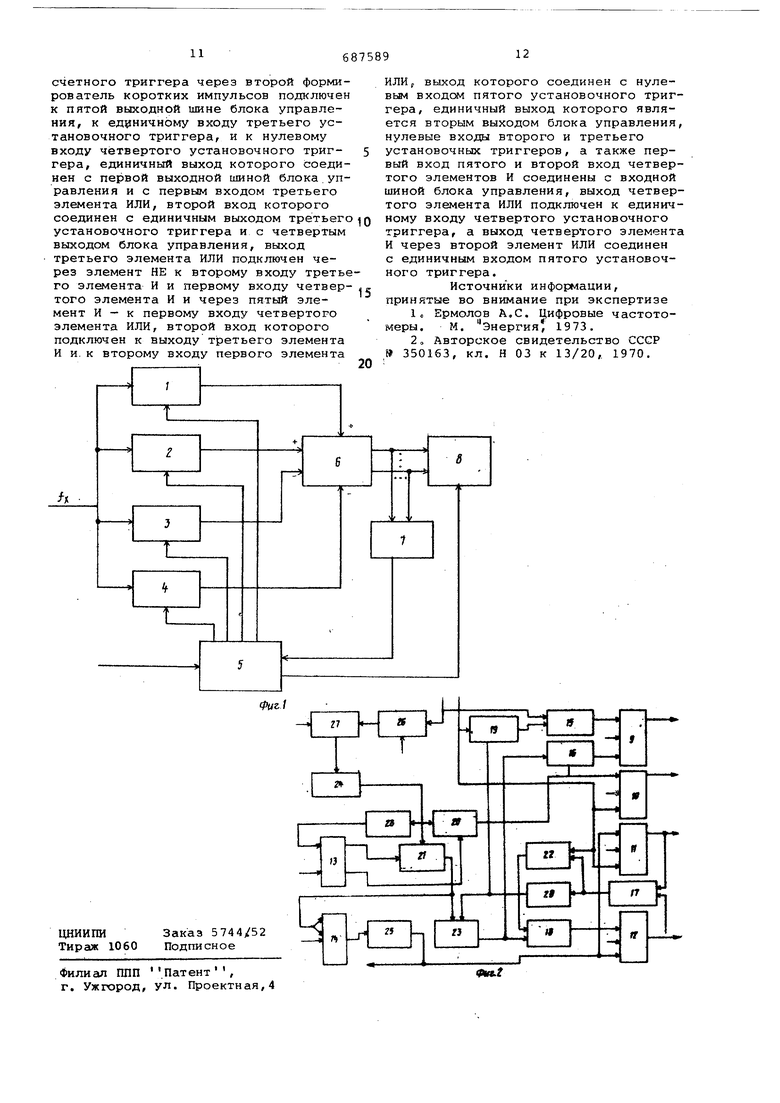

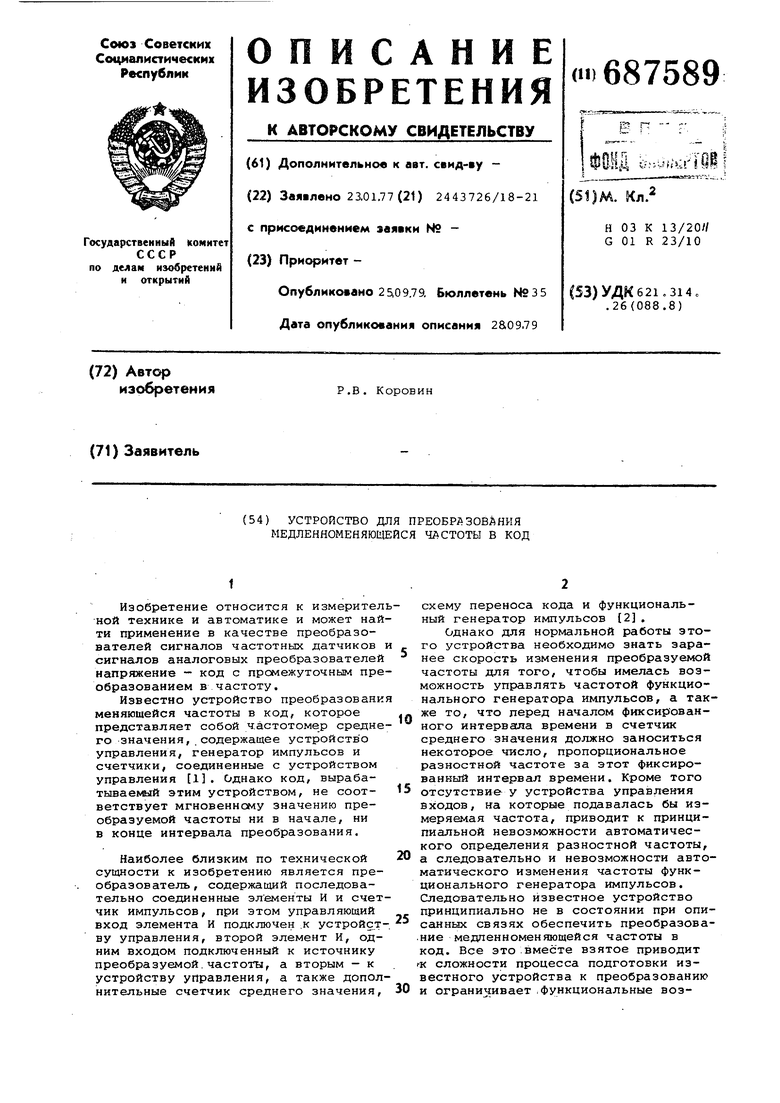

На фиг. 1 изображена функциональная схема устройства для преобразования медленноменяющейся частоты в код на фиг. 2 - функциональная схема блока управления.

Устройство для преобразования медленноменяющейся частоты в код содержит четыре элемента И 1-4, первые входы которых подключены к входной шине устройства, вторые входы элемента И подключены к четырем выходам блока управления 5, при этом выход элемента И 1 подключен к первому суммирующему входу реверсивного счетчика б, выход элемента И 2 к второму суммирующему входу реверсивного счетчика 6, выход элемента И 3 подключен к первому вычитающему входу реверсивного счетчика 6 и выход элемента И 4 подключен к второму вычитающему входу реверсивного счетчика 6. Выходы разрядов реверсивного счетчика б через дешифратор 7 нулевого состояния подключены к первому входу блока управления 5 и непосредственно к блоку 8 индикации с памятьюf управляющий вход которого присоединен к пятому выходу блока управления. Второй вход блока управления служит для подачи сигнала зацус.ка. Блок управления 5 содержит пять установочных триггеров 9-13, счетный триггер 14, четыре элемента ИЛИ 15-1 пять элементов И 19-23, два формирователя коротких импульсов 24 и 25, генератор импульсов 26, пересчетную схему 27, элемент задержки 28 и элемент НЕ 29. При этом единичный вход триггера 9 через элемент ИЛИ 15 подключен непосредственно к входу запуска и к управляющему входу запуска мого генератора импульсов 26, а чере элемент И 19, второй вход которого подключен к выходу элемента НЕ 29 и к входу элемента И 23, подключен к выходу дешифратора 7, соединенному .также с нулевыми входами триггеров 10 и 11 и с первым входом элемента И 22, второй вход которого подключен к входу элемента НЕ 29, а через элемент ИЛИ 17 связан с единичными выходами триггеров 11 и 12. Запускае мый генератор импульсов через последовательно соединенные пересчетную схему 27, формирователь коротких импульсов 24, элемент задержки 8, триггер-13, элемент И 21, триггер 14 и формирователь коротких импульсов 25 соединен с выходом блока управления 5, подключенным к блоку индикации с памятью 8, с нулевым входом триггера 12 и с единичным входом триггера 11, при этом выход формирователя коротких импульсов 24 подключен к второму входу элемента И 21, выход которого подключен также к вто рому входу элемента И 23, выход которого подключен к входам элементов ИЛИ 16 и 18, соединенных выxoдa ш соответственно с нулевым входом триг гера 9 и с единичным входом триггера 12, при этом второй вход элемента ИЛИ 18 соединен с выходом элемента И 22, Кроме того выход формирователя 24 соединен с первым входом элемента И 20, второй вход которого подключен к нулевому выходу триггера 13, а выход - к второму входу элемента ИЛИ 1 и к единичному входу триггера 10. Единичные выходы триггеров 9-12 являются соответственно вторым, третьим, четвертым и первым выходами блока управления 5, а нулевые входы всех триггеров, входы сброса счетчикового делителя частоты и генератора импульсов 26 подключены к шине установки устройства в исходное состояние. В исходном положении (после подачи на шину установки устройства в ис ходное состояние сигнала установки) реверсивный счетчик установится в ну левое состояние, так ;же как и пересчетная схема 27, в нулевое состояни становятся также триггеры 9-12, причем элементы И 1-4 оказываются закры TfjMH, и триггеры 13,и 14, причем эле мент И 21 запирается, а элемент И 20 оказывается открытым. Поскольку на первом и четвертом выходах блока 5 отсутствуют высокие потенциа.ггы, элемент И 22 закрыт, а на выходе элемента НЕ 29 существует высокое напряжение, открывающее элементы И 19 и 23. Генератор импульсов 26 сигналов не вырабатывает. В таком состоянии устройство находится до подачи запускающего сигнала на шину запуска. Запускающий сигнал . воздействует на запускаемый генератор импульсов 26, который начинает генерировать импульсные сигналы стабильного периода Тд, поступающие на пересчетную схему 27 с коэффициентом деления К. Одновременно с запуском генератора 26 сигнал с шины запуска поступает через элемент ИЛИ 15 на единичный вход триггера 9, триггер переходит в единичное состояние, при котором на управляющий вход элемента И 2 поступает высокий потенциал, открывает его, через него с входной шины на. суммирующий вход первого разряда реверсивного счетчика поступают импульсные сигналы преобразуемой частоты. В момент времени t , соответствующий интервалу 0,5 Т - , после появления импульса запуска на выходе пересчетной схемы 27 появляется первый сигнал в виде высокого потенциала, преобразуелый формирователем 24 в короткий импульс, который через открытый элемент И 20 поступает на единичный вход триггера 10 и через элемент ИЛИ 16 на нулевой вход триггера 9. В результате этого высокий потенциал на втором выходе блока управления прекращается и элемент И 2 закрывается, а триггер 10 переходит в единичное состояние, на его выходе появляется высокий потенциал, открывающий элемент И 3, в результате чего импульсы преобразуемой частоты с входа устройства подаются на вьлчнтающий вход первого разрядареверсивного счетчика 6. В результате поступления изменяющейся частоты f в течение интервала времени от момента запуска до момента t.j на суммирующий вход первого разряда реверсивного счетчика к моенту tj число импульсов, поступающих на счетчик, определяется при линейном изменении входной частоты зависимостьюNO- (f,-1-0,25 Л f) 0,5 T«f, где fo - мгновенное значение частоты в момент начала измерений (при t 0) ; Af - приращение частоты за длительность некоторого фиксированного интервала 2 Kg Т Кроме поступления сигнала с формиователя 24 на триггеры 9 и 10, он

элемент задержки 28 поступает на единичный вход триггера 13, триггер при этом переходит в единичное состояние, причем закрывается элемент И 20 и открывается элемент И 21,

Поступление импульсов входной преобразуемой последовательности на вычитающий вход первого разряда реверсивного счетчика происходит до тех пор, пока счетчик не обнулится. При этом срабатывает дешифратор нуля 7, на его выходе появляется сигнал, который поступает на нулевой вход триггера 11, подтверждая его исходное состояние, на нулевой вход триггера 10, возвращая его в исходное состояние и прекращая подачу импульсов преобразуемой последовательности на вычитающий вход первого разряда реверсивного счетчика, и через элемент И 19, открытый высоким потенциалом на выходе элемента НЕ 29, и элемента ИЛИ 15 на единичный вход триггера 9, переводя его в единичное состояние, открывая элемент И 2 и обеспечивая поступление преобразуемой последовательности вновь на суммирующий вход первого каскада реверсивного счетчика 6. Этот процесс продолжается до момента времени tj,, отстоящего от момента запуска на интервал Т, В этот момент времени t на выходе пересчетной схемы 27 появляется высокий потенциал, преобразуемый формирователем 24 в короткий импульс, который через открытый элемент И 21 поступает, во-первых, на триггер 14 и переводит его в единичное состояние, при котором на нулевом выходе, соединенном с формирователем 25 исчезает высюкий потенциал, во-вторых, на элемент И 23, который до этого был открыт высоким потенциалом с выхода элемента НЕ 29, проходит элемент И 23 и через элемент ИЛИ. 16 поступает на нулевой вход триггера 9, который перебрасывется в нулевое состояние и закрывает элемент И 2, а также с выхода элемента И 23 через элемент ИЛИ 18 поступает на единичный вход триггера 12р который вырабатывает на своем единичном выходе высокий потенциал, открывающий элемент И 1, Входная преобраз уемая последовательность через элемент И 1 после момента tj поступаетна суммирующий вход второго разряда реверсивного счётчика б.

К моменту времени tj, в счетчике присутствует положительный код N, соответствуюсдай разности

% - N. - N. ,

где N«, количество периодов преобразуемого сигнала, в интервале времени от tj во

Нетрудно подсчитать, что N. (fj +0, 2 5uf) О ,5% (fo-5-0 , 75Af) О , БТ где f,j мгновенная частота исследуемого процесса в момент , равная fy + 0,5Af .

При этом N2,N. -No.,5uf 0,,25Д Т,

Начиная с момента времени t импульсы входной преобразуемой, последовательности подаются на суммирующий вход второго разряда счетчика, что равносильно тому, что на суммирующий вход первого разряда этого счетчика подается удвоенная частрта входной чмпульсной последовательности. Этот процесс заполнения счетчика удвоенной частотой

продолжается до момента времени t, отстоящего от момента f на интервал времени 0,5 Тхр, В момент времени tjна выходе пересчетной схемы 27 появляется импульс, укорачивается формирователем 24 и через элемент И 21 поступает на счетный вход триггера 14, Напомним, что к этому моменту времени элемент И 20 закрыт низким потенциалом на нулевом выходе триггера 13, элемент И 23 закрыт отсутствием потенциала на выходе элемента НЕ 29 из-за наличия потенциала ча выходе триггера 12,

Триггер 14 меняет свое состояние, в результате чего на его нулевом выходе появляется сигнал, который укорачивается формирователем 25 и поступает на пятый выход блока управления. На нулевой вход триггера 12 и на. единичный вход триггера 11. Триггеры перебрасываются, в результате чего элемент И 1 закрывается, а элемент И 4 открывается и импульсы входной преобразуемой последовательности поступают на вычитающий вход второго разряда реверсивного счетчика.

Следовательно, к моменту времени tj в счетчике оказывается записанный код Nj .

где NJ.JI - удвоенное количество импульсов, поступившее на счетчик в интервале от tji, до tj , (,25Af) Тф 0,5(fo -И,25Л) Тф.

Здесь f - мгновенное значение измеряемой частоты в момент времени t ta, равное fo -f Af.

При этом .

N3 Nx+Ni..-3 0,254fT j,+ (fo+l,25Af) ( +1,5л) Tqj,

где fi - мгновенное значение преобразуемой частоты в момент времени t t} .

Таким образом уже в момент времени t t,, т,е, через промежуток времени в 1,5 Тф после начала преобразования код, содержащийся в счетчике 6, пропорционален с некоторым коэффициентом Тф мгновенному значению преобразуемой частоты в этот же момент времени. Содержание счетчика б в этот момент можно отразить на табло блока индикации, что и осуществляется си.гналом пятого выхода блока управления.

Начиная с момента времени Ц, производятся обычные циклы измерений, длящиеся в течение интервалов t Тф Эти интервалы ограничиваются двумя приодами сигналов с формирователя 24, поступающих через элемент И 21 на счетный вход триггера 14, вырабатыващего импульсы считывания показаний со счетчика б, В начале каждого из этих интервалов (так же как после момента tj) производится вычитание импульсов через вычитающий вход второго разряда счетчика (т.е. вычитани с удвоенной частотой) до обнуления счетчика 6. В момент обнуления счетчика на вьоходе дешифратора нуля 7 появляется сигнал, подтверждающий нулевое состояние триггера 10, переводщий триггер 19 в нулевое состояние и через элемент И 22 и элемент ИЛИ 1 переводящий триггер 12 в единичное состояние. При этом прекращается поступление входной преобразуемой последовательности на вычитающий вход второго разряда счетчика и начинается поступление этой последовательности на суммирующий вход второго же разряда. Другими словами, начиная с момента tn, суммирование и вычитание числа периодов входной последовательности производится как бы с удвоенной частотой.

Таким образом, в интервале от t до t/j tj-f Тфна счетчик поступит количество импульсов, равное (fg+0 ,5Д) Tip, что равносильно Н.ц (2fj-(-Af)T.

.При работе на вычитание компенсируется число импульсов N0 f« ф, следовательно, в момент t код счетчика будет представлять собой число Nj (fj+Д)Тф( Тф, т.е. в момент tq этот код пропорционален мгновенному значению измеряемой частоты. Содержание счетчика 6 индицируется блоком индикации 8.

Результат преобразования (код в счетчике 6 в моменты t i.-j Т) не зависит от величины и знака изменения частоты uf в данном интервале Тф. Следовательно, предлагаемое устройство без всяких изменений может служить для преобразования и индикации мгновенных значений как возрастающей, так и уменьшающейся, равно как и неизменной, частоты.

Для нормальной работы предлагаемого устройства нет необходимости знать заренее скорость изменения преобразуемой частоты в любом из интервалов Тф|, нет необходимости знать разностную частоту за фиксированный интервал времени Тф и заносить число, пропорциональное этой разностной частоте, в счетчик. В данном устройстве нет необходимости применять функцио aльный генератор импульсов, что сулественно упрощает схему устройства

и его конструкцию. Возможность работы устройства с любым изменением частоты (по величине и знаку) расширяет функциональные возможности данного устройства.

Формула изобретения

1. Устройство для преобразования медленноменяющейся частоты в код содержащее два элемента И, управляющие входы которых подключены соответственно к первому, и второму выходам блока управления, вход первого элемента И подключен к входной шине устройства и реверсивный счетчик, отличающееся тем, что, с целью упрощения процесса измерени повышения надежности и расширения диапазона изменения преобразуемых частот, в него дополнительно введен два элемента И и дешифратор, причем входы второго и двух дополнительных элементов И подключены к входной шине устройства, выходы первого и второго элементов И подключены соответственно к первому и второму;суммирующим входам реверсивного счетчика к вычитающим входам которого подключены выходы дополнительных элементов И, выходы реверсивного счетчика поразрядно соединены с входами дешифратора , выход которого подключен к входу блока управления, третий и четвертый выходы которого соединены с управляющими входами соответственно первого и второго дополнительных элементов И.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит пять установочных триггеров, счетный триггер, четыре элемента ИЛИ, пять элементов И, два формировлтеля коротких импульсов, генератор импульсов, пересчетную схему, элемент задержки и элемент НЕ, причем выход генератора импульсов через последовательно соединенные пересчетную схему и первый формирователь коротких импульсов подключен к первым входам первого и второго элементов И и к входу элемента задержки, выход которого соединение единичным входом, первого установочного триггера, один выход которого через второй элемент И соединен с входом счетного триггера и с первым входом третьего элемента И, другой выход первого установочного триггера через первый элемент И подключен к первому входу первого элемента ИЛИ И единичному входу второго установочного триггера, единичный выход которого является третьим выходом блока управления, вход генератора импульсо и управляющий вход второго элемента ИЛИ подключены к шине запуска, выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой компенсационный фазометр | 1980 |

|

SU920563A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1990 |

|

SU1837395A1 |

| Адаптивный аналого-цифровой преобразователь | 1980 |

|

SU875622A1 |

| Программируемый преобразователь код-фаза | 1984 |

|

SU1236389A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU924611A1 |

| Цифро-аналоговый преобразователь | 1977 |

|

SU690624A1 |

| Аналого-цифровой преобразователь компенсационного интегрирования | 1974 |

|

SU764126A1 |

| Цифровой автокомпенсационный фазометр | 1980 |

|

SU901937A2 |

| Устройство для телеизмерения давления скважинных штанговых насосов | 1990 |

|

SU1711218A1 |

Авторы

Даты

1979-09-25—Публикация

1977-01-23—Подача