1-2-4-8, содержащий четыре, по числу разрядов, счетных триггера, по четыре элемента И в суммарном U разностном каналах, каждый из которых соединен соответственно, нервым входом с единичиым или нулевым выходом триггера соответствующего разряда, четыре элеме1гга ИЛИ, входы иервого из которых являются входами суммарного и разиостиого каналов счетчика, входы других элементов ИЛИ иодключеиы к выходам элементов И соответствующих разрядов суммариого и разиостиого каналов, третий вход элемента ИЛИ четвертого разряда соединен с выходом элемента И четвертого разряда суммарного канала, являющийся выходом этого канала счетчика, а выходы всех элементов ИЛИ подключены к счетным входам триггеров соответствующих разрядов, элемеит ИЕ, входом соедииеиный с выходом элемеита И третьего разряда разностного канала, а выходом - со входом элемента И четвертого разряда разностного канала, выход которого является выходом разностного канала счетчика, блокирующий элемент PI, иервым входом иодключенный к нулевому выходу трнггера четвертого разряда, вторым - к шиие разрешения счета разностного канала, а выходами соединенный с блокирующими входами триггеров второго и третьего разрядов, иричем Н1ина разрешения счета разностного канала нрисоединена ко вторым входам элементов И трех первых разрядов разностного канала, шина разрешения счета суммариого каиала ирисоединеиа ко вторым входам каждого из четырех элементов И суммариого канала, нулевой выход триггера четвертого разряда подключен к третьему входу элемеита И первого разряда суммарного канала, введена схема компенсации времени переключения триггера первого разряда, входом иодключеииая к выходу элемента ИЛИ, установленного иа входе счетчика, а выходом соединеииая со входами всех элементов И каждого разряда как суммарного, так и разностного каналов, исключая выходной элемент И четвертого разряда разностного канала и блокирующий элемент И, причем единичный выход трнггера первого разряда подключен к четвертым входам элементов И второго и третьего разрядов разиостиого канала, единичный выход триггера второго разряда подключен к пятому входу элемента И третьего разряда суммарного канала, а его нулевой выход подключен к нятому входу элемента И третьего разряда разностного канала и к третьему входу блокирующего элемента И, нулевой выход триггера третьего разряда подключен к четвертому входу блокирующего элемента И.

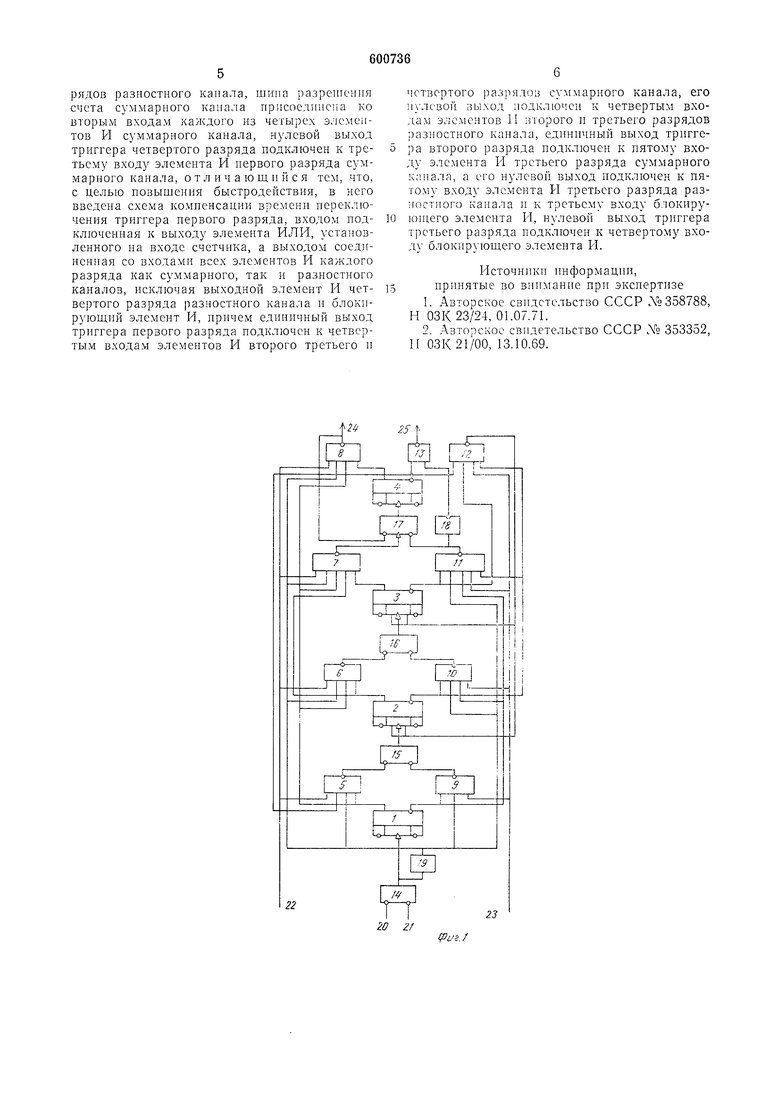

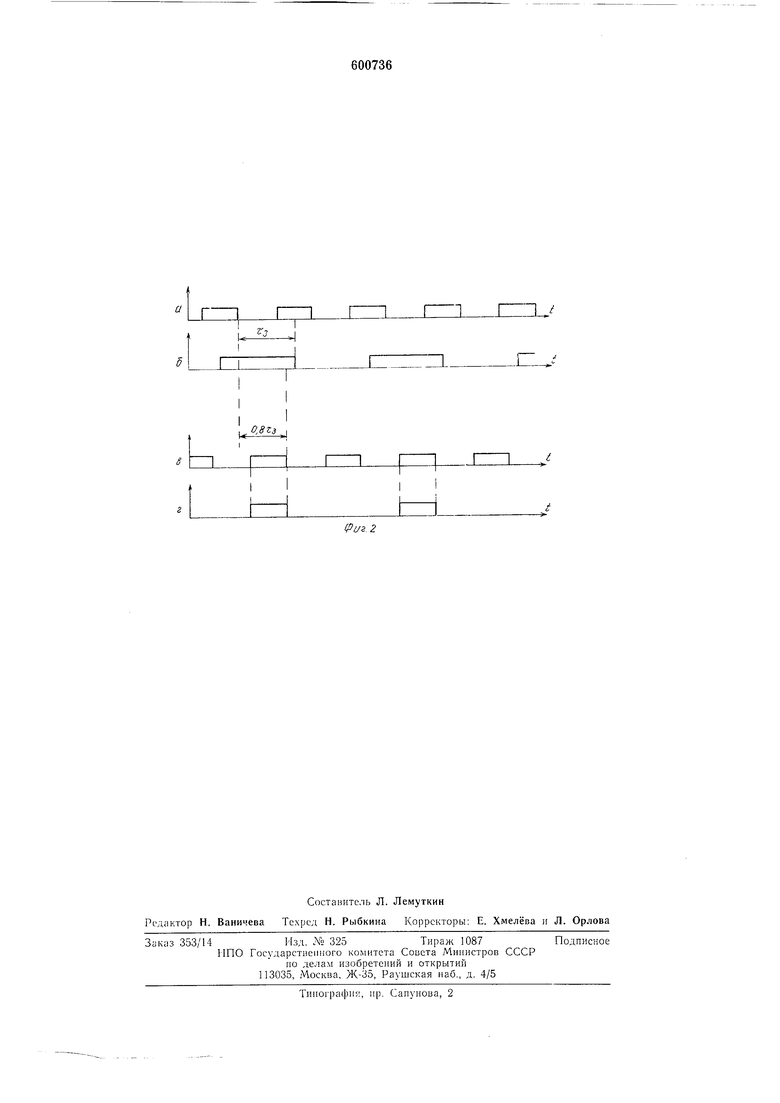

Иа фиг. 1 представлена структурная схема двоично-десятичного реверсивного счетчика; на фиг. 2 - диаграммы, ноясияющие работу данного счетчика.

Предлагаемый счетчик содержит четыре счетных триггера 1-4, четыре элемента И 5-8 суммариого канала, элементы И 9-11 разностного канала, блокирующий элемент И 12,

элемент И 13, четыре элемента ИЛИ 14-17, элемент ИЕ (ннвертор) 18 и схему 19 комненсадии времени нереключения триггера нервого разряда, представляющую соОой линию задержкн, сигнал на выходе контроля задержан относительно сигиала на шинах 20, 21 суммарного и разиостиого каналов на время, равное (0,8-0,9) времеии нереключения триггера 1. Счетчик содерл;ит также шииы 22, 23 разрешеиия счета и выходы 24, 25 суммарного и разностного каналов.

Иа вход счетчика по одиой из шии 20 или 21 ностунают тактовые нмнульеы (см. фиг. 2,а). В это время триггер 1 имеет состояиия, иредетавленные на фиг. 2,6. Переключение этих состояний происходит ио отрицательиым иерепадам входного сигнала с задержкой на время Тз - время переключения триггера 1. Элемеитом И 5 в суммариом канале или элементом И 9 в разностном канале производится оиределение совпадений входных имиульсов с имнульсами, ноступающими с выхода триггера 1. Введение схемы 19 приводит к совпадению

на элементах И 5 и 9 ил1пульсов, поступающих с выхода триггера 1, с импульсами, поступающими с выхода схемы 19, задержанными его на 0,8 Тз относительно входных сигиалов. Иа выходе других схем совпадения при этом

формируются имиульсы, иредставлениые на фиг. 2,г.

Формула изобретения

Двончно-десятичный реверсивный счетчик в

коде 1-2-4-8, содержащий четыре, по числу разрядов, счетиых триггера, по четыре элемента И в суммарном н разностном каналах, каждый из которых соединен, соответственно, иервым входом с единичным или нулевым выxoдoJM триггера соответствуюи его разряда, четыре элемента ИЛИ, входы иервого из которых являются входами суммарного и разностного каналов счетчика, входы других элементов ИЛИ подключены к выходам элементов И

соответствующих разрядов суммарного и разностного каналов, третий вход элемеита ИЛИ четвертого разряда соедииен с выходом элемента И четвертого разряда суммарного канала, являющимся выходом этого канала

счетчика, а выходы всех элементов ИЛИ подключены к счетным входам триггеров соответствующих разрядов, элемеит ИЕ, входом соедииеииый с выходом элемента и третьего разряда разностного канала, а выходом - со входом элемента И четвертого разряда разностного канала, выход которого является выходом разностного канала счетчика, блокирующий элемент И, первым входом подключенный к нулевому выходу триггера четвертого

разряда, вторым - к шине разрещения счета разностного канала, а выходом соедииенный с блокирующими входами триггеров второго и третьего разрядов, причем шина разрешения счета разностного канала присоединена ко

вторым входам элементов И трех первых разрядов разностного капала, шипа разрептенпя счета суммарпого канала нрнсоедппспа ко вторым входам каждого из четырех элемептов И суммарного капала, нулевой выход триггера четвертого разряда подключен к третьему входу элемента И первого разряда суммарного канала, отличающийся тем, что, с целью повышения быстродействия, в него введена схема компенсации времени переключения триггера первого разряда, входом подключенпая к выходу элемента ИЛИ, установленного на входе счетчика, а выходом соединенная со входами всех элементов И каждого разряда как суммарпого, так и разпостного каналов, исключая выходной элемент И четвертого разряда разностного канала п блокирующий элемент И, причем единнчпый выход триггера первого разряда подключен к четвертым входам элементов И второго третьего п

четвертого разрядов суммарного канала, его нулевой выход подключен к четвертым входам элементов И второго и третьего разрядов разностного капала, едпппчный выход трпггера второго разряда подключен к пятому входу элемента И третьего разряда суммарного , а его пулевой выход подключен к пятому входу элемента И третьего разряда раз110СТНОГО канала п к третьему входу блокируloniero элемента И, нулевой выход триггера третьего разряда подключен к четвертому входу блокирующего элемента И.

РГсточникп информации, иринятые во внимание при экспертизе

1.Авторское свидетельство СССР oYo 358788, Н ОЗК 23/24, 01.07.71.

2.Автооское свидетельство СССР Х 353352, II ОЗК 21/00, 13.10.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1978 |

|

SU731597A1 |

| Устройство для прерывания программ | 1976 |

|

SU630629A1 |

| Распределитель сигналов | 1973 |

|

SU514442A1 |

| Двоичный умножитель числа импульсов на 5 | 1976 |

|

SU660048A1 |

| Специализированная электронная машина для анализа определителей | 1969 |

|

SU481037A1 |

| Устройство для подсчета предметов | 1975 |

|

SU590789A1 |

| ДВОИЧНЫЙ СЧЕТЧИКВСЕСОЮЗНАЯflATEHTHO-TEXHtViErKAfБИБЛИОТЕКА | 1972 |

|

SU330547A1 |

| Устройство для преобразования кодов | 1974 |

|

SU556429A1 |

| Устройство для контроля ошибок канала магнитной записи-воспроизведения | 1983 |

|

SU1101887A1 |

| Трехканальное устройство для выбора достоверной информации | 1975 |

|

SU595733A1 |

23

Авторы

Даты

1978-03-30—Публикация

1976-02-03—Подача