1

Изобретение относнтся к вычислительной техннке и автоматике и может быть исиользовано при ностроении систем новышенной надежности.

Известен резервированный делитель частоты, содержащий три канала деления, каждый из которых состоит из мажоритарного элемента и триггера, выходы тр 1ггеров каналов деления подключены нараллельпо мажоритарным элементам 1.

Недостатком известного резервированного делителя частоты является то, что он предназначен для исправления только одиночных сбоев триггера при работоспособности всех элементов и не обеснечивает поканальпого исправления ошибок при любом одиночиом отказе.

Известеи также резервированный делитель частоты, содержащий три канала, в каждом из которых включен / 5-триггер, один выход которого соединен с входной шиной, мажоритарный элемент, один вход которого подключен к выходу триггера и одному из входов мажоритарных элементов остальных каналов, и выходной логический элемент ИЛИ-НЕ, один выход которого соединен с шиной стробирующего сигнала, а выход - с / -входом Л5-триггера данного канала, лричем выход мажоритарного элемента каждого капала соединен с соответствуюп1,ей выходной шиной 2.

Недостатком данного устройства является то, что нельзя обнарулсить неисирав5 ность при выходе из строя делителя частоты в одном из каналов, так как нет возможности принудительной установки делнтеля частоты в пулевое или единичное состояние.

10 Цель изобретения - повышение надежности устройства путем обнаружения неисправности по принудительной установке делителя в нулевое нлп едпппчное состояние.

15 Поставленная цель достигается тем, что в резервированный делитель частоты, содержащий три канала, в каждом из которых включен / 5-триггер, вход которого соединен с входной шиной, мажоритарный элемент, один вход которого подключен к выходу трпггера и одному из входов мажоритарных элементов остальных каналов, и выходной логический элемеит ИЛИ- НЕ, один вход которого соединен с шиной

25 стробирующего сигнала, а выход - с Rвходом ./ 5-триггера данного канала, нричем выход мажоритарного элемента каждого канала соедннен с соответствующей выходной шиной, введены два дополнительны.

логических э.чсмеыта ИЛИ- -НЕ, один из входов исрзого элемента Ио1И---НЕ соединен с выходом мажор)1тарного элемента данного канала, а второй вход - с шнной сигнал установки в единичное состояние, выход-с одним входом второго донолиительного логического элемента ИЛИ-ИЕ, второй вход которого соединен с шиной стробирующего сигнала, третий вход нодключен к шине установки в нулевое состояние, а выход соединен с вторым входом выходного логического элемента ИЛИ-ИЕ и 5-входом / 5-триггера даиного канала.

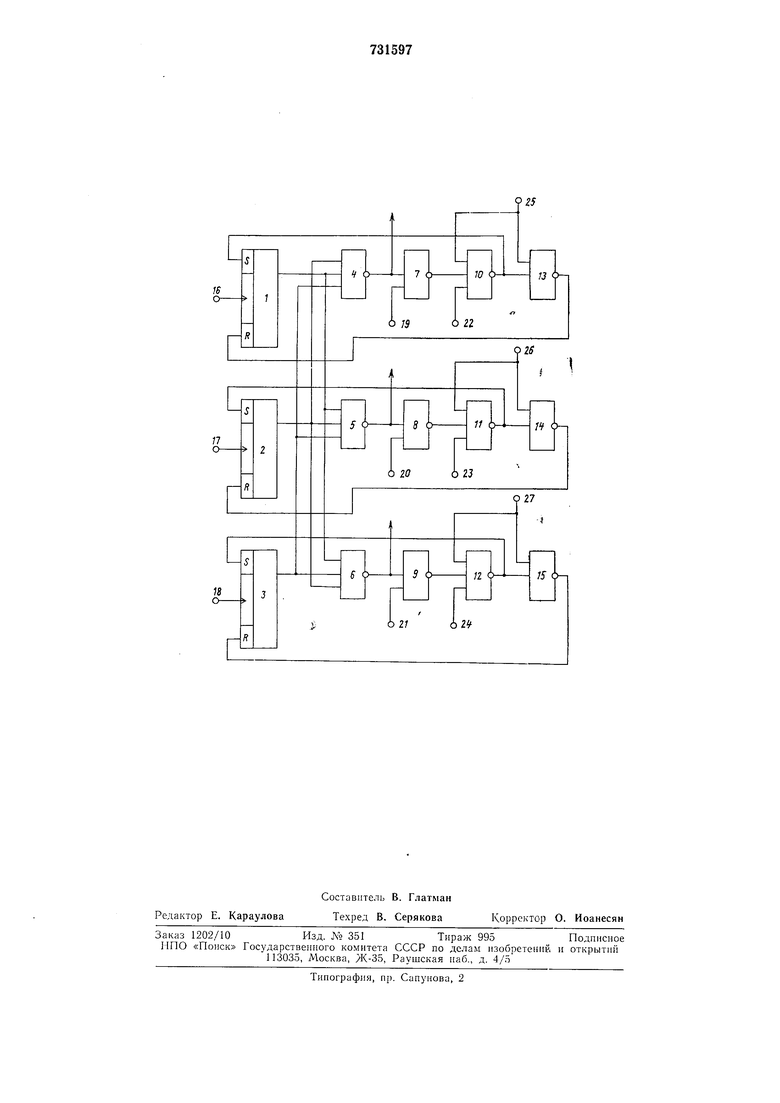

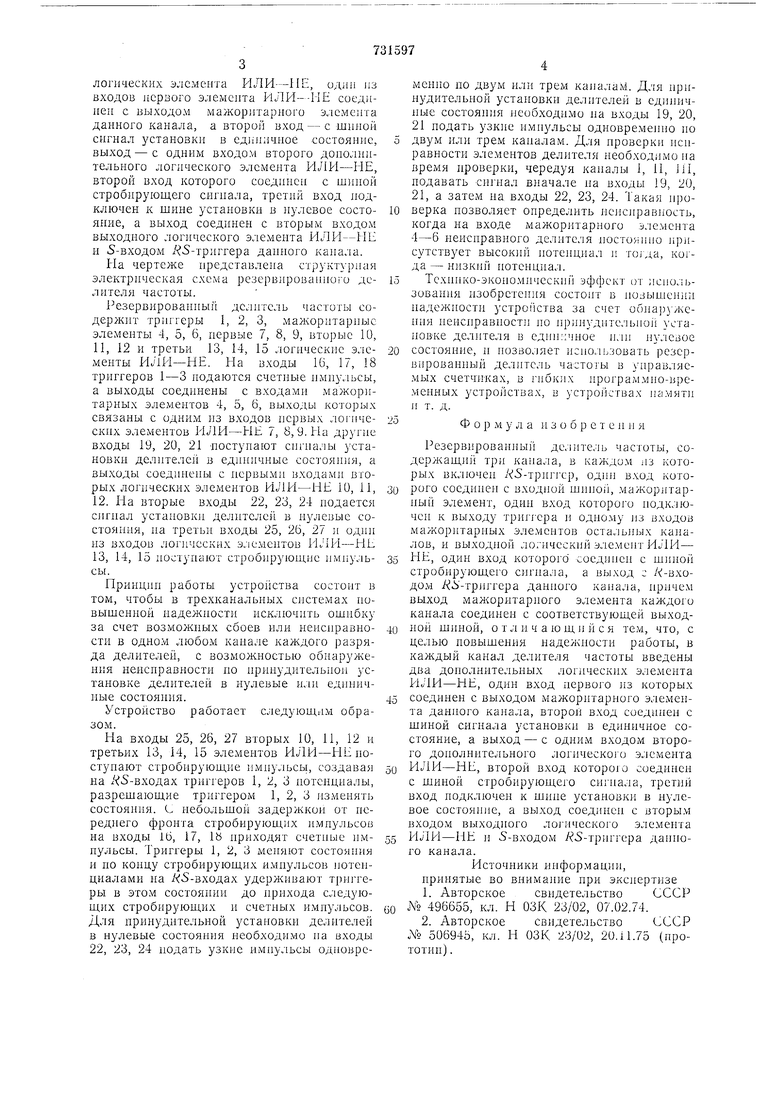

Иа чертеже иредставлеиа структу1)11ая электрическая схема резервированиого делителя частоты.

Резервироваииый делитель частоты содержит триггеры 1, 2, 3, мажоритарные элементы 4, 5, 6, первые 7, 8, 9, вторые 10,

11,12 и третьи 13, 14, 15 логические элементы ИЛИ-ИЕ. Иа входы Ш, 17, 18 трнггеров 1-3 иодаются счетные имиульсы, а выходы соединены с входамн мажоритарных элементов 4, 5, 6, выходы которых связаны с одним из входов первых логических элементов ИЛИ-НЕ 7, 8, 9. Иа другие входы 19, 20, 21 лостуиают сигиалы установки делителей в едииичиые состояиия, а выходы соедииеиы с иервыми входа1ми вторых логических элементов ИЛИ-ИЕ 10, И,

12,Иа вторые входы 22, 23, 24 нодается сигнал установки делителей в нулевые состояния, на третьи входы 25, 26, 27 и один из входов логических элементов ИоЧИ-Е1Е

13,14, 15 иостуиают стробирующие имиульсы.

Ирпиции работы ycTpoiicTBa состоит в том, чтобы в трехканальных системах повышенной надежности исключить ошибку за счет возможных сбоев или ненсиравности в одном любом канале каждого разряда делителей, с возможностью обнаружения неисправности но нрнпудительнои установке делителей в нулевые или единичные состояния.

Устройство работает следующим образом.

Иа входы 25, 26, 27 вторых 10, 11, 12 и третьих 13, 14, 15 элементов ИЛИ-ИЕ иостуиают стробируюш.ие имиульеы, создавая на хч б-входах триггеров 1, 2, 3 нотенцналы, разрешаюидие триггером 1, 2, 3 измеиять еостояния. С небольшой задержкой от переднего фронта стробирующих имиульсов на входы Ш, 17, 1й ириходят счетиые имиульсы. Триггеры 1, 2, 3 меияют состояиия и по концу стробируюгцнх имиульсов потепцпалами на / 5-входах удерживают триггеры в этом еостояиии до прихода следуюш,их стробпруюш,их н ечетных импульсов. Для иринудительной устаиовки делителей в нулевые состояния необходимо иа входы 22, 23, 24 подать узкие импульсы одиовременно по двум пли трем каналам. Для иринудительиой устаиовки делителей в едипичпые состояния необходимо па входы 19, 20, 21 подать узкие имиульсы одиовреме И10 ио

двум или трем каиалам. Для ироверки исиравпости элементов делителя необходимого время проверки, чередуя каиалы I, И, ill, подавать сишал вначале на входы 19, 20, 21, а затем па входы 22, 23, 24. Такая нроверка нозволяет оиределить неисирав 1ость, когда на входе мажоритарного элемеита 4-6 неиснравного делителя постоя иио присутствует высокий иотеидиал и TOJVJ,a, когда - низкий потенциал.

Техиико-экоио.1ическнй эффект от исиользования изобретения состоит в иовышении надежности устройства за счет обпа1)ужеиия иеисправпости по ирии Дительио стаповке делггеля в едип::чиое или нулевое

состоянне, и иозволяет исиользовать резервированный делитель частоты в управляе.1ых счетчиках, в гибких ирограммио-иременных устройствах, в устройствах иамяти и т. д.

Фор м у л а изобретен и я

Резервированный делитель частоты, содержащий три каиала, в каждо.м ii3 которых включеи ixjS-триггер, один вход когорого еоедииеи е входной шнной, мажоритарный элемент, один вход которого нодключен к выходу триггера и одному из входов мажоритарных элементов остальных каналов, и выход 1ой логическпй элемеит ИЛИ-

ИЕ, один вход которого еоедииеи с шиной стробирующего сигиала, а выход с / -входом Ь-триггера даииого каиала, иричем выход мажоритарпого элемента каждого капала еоедппен е соответствующей выходной шииой, о т л и ч а ю щ и и с я тем, что, с целью повышения надежности работы, в каждый канал делителя чаетоты введены два дополпптельпых логичееких элемента ИЛИ-ИЕ, один вход первого из которых

еоединеп е выходом мажорптарного элемента данного канала, второй вход соединен е шииой еигнала установкн в единичное состояние, а выход - с одним входом второго доиолнптельпого логпческо1о элемепта

ИЛИ-ИЕ, второй вход которого соедппеп с шнной етробирующего сигиала, третий вход подключен к шнне установки в нулевое состояиие, а выход соединен с вторым входом выходного логического элемента

ИЛИ-ИЕ и 5-входом / 5-триггера даииого канала.

Источники ниформации, ирпнятые во внимание нри экспертизе

1.Авторское свидетельство СССР Яо 496655, кл. И ОЗК 23/02, 07.02.74.

2.Авторское свидетельство СССР JNo 506945, кл. И ОЗК 23/02, 20.11.75 (прототип) .

гг

IB

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Резервированный делитель частоты импульсов | 1977 |

|

SU698130A2 |

| Резервированный делитель частоты | 1985 |

|

SU1265995A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU953744A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU961155A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

| Резервированный делитель частоты | 1976 |

|

SU601828A1 |

| Резервированный делитель частоты | 1983 |

|

SU1163473A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Резервированный делитель частоты следования импульсов | 1980 |

|

SU936434A1 |

6

If

s (

23

20

027

3 (

n С

i2

i2/

Авторы

Даты

1980-04-30—Публикация

1978-02-09—Подача