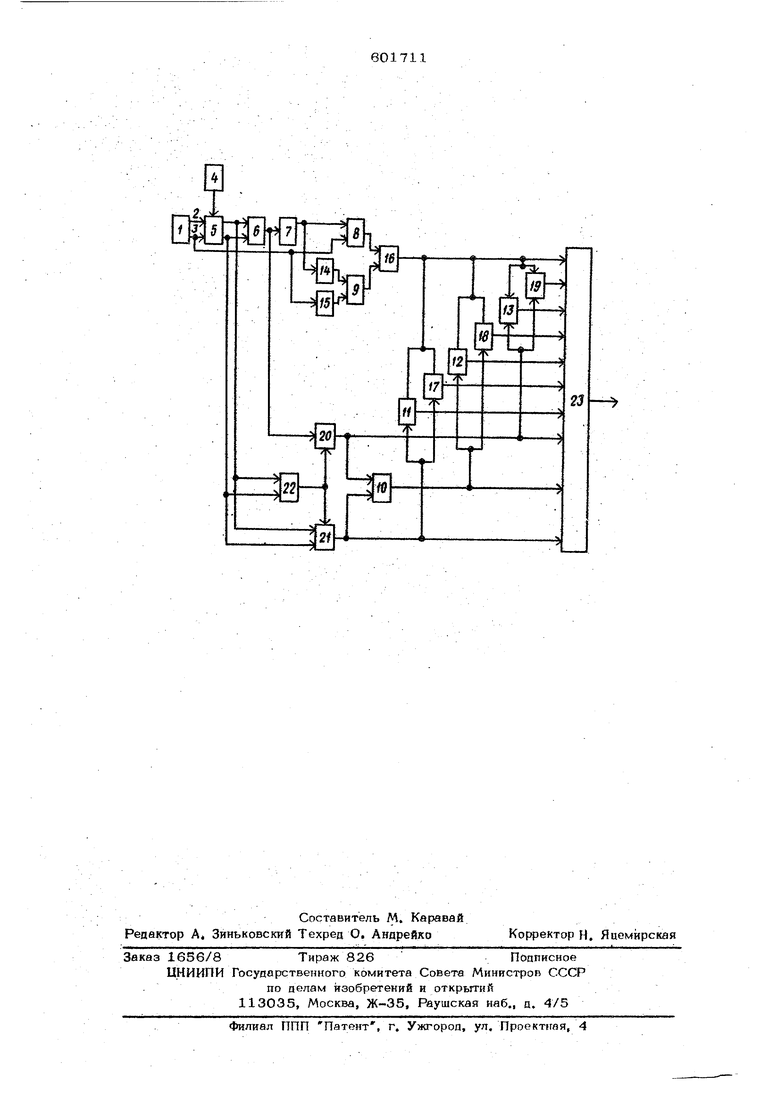

сов соединен со вторыми входами блока ко дирЬвания и блока декоаиров ания; второй Esbixbfl блока декодирования подключен через датчик случайных последовательностей и бло моделирования группового сообщения к второму вхопу блока восстановления сробшений 2. Данное устройство позволяет моделировать процессьь характерные для адресных методов передачи сжатых сообщений по каналам с помехами, в том числе для исслерования помехоустойчивости передачи существенньяс отсчетов с различным соотношением статястинеской избыточности, для оценки эф евтавндстй использования помехоустойчивых иэйов ярн адресной передаче сжатых сообщевий и т.д. Однако и это устройство не позволяет решать занапй, связанные с исследованием повьшенш внфсфмативности оценки дискретвых каналЕоО. Наиболее близким техническим {тошением к данному изобретению является устройство для моделирования систем контроля дискрет ных каналов содерн ащее блок щзеобразования случайных ойг налов, подсоединенный к выходам датчика исхойных сообщений и датчика случайных сирналов4 и анализатор .{ЗД Состав, aimaparypw указанного устройств обеспечивает исслейовааие качества фунвДионирования систем передачи данных, имеклди прямой и обратный каналы сйязи, регистрац и анализ ошибок в каналах передачи информации. Однако э устройство не позволяет исследовать процессы & устройствах, предназначенных для контроля дискретных каналов, отличительной особенностью которых является то, что в их состав входят элемен ты для формирования сигналов стирания, блоков автоматической регулировки порога, и необходимость- фиксации событий, связанных с одновременнь1М появлением ошибок и сигналов стирания различных типов, не решает задачи узкого класса. Целью изобретения является расширение класса решаемых задач. Для этого Б устройство введены два фор мирователя сигналов стирания, блок регулировки порога, блок сравнения, шесть элеме той равнозначности, пороговый элемент, че тьфё элемента ИЛИ и два инвертора, при этом единич1 ьтй и нулевой выходы датчика исходных сообщений подсоединены к управляющим входам блока преобразования случайных сигИалоЁ, информапионный вход которого подключен к датчику случайных сигналов, а БЬГХОДЬТ - к информационным входам второго формирователя сигналов стирания, к входам блока сравнения и к входам лока регулировки порога, вь1ход которого подсоединен к управляющим входам формирователей сигналов стирания, выходы которых подсоединены к входам анализатора непосредственно и через первый элемент равнозначности, вьжод блока сравнения попкйючен к первому формирователю сигналов стирания и к входу порогового элемента, выход которого через второй элемент равнозначности и первый элемент ИЛИ подключен к входу анализатора, а через первый иквер)- тор и третий элемент равнозначности подсоединен на второй вход первого элемента ИЛИ нулевой выход датчика исходных сообщений подключен к второму входу второго элемента равнозначности, а через второй инвертор к второму входу третьего элемента равнозначности, выходы формирователей сигналов стирания и первого, элемента равнозначности каждый через элемент ИЛИ и через элемент равнозначности, на другие управляющие входы которых подключен выход первого элемента ИЛИ, подключены к входам анализатора. На черетже приведена структурная электрическая схема устройства. Устройство для моделирования систем контроля дискретных кааалов содержит датчик исходньтх сообщений 1, единичный 2 и нулевой 3 Выходы датчика исходных сообщений, датчик случайньпс сигналов 4, блок для перобразования случайных сигналов 5, блок сравнения 6, пороговый элемент 7, элементы равнозначности 8 - 13, инверторь1 14 и 13, элементы ИЛИ - 19, формирователи сигналов стирания 20 и21, блок 22 для регулировки порога и анализатор 23. Устройство работает следующим образом. При включении устройства (цепь включения не показана) датчик исходньтх сообщений 1 случайным образом формирует на своих вьтходах 2 и 3 сигналы, (формируется последовательность 1 и О). Если появится сигнал на выходе 2 (моделируемая единица), то он поступйет на управляющий вход блока для преобразования случайных сигналов 5, на информационный вход которого подается сигнал с выхода датчика случайных сигналов 4. В противном случае, т.е. при выработке датчиком исходных сообшений 1 сигнала О сигнал с выхода 3 датчика 1 поступает на другой управляющий вход блока для преобразования случайных сигналов 5, на вход элемента равнозначности 12 и на вход инвертора 14, Если например, появился сигнал на вы- ходе 2, то по этому сигналу блок 5 на .опиом. выходе формирует случайный сигнал, имеющий, например, нормальный зякон распределения с параметрами. О н Ь а на другом выходе формирует сигнал, имеющий, например, нормальный закон распределения с нулевьгм средним ( С{ о). (Моделируются сигналы на выходах, например, интеграторов корреляционного приемника Дискретных сигналов). Случайные сигналы с выходов блока 5 поступают на соответствукщие входы блока 22, формирователя сигналов сткрания 21 и на входы блока. сравнения 6, Сигнал на вькоце блока сравнения 6, соответствующий разности слз айнь1Х сигналов на выходах блока 5, поступае на вход порогового элемента 7 и на вход формирователя сигналов стирания 20, Если величине этого сигнала больше величины порога срабатывания порогового элемента t, то на его вькоде появляется сигнал, который поступает на вход инвертора 14 к на вход элемента равнозначности 8. Таким образом, на выходе элемента равнозначности 8 будет сигнал только в том случае, если имеется сигнал на выходе 3 датчика исходных сообщений 1 и разность между сигналами на вь ходах блока 5 больше некоторой величины (порога срабатывания порогового элемента). Это соответствует когда, например, при передаче по дискретному каналу О получили 1, т.е моделируются случаи трансформации вида .. На вькоде элемента равнозначности 9 сигнал появляется только в том случае, если сигнал на выходе 3 датчика исходных сообщений 1 отсутствует (т.е; имеется сигнал на выходе 2) и разность между сигналами на выходах блока 5 меньше или равна порогу срабатьюания порогового элемента 7, Это соответствует случаю, когда, например, при передаче по дискретному каналу I лолучили О, т.е. моделируются случаи трансформации вида . Сигналы с выходов элементов равнозначностк 8 и 9 через элемент ИЛИ 16 поступают на вход анализатора 23, например, в один из его счетчиков (счетчик ошибок) и на входы элементов 11, 12, 13, 17, 18, 19; Таким образом, на выходе элемента ИЛИ 16 сигнал появляется при выполнении следующих условий t (rfa tj b «4ir.) а - логическая переменная, истинная при появлении сигнала 1 на -выходе 2{. . - сигналы на двух выходах блока 5 7у - знак логического умножения V - знак логического сложения,и- величигта порога. Если величины случайных сигналов, подаваемых с выходов блока 5 на ииформаци.онные входы блока 21, одновременно больше или меньше порогового сигнала, подаваемого с выхода блока 22 на управляющий вход формирователя сигналов стирания 21} т.е. если выполняется, например, условие (,и,)л(,и,)А(.,) где U - величина порога, то на выходе формирователя 21 появляется сигнал, который поступает на вход элемента, равнозначтости 10, на вход анализатора 23, например, в его счетчик сигналов стирания, подсчитывающий число событий, соответствующих выполнению условия (2), и на входы элементов 11 и 17. На вьгходе формирователя сигналов стирания 20 сигнал появляется в том случае, если вьшолняется, например, условие ,Ci где 112 - величина порога. Сигналы с вь1хода формирователя 20 поступают на элемент равнозначности 10, на вход анализатора 23, например, в один из его счетчиков, подсчитывающий число событий, Соответствующих выполнению условия (3), и на вход элементов 13 и 19. На вь1ходе элемента равнозначности 10 сигнал появляется в том случае, когда имеются одновременно сигналы на выходах формирователей 2О и 21, т.е. когда ььь полняется условие 1Мг4а/ и,л{(и,)л(и,)у () v(u)A(u), де , , UA , (J2 - имеют прежний мысл. -. , Сигнал с выхода элемента равнозначноси 10 поступает в анализатор, например р одий из его счетчиков, подсчитывакнцих исло событий.выполнения условия (4), и а Входы элементов 12 и 18. На выходе лемента равнозначности 11 появляются игналы в тех случаях, когда одновременно меются сигналы ка выходах элементов 16 и 21, т.е. моделируются события, соотетствующие одновременному вьшолнению словия (.2) и появлению ошибки. На выходе элемента равнозначности 12 оявляются сигналы в тех случаях, когда дновременно имеются сигналы на вь1ходах лементов 16 и 10, т.е. моделируются обьттия, соответствующие одновременному оявлению ошибки и вьшолненпю условия (4). На выходе элемента равнозначности 3 появляются сигналы в тех случаях, когда опновременно имеются сигналы на выходах элементов 16 и 2О, т.е. моделируются событие, соответствукйцие одновременно му появлению ошибки и вьшблнешю усло-i ВИЯ 3). На выходах элементов ИЛИ 17 - 19 по являкггся сигналы в тех случаях, волн хота бы на одном из входов появляетсяСигнал, т.е. моделируются события, заключаюшнеся в появлении или ошйбкя, вли соответствую щего сигнала стирания, иди их одновремен кое появление . С выхода логических элементов 11,, 12, 13, 17, 18, 19 .сигналы поступают на соответствующие входы анализатора (на«. , в соответствующие счетйки аналнаатора). Анализатор 23 производит обработку результатов моделирования, .например содер жимого счетчиков, полученных за определенный отрезок времени моделирования (например, -за время анализа разрядов ни формации случайной последовательности с выхода ясходньрс сообщений 1), Применение данного устройства позволяет исследовать качество работы систем контроля дискретных каналов 1фй различных принципах их построения, исследовать работ этих систем при различных параметрах |гстройств и производить сравнительный анализ эффективнрстй работы этйх устро1ст с целью- повышения э ектявности функиио нирования системы цередача аанньзх в целом, когда классически© методы прикладно математики5 являются на всегда пригодным для решения этих задач а крактическое макетированре всех условий работьз без предварительного моделирования чрезвь чайно дорогим. Исследования, проведенные на данномустройстве, покапли его высокую точность (сравнение производилось с известными данными, полученными а юлит1йческими расчетами) и дает возможность решения ряда задач исследовательского характера, когда классические методы исследований йвляют ся, в основном, не эффективными, или же требуют большого труда высококвалифицированных, математиков, программистов, и огромного машинногс времени, Формула изобретения Устройство для, моделирования систем контроля дискретных каналов, содержащее блок преобразования случайных сигналов, поасоепиненный к выходам датчика исходных сообщений и датчика случайных сигналов и анализатор, отличающееся тем, что, с целью расширения класса решаемых задач, оно содержитдва формирователя сигналов стирания, блок.регулировки порога, блок сравнения, элементов равнозначности, пороговый элемент, четыре элемента ИЛИ и два инвертора, при этом единичный и нулевой выходы датчика .исходных сообщений подсоединены к управляющим входам блока преобразования случайных сигналов, информационный вход Которого подключен к датчику случайных сигналов, а выходы - к информационным входам второго формирователя сигналов стирания, к входам блока сравнения и к входам блока pefyлиpoвки порога, выходкоторого подсоединен к управляющим входам формирователей сигналов стирания, выходы которых подсоединены к входам анализатора непосредственно и через первый элемент равнозначности, выход блока сравнения подключен к первому формирователю Сигналов стирания и к входу порогового элемента. Выход которого через второй элемент равноаначностн к первый элемент ИЛИ подключен к входу анализатора, а через нервый инвертор и третий элемент равнозначности подсоединен на Ьторой вход первого элемента ИЛИ, нулевой вькод датчика исходных сообщений подключен к второму входу второго элемента равнозначности, а через второй инвертор к второму входу третьего элемента равнозначности, В|,1ходы формирователей сигналов стирания и первого элем-ента равнозначности-, каждый через ИЛИ и через элемент равноаначнос-г тк, Ца другие управляющие входы которых подкйаден выход первого Э1темента ИЛИе подключены к входам анализатора. Источники информации, принятые во внимание при экспертизе: .1, Авторск-ое свидетельство СССР №369582, кл. Q 06 ( 7/48, 1973, 2,Авторское свидетельство СССР NS 411470, кл. Щ06 Q 7/48, 1974, 3,Шсйльев В. И. Построение систем г автоматическим копированием и исследова- нием их помехоустойчивости, Новосибирск, 1971, с. 176, рис, 63.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем контроля дискретных каналов | 1976 |

|

SU684563A2 |

| Устройство для моделирования каналов передачи дискретной информации | 1976 |

|

SU605218A1 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1987 |

|

SU1559415A1 |

| АДАПТИВНОЕ ПРИЕМНОЕ УСТРОЙСТВО | 1980 |

|

SU1840134A1 |

| Устройство для моделирования дискретных каналов | 1976 |

|

SU605220A1 |

| Устройство для моделирования каналов передачи дискретной информации | 1982 |

|

SU1049915A1 |

| Устройство для моделирования отраженных радиолокационных сигналов | 1980 |

|

SU935968A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для моделирования процесса выполнения системы работ | 1986 |

|

SU1363233A1 |

Авторы

Даты

1978-04-05—Публикация

1976-01-04—Подача