Изобретение относится к электросвязи и может быть использовано в приемных устройствах синхронизации кодовых комбинаций двоичных сообщений, закодированных каким-либо равномерным кодом с обнаружением или исправлением ошибок, к числу которых можно отнести, например, блочные и систематические коды, а также коды с проверкой на четность или нечетность.

Блочные коды отличаются тем, что с каждой последовательностью из определенного числа элементарных сообщений (двоичных символов) составляется блок из n символов (n-символьная кодовая комбинация). При этом, если выбрано некоторое число n, то можно построить общее количество Nобщ=2n различных комбинаций из n символов, из которых No<Nобщ являются разрешенными кодовыми комбинациями. Остальные Nобщ - No комбинаций являются запрещенными и не используются для передачи сообщений [1, с 84].

Систематический (n, k) код представляет собой набор n-разрядных (n-символьных) кодовых комбинаций, в которых к разрядов (двоичных символов) представляют собой результат примитивного кодирования сообщения, которые называются информационными разрядами (символами). Остальные n - k разрядов (символов) называются проверочными (корректирующими) и служат для обнаружения или исправления ошибок [1, с 100].

Код с проверкой на четность образуется добавлением к группе информационных символов (кодовой комбинации), представляющих простой (не избыточный) код одного избыточного (контрольного) символа.

При формировании кодовой комбинации в качестве контрольного символа записывается 0 или 1 таким образом, чтобы сумма «единиц» в комбинации, включая избыточный символ, была четной (при контроле на четность) или нечетной (при контроле на нечетность). Если при передаче информации приемное устройство обнаруживает, что в принятой кодовой комбинации значение контрольного символа не соответствует, например, четной суммы «единиц», то это воспринимается как признак ошибки.

Известно устройство синхронизации кодовых комбинаций, содержащее неуправляемый генератор, делитель частоты импульсов, распределитель и фазовый дискриминатор с управляющими цепями, выходы тактового и циклового фазовых дискриминаторов объединены в общих цепях управления, а выходы цепей управления подключены к дополнительным входам фазовых дискриминаторов посредством прерывистой обратной связи [2].

Недостатками такого устройства являются дополнительные требования, предъявляемые к передаваемой двоичной последовательности для обеспечения функционирования этого устройства:

1. Для обеспечения синхронизации все передаваемые кодовые комбинации должны иметь вначале и в конце паузы одинаковой длины, превышающие по длительности максимальные паузы внутри комбинации.

2. Для исключения ложных устойчивых состояний устройства должны быть исключены кодовые комбинации, симметричные относительно своей середины.

Выполнение указанных требований приводит к необходимости преобразования исходной передаваемой информации и уменьшению пропускной способности канала связи [1].

Известно множество приемных устройств синхронизации кодовых комбинаций, которые также называют устройствами цикловой синхронизации [3], предназначенных для работы с сигналами, содержащими явно выраженную синхронизирующую информацию. Для функционирования таких устройств в исходную передаваемую двоичную последовательность, в том числе и закодированную каким либо равномерным корректирующим кодом, вводят цикловой синхросигнал выбранного вида. Цикловой синхросигнал может представлять собой либо периодически повторяемый через цикловой интервал Тц (или N двоичных символов) односимвольный синхросигнал (m=1), либо периодически повторяемую через Тц=N (двоичных символов) сосредоточенную или распределенную по циклу синхрогруппу из m>1 синхросимволов. При поиске в принимаемой двоичной последовательности временного положения циклового синхросигнала или временной позиции синхронизма, соответствующей границам n-символьных кодовых комбинаций (1-ой или n-ой позиции кодовой комбинации), в качестве первичного источника синхроинформации, подлежащей обработке тем или иным устройством синхронизации кодовых комбинаций, используют отклики опознавателя синхросигнала

(дешифратора синхрогруппы) [3]. Анализируя отклики опознавателя синхросигнала от каждой временной позиций цикла длительностью Тц=N=m+Ln (в числе двоичных символов), где L - количество кодовых комбинаций в одном цикле, n - количество двоичных символов в кодовой комбинации, определяют временное положение позиции синхронизма, соответствующей временному положению границ кодовых комбинаций (1-ой или n-ой позиции кодовой комбинации) при L=1 или границ блоков из L>1 кодовых комбинаций в соответствии с длительностью выбранного Тц=N (в числе двоичных символов).

Из известных устройств синхронизации кодовых комбинаций наиболее близким по сущности решаемых задач и большинству совпадающих существенных признаков, является устройство синхронизации кодовых комбинаций, которое содержит опознаватель синхросигнала, элемент запрета, первый элемент «И», сумматор, блок регистров сдвига, решающий узел, элемент «ИЛИ», формирователь цикловых импульсов, счетчик циклов, счетчик искаженных синхросигналов, счетчик по выходу из синхронизма, первый и второй блоки выбора порога и блок выбора допустимого числа неискаженных синхросимволов, выход которого подключен к дополнительному входу опознавателя синхросигнала, на тактовый и информационный входы которого, являющиеся тактовым и информационным входами устройства, поступают соответственно последовательность тактовых импульсов и двоичная последовательность n-символьных кодовых комбинаций, содержащая n-символьный цикловой синхросигнал, представляющий собой синхрогруппу из n синхросимволов, повторяемую через каждые L n-символьных кодовых комбинаций, выход опознавателя синхросигнала, совместно подключен к первым входам элемента запрета и первого элемента «И», а также к первому входу сумматора, выход которого подключен к сигнальному входу блока регистров сдвига, основной и дополнительный выходы которого подключены соответственно к второму входу сумматора и сигнальному входу решающего узла, тактовый вход которого объединен с соответствующими входами опознавателя синхросигнала, блока регистров сдвига и формирователя цикловых импульсов, выход которого, являющийся выходом устройства, объединен с входом счетчика циклов и вторыми входами элемента запрета и первого элемента «И», выход которого через первый вход элемента «ИЛИ» подключен к входу сброса счетчика по выходу из синхронизма, другой вход которого объединен с выходом элемента запрета и входом счетчика искаженных синхросигналов, а вход сброса формирователя цикловых импульсов объединен с вторым входом элемента «ИЛИ», с входами сброса блока регистров сдвига и блока памяти решающего узла, управляющий вход которого подключен к выходу первого блока выбора порога, адресный вход которого объединен с выходом счетчика искаженных синхросигналов и адресными входами блока выбора допустимого числа неискаженных синхросимволов и второго блока выбора порога, выход которого подключен к управляющему входу счетчика по выходу из синхронизма, выход которого подключен к дополнительному управляющему входу решающего узла, который состоит из первого блока сравнения, блока памяти, блока вычитания, второго блока сравнения, счетчика сравнения и второго элемента «И», выход является выходом решающего узла, дополнительным управляющим входом которого является другой вход второго элемента «И». [4].

Однако данное устройство синхронизации кодовых комбинаций имеет следующие недостатки:

1. Данное устройство требует введения в передаваемую информационную двоичную последовательность n-символьных кодовых комбинаций циклового синхросигнала (периодически повторяемой через L n-символьных кодовых комбинаций n-символьной синхрогруппы) для определения границ кодовых комбинаций на приемной стороне. Соответственно требуется повышать скорость передачи из-за введения избыточных синхросимволов в исходную информационную последовательность кодовых комбинаций для сохранения пропускной способности канала связи и дорабатывать передающее оборудование. Кроме того, повышение скорости передачи приводит к уменьшению длительности двоичных символов и снижению помехоустойчивости приема информации [1].

2. В устройстве в качестве источника синхроинформации, выделяемой из принимаемого двоичного сигнала, используются отклики опознавателя синхросигнала на синхрогруппы из n синхросимволов. При этом допускается искажение n - K синхросимволов, где K - число не искаженных синхросимволов, и их корректировка путем инвертирования или формирования отклика опознавателя синхросигнала только на К не искаженных синхросимволов для получения большего количества откликов опознавателя синхросигнала на позиции синхронизма. Однако, при этом возрастает вероятность ложного обнаружения синхронизма, поскольку коррекции подвергаются и ложные синхросимволы. Причем, чем меньше количество синхросимволов m в синхрогруппе, тем меньше вероятность уменьшения времени восстановления синхронизма по отношению к устройству без коррекции синхрогрупп. Например, при m<3 данный метод коррекции не имеет смысла. Поэтому количество синхросимволов в синхрогруппе выбирают достаточно большим, например, при моделировании работы данного устройства использовалась 9-символьная синхрогруппа (000111011) [4]. Однако, чем больше синхросимволов m в синхрогруппе, тем больше должна быть длительность цикла Тц (в двоичных символах), чтобы увеличение скорости передачи информации из-за введения циклового синхросигнала было сравнительно малым. В [4] при моделировании работы данного устройства длительность цикла или количество двоичных символов (позиций) в одном цикле выбрана равной N=1200.

Время восстановления синхронизма измеряют в циклах или цикловых интервалах (ЦИ) [3], поэтому длительность ЦИ в основном и определяет время восстановления синхронизма, Соответственно данному устройству требуется большое число R=NGвc двоичных символов на восстановление синхронизма, где Gвc - время восстановления синхронизма в ЦИ, из-за чего теряется большой блок информационных символов при каждом сбое синхронизма.

3. Для уменьшения времени восстановления синхронизма кодовых комбинаций требуется с высокой достоверностью и за минимально возможное время определять сбой синхронизма. Кроме того, после восстановления синхронизма требуется заблокировать выход решающего узла устройства с целью повышения помехоустойчивости устройства за счет исключения ложного обнаружения синхронизма (ложного срабатывания решающего узла).

В данном устройстве сбой синхронизма определяется далеко не оптимальным способом. При сбое синхронизма счетчик по выходу из синхронизма суммирует подряд следующие импульсы с выхода элемента запрета, соответствующие отсутствующим откликам на выходе опознавателя синхросигнала. Однако, любая ложно принятая синхрогруппа, отклик от которой совпадает во времени с цикловым импульсом формирователя цикловых импульсов, одиночный символ 1 с выхода первого элемента «И» через первый вход элемент «ИЛИ» подается на вход сброса указанного счетчика, обнуляя его содержимое. В результате подсчет подряд следующих импульсов с выхода элемента запрета начинается заново. Это может повторяется до тех пор, пока за счетчик по выходу из синхронизма не произведет подсчет заданного количества подряд следующих импульсов с выхода элемента запрета. И только после этого с выхода этого счетчика на дополнительный управляющий вход решающего узла поступит «единичный» логический уровень - лог, 1, разрешающий поиск новой цикловой фазы входного сигнала (новой временной позиции синхронизма). Это может существенно увеличить время восстановления синхронизма.

С другой стороны, такой алгоритм работы счетчика по выходу из синхронизма не приводит к повышению достоверности установления синхронизма кодовых комбинаций, поскольку импульсный сигнал синхронизации с выхода решающего узла фазирует формирователь цикловых импульсов и одновременно поступает через элемент «ИЛИ» на вход счетчика, обнуляя его, и запрещающий «нулевой» уровень с его выхода блокирует выход решающего узла, что может означать, что синхронизм восстановлен (ложный).

4. При обнаружении сбоя синхронизма кодовых комбинаций обнуления блока памяти решающего узла и блока регистров сдвига не производится, что создает условия для ложного обнаружения синхронизма. Поскольку ложное обнаружение синхронизма может произойти при одном из сбоев синхронизма в наиболее вероятный начальный интервал времени поиска после обнаружения сбоя синхронизма. В этот интервал времени остаточная информация, соответствующая прежней позиции синхронизма, сохраняется в блоке регистров сдвига и блоке памяти решающего узла. Новая информация, соответствующая новой позиции синхронизма, накладывается на прежнюю информацию, что нарушает оптимальный алгоритм поиска [5], и в этот интервал времени наиболее вероятно ложное обнаружение синхронизма.

Задачами, на решение которых направлено настоящее изобретение -устройство синхронизации кодовых комбинаций являются:

1. Повышение помехоустойчивости приема кодовых комбинаций за счет исключения передачи совместно с основой информацией циклового синхросигнала и соответствующего понижения скорости передачи информации.

2. Сокращение времени поиска синхронизма за счет сокращения длительности цикла до длительности кодовой комбинации и оптимизации процесса обнаружения синхронизма с требуемой достоверностью с учетом вероятности ошибочного приема кодовой комбинации входной двоичной последовательности.

3. Уменьшение вероятности ложного обнаружения синхронизма кодовых комбинаций путем стирания прежней накопленной синхроинформации в блоке регистров сдвига и в блоке памяти решающего узла после обнаружения сбоя синхронизма.

4. Уменьшение потерь двоичной информации при сбоях синхронизма путем оптимизации процессов обнаружения сбоя и восстановления синхронизма кодовых комбинаций.

Решение поставленных задач достигается тем, что в устройство синхронизации кодовых комбинаций, содержащее опознаватель синхросигнала, первый элемент запрета, первый элемент «И», сумматор, блок регистров сдвига, решающий узел, формирователь цикловых импульсов, счетчик циклов, первый элемент «ИЛИ», первый и второй блоки выбора порога, причем на тактовый и информационный входы устройства, которыми являются тактовый и информационный входы опознавателя синхросигнала, поступают соответственно последовательность тактовых импульсов и двоичная последовательность n-символьных кодовых комбинаций равномерного кода с обнаружением или исправлением ошибок, а выход опознавателя синхросигнала объединен с первыми входами первого элемента запрета и первого элемента «И», а также с первым входом сумматора, выход которого подключен к сигнальному входу блока регистров сдвига, основной и дополнительный выходы которого подключены соответственно к второму входу сумматора и сигнальному входу решающего узла, тактовый вход которого объединен с соответствующими входами блока регистров сдвига, и формирователя цикловых импульсов, выход которого, являющийся выходом устройства, объединен с вторыми входами первого элемента запрета и первого элемента «И», а также с входом счетчика циклов, при этом вход сброса формирователя цикловых импульсов объединен с первым входом первого элемента «ИЛИ» и выходом решающего узла, управляющий вход которого подключен к выходу первого блока выбора порога, адресный вход которого объединен с адресным входом второго блока выбора порога.

Решающий узел состоит из первого блока сравнения, первого блока памяти, первого блока вычитания, второго блока сравнения, счетчика сравнения и второго элемента «И», причем сигнальным входом решающего узла является первый вход первого блока вычитания, объединенный с входом данных первого блока памяти и первым входом первого блока сравнения, выход которого соединен с входом управления первого блока памяти, выход которого объединен с вторыми входами первого блока сравнения и первого блока вычитания, выход которого подключен к первому входу второго блока сравнения, выход которого подключен к входу сброса счетчика сравнения, выход которого подключен к первому входу второго элемента «И», выход которого является выходом решающего узла, управляющим, тактовым и первым дополнительным управляющим входами которого являются соответственно второй вход второго блока сравнения, тактовый вход счетчика сравнения и второй вход второго элемента «И».

Дополнительно введены второй элемент «ИЛИ», первый триггер и последовательно соединенные первый накапливающий сумматор, третий блок сравнения и первый формирователь импульса, выход которого объединен с вторым входом первого элемента «ИЛИ» и первыми входами второго элемента «ИЛИ» и первого триггера, выход которого подключен к первому дополнительному управляющему входу решающего узла, второй дополнительный управляющий вход которого, являющийся входом сброса первого блока памяти решающего узла, объединен с входом сброса блока регистров сдвига и выходом первого элемента «ИЛИ».

Кроме того, дополнительно введены последовательно соединенные второй блок вычитания, второй накапливающий сумматор, четвертый блок сравнения и второй формирователь импульса, выход которого объединен с вторыми входами первого триггера и второго элемента «ИЛИ», выход которого объединен с входами сброса первого и второго накапливающих сумматоров, третий вход второго элемента «ИЛИ» дополнительно подключен к выходу решающего узла.

Дополнительно введены также первый и второй элементы задержки, а также третий накапливающий сумматор, выход которого подключен к входу данных второго блока памяти, вход управления которого объединен с выходом счетчика циклов и входом первого элемента задержки, выход которого подключен к входу сброса третьего накапливающего сумматора, а выход второго блока памяти подключен дополнительно к адресному входу второго блока выбора порога, выход которого объединен с другими входами третьего и четвертого блоков сравнения, входы синхронизации первого, второго и третьего накапливающих сумматоров объединены с выходом второго элемента задержки, вход которого подключен дополнительно к выходу формирователя цикловых импульсов, тактовый вход которого, дополнительно подключен к дополнительному выходу опознавателя синхросигнала, выход первого элемента «И» подключен к первому входу второго блока вычитания, второй вход которого объединен с выходом элемента запрета и сигнальными входами первого и третьего накапливающих сумматоров.

Кроме того, опознаватель синхросигнала содержит последовательно соединенные третий элемент задержки, формирователь управляющих импульсов, счетчик управления, дешифратор, третий элемент «ИЛИ» и второй триггер, первый выход которого подключен к входу сброса счетчика управления, а другой вход второго триггера соединен с входом четвертого элемента задержки, выход которого подключен к первому входу третьего триггера, выход которого является выходом опознавателя синхросигнала, тактовым входом и дополнительным выходом которого являются соответственно вход и выход третьего элемента задержки, выход которого дополнительно подключен к другому выходу второго триггера.

Кроме того, опознаватель синхросигнала содержит n-разрядный регистр сдвига с порядковыми номерами разрядов i=1, 2, …, n, соответствующими порядку их следования - от старшего выходного разряда - при i=1, к младшему входному разряду, который является информационным входом опознавателя синхросигнала - при i=n, блок памяти разрешенных кодовых комбинаций (БПРКК) с аналогичными порядковыми номерами выходов, соответствующими порядку следования двоичных символов с порядковыми номерами i=1, 2, …, n в каждой кодовой комбинации входного сигнала, адресный вход БПРКК подключен дополнительно к выходу счетчика управления, а также n элементов равнозначности с такими же порядковыми номерами i=1, 2, …, n, и третий элемент «И», выход которого подключен к первому входу второго элемента запрета, второй вход которого подключен дополнительно к выходу формирователя управляющих импульсов, а выход второго элемента запрета объединен с другим входом третьего элемента «ИЛИ» и вторым входом третьего триггера, первый и второй входы каждого элемента равнозначности с соответствующим порядковым номером i подключены соответственно к разрядному выходу n-разрядного регистра сдвига с таким же порядковым номером i и выходу БПРКК с таким же порядковым номером i, а выходы всех n элементов равнозначности подключены к соответствующим n входам третьего элемента «И», (n+1)-й вход которого подключен к второму выходу второго триггера.

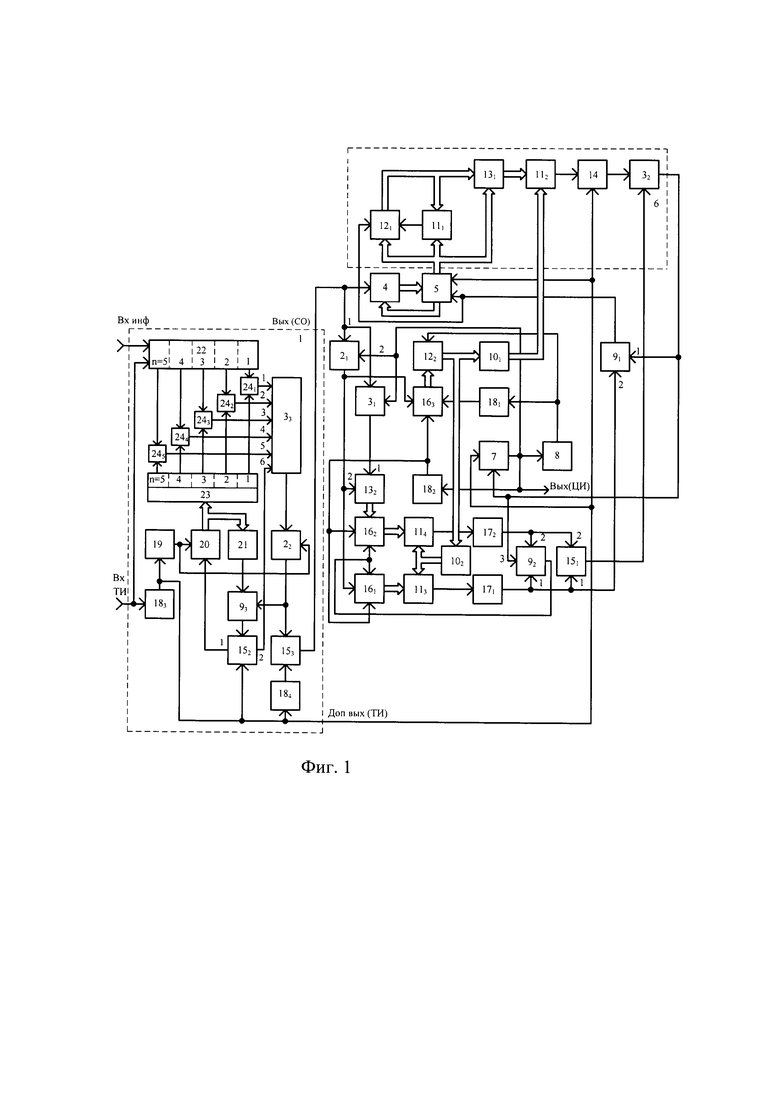

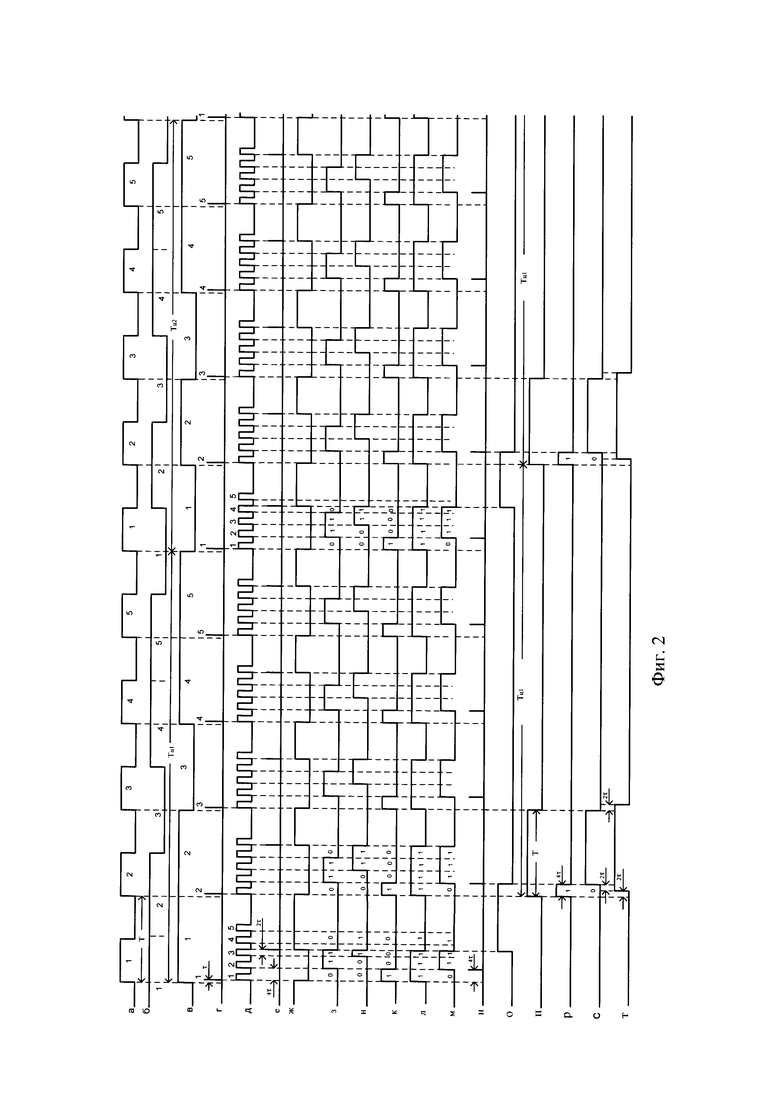

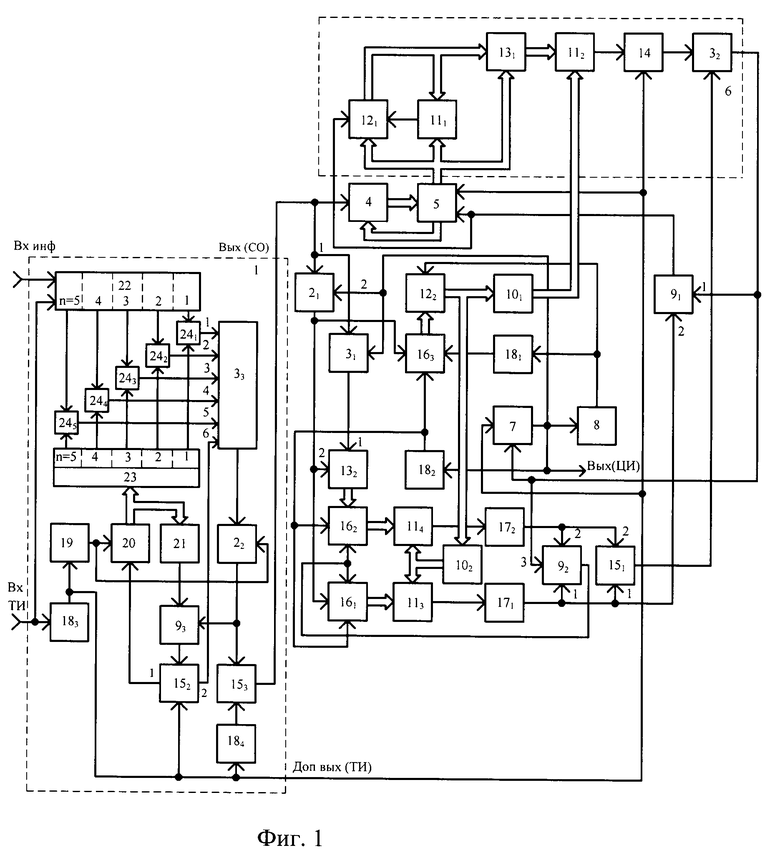

На фиг. 1 представлена схема электрическая структурная устройства синхронизации кодовых комбинаций для приема двоичной последовательности, закодированной гипотетическим равномерным кодом (5,2). На фиг. 2 приведены временные диаграммы работы устройства.

Устройство синхронизации кодовых комбинаций содержит опознаватель синхросигнала 1, первый элемент запрета 21, первый элемент «И» 31 сумматор 4, блок регистров сдвига 5, решающий узел 6, формирователь цикловых импульсов 7, счетчик циклов 8, первый элемент «ИЛИ» 91, первый блок выбора порога 101 и второй блок выбора порога 102.

На тактовый и информационный входы устройства, которыми являются тактовый и информационный входы опознавателя синхросигнала 1, поступают соответственно последовательность тактовых импульсов и двоичная последовательность n-символьных кодовых комбинаций. Выход опознавателя синхросигнала 1 объединен с первыми входами первого элемента запрета 21 и первого элемента «И» 31, а также первым входом сумматора 4, выход которого подключен к сигнальному входу блока регистров сдвига 5, основной и дополнительный выходы которого подключены соответственно к второму входу сумматора 4 и сигнальному входу решающего узла 6, тактовый вход которого объединен с соответствующими входами блока регистров сдвига 5 и формирователя цикловых импульсов 7, выход которого, являющийся выходом устройства, объединен с вторыми входами первого элемента запрета 21, первого элемента «И» 31 и с входом счетчика циклов 8. Вход сброса формирователя цикловых импульсов 7 объединен с первым входом первого элемента «ИЛИ» 9i и выходом решающего узла 6, управляющий вход которого подключен к выходу первого блока выбора порога 101, адресный вход которого объединен с адресным входом второго блока выбора порога 102.

Решающий узел 6 состоит из первого блока сравнения 111, первого блока памяти 121, первого блока вычитания 131, второго блока сравнения 112, счетчика сравнения 14 и второго элемента «И» 32, причем сигнальным входом решающего узла является первый вход первого блока вычитания 131, объединенный с входом данных первого блока памяти 121 и первым входом первого блока сравнения 111, выход которого соединен с входом управления первого блока памяти 121, выход которого объединен с вторыми входами первого блока сравнения 111 и первого блока вычитания 131, выход которого подключен к входу второго блока сравнения 112, выход которого подключен к входу сброса счетчика сравнения 14, выход которого подключен к первому входу второго элемента «И» 32, выход которого является выхода решающего узла 6, управляющим, тактовым и первым дополнительным управляющим входами которого являются соответственно второй вход второго блока сравнения 112, тактовый вход счетчика сравнения 14 и второй вход второго элемента «И» 32.

Устройство также содержит второй элемент «ИЛИ» 92, первый триггер 151 и последовательно соединенные первый накапливающий сумматор 161, третий блок сравнения 113 и первый формирователь импульса 171, выход которого объединен с вторым входом первого элемента «ИЛИ» 91 и первыми входами второго элемента «ИЛИ» 92 и первого триггера 151, выход которого подключен к первому дополнительному управляющему входу решающего узла 6, второй дополнительный управляющий вход которого, являющийся входом сброса первого блока памяти 121 решающего узла 6, объединен с входом сброса блока регистров сдвига 5 и выходом первого элемента «ИЛИ» 91.

Кроме того, устройство содержит последовательно соединенные второй блок вычитания 132, второй накапливающий сумматор 162, четвертый блок сравнения 114 и второй формирователь импульса 172, выход которого объединен с вторыми входами первого триггера 151 и второго элемента «ИЛИ» 92, выход которого объединен с входами сброса первого и второго накапливающих сумматоров (161, 162).

Устройство содержит также первый и второй элементы задержки (181, 182), а также третий накапливающий сумматор 163, выход которого подключен к входу данных второго блока памяти 122, вход управления которого объединен с выходом счетчика циклов 8 и входом первого элемента задержки 181, выход которого подключен к входу сброса третьего накапливающего сумматора 163, а выход второго блока памяти 122, подключен дополнительно к адресному входу второго блока выбора порога 102, выход которого объединен с другими входами третьего и четвертого блоков сравнения (113, 114), входы синхронизации первого, второго и третьего накапливающих сумматоров (161, 162, 163) объединены с выходом второго элемента задержки 182, вход которого подключен дополнительно к выходу формирователя цикловых импульсов 7, тактовый вход которого, дополнительно подключен к дополнительному выходу опознавателя синхросигнала 1, выход первого элемента «И» 31 подключен к первому входу второго блока вычитания 13 2, второй вход которого объединен с выходом элемента запрета 21 и сигнальными входами первого и третьего накапливающих сумматоров (161, 162).

Опознаватель синхросигнала 1 содержит последовательно соединенные третий элемент задержки 183, формирователь управляющих импульсов 19, счетчик управления 20, дешифратор 21, третий элемент «ИЛИ» 93 и второй триггер 152, первый выход которого подключен к входу сброса счетчика управления 20, а другой вход второго триггера 152 соединен с входом четвертого элемента задержки 184, выход которого подключен к первому входу третьего триггера 153, выход которого является выходом опознавателя синхросигнала 1, тактовым входом и дополнительным выходом которого являются соответственно вход и выход третьего элемента задержки 183, выход которого дополнительно подключен к другому входу второго триггера 15 г,

Кроме того, опознаватель синхросигнала 1 содержит (n=5)-разрядный регистр сдвига 22 с порядковыми номерами разрядов i=1, 2, …, 5, соответствующими порядку их следования - от старшего выходного разряда - при i=1, к младшему входному разряду, который является информационным входом опознавателя синхросигнала - при i=5, блок памяти разрешенных кодовых комбинаций (БПРКК) 23 с аналогичными порядковыми номерами выходов, соответствующими порядку следования двоичных символов с порядковыми номерами i=1, 2, …, 5 в каждой кодовой комбинации входного сигнала, адресный вход БПРКК дополнительно подключен к выходу счетчика управления 20, а также n=5 элементов равнозначности (241, …, 245) с такими же порядковыми номерами i=1, 2, …, 5, и третий элемент «И» 33, выход которого подключен к первому входу второго элемента запрета 22, второй вход которого дополнительно подключен к выходу формирователя управляющих импульсов 19, а выход второго элемента запрета 21 объединен с другим входом третьего элемента «ИЛИ» 93 и вторым входом третьего триггера 152, первый и второй входы каждого элемента равнозначности (241, …, 245) с соответствующим порядковым номером i подключены соответственно к разрядному выходу 5-разрядного регистра сдвига 22 с таким же порядковым номером i и выходу БПРКК 23 с таким же порядковым номером i, а выходы всех 5 элементов равнозначности (241, …, 245) подключены к соответствующим 5 входам третьего элемента «И» 33, 6-й вход которого подключен к второму выходу второго триггера 152.

Устройство синхронизации кодовых комбинаций работает следующим образом.

Принимаемая двоичная последовательность, закодированная гипотетическим равномерным 5-символьным кодом (5,2), выбранным для более наглядного представления работы устройства, подается на информационный вход 5-разрядного регистра сдвига 22, который является информационным входом опознавателя синхросигнала 1 и устройства (фиг. 1) вцелом.. Здесь каждая кодовая комбинация содержит п=5 двоичных символов с порядковыми номерами i=1, 2, …, 5, из них k=2 информационных символа и n - k=3 проверочных (корректирующих) символа.

На фиг. 2 приведены временные диаграммы работы устройства при приеме отрезка двоичной последовательности, состоящего из двух следующих друг за другом разрешенных кодовых комбинаций гипотетического кода (5,2) вида: 11011 и 01011 (фиг. 2, б) из No=2k=4 возможных разрешенных кодовых комбинаций, например, с условными порядковыми номерами j=1, 2, 3, 4: 1) 00110,2) 10011,3) 11011,4) 01011. Здесь из общего количества Nобщ=2n=32 возможных кодовых комбинаций Nобщ - No=28 являются запрещенными. В качестве источника цикловой синхронизирующей информации в данном случае используется последовательность из No<Nобщ разрешенных кодовых комбинаций, при этом длительность каждого цикла Тц равна длительности одной кодовой комбинации, т.е. Тц=n (двоичных символов).

Под действием тактовых импульсов (ТИ), поступающих на тактовый вход опознавателя синхросигнала 1 (фиг.2, а), входная двоичная последовательность (фиг. 2, б) продвигается по разрядам 5-разрядного регистра сдвига 22 с порядковыми номерами разрядов i=1, 2, 5, 4, 5. На фиг. 2, в зафиксировано синхронное состояние первого цикла Тц1 входной двоичной последовательности в разрядах 5-разрядого регистра сдвига 22 после поступления соответствующего - 1-го, тактового импульса (фиг. 2, а), когда 1-й двоичный символ первой кодовой комбинации размещается в 1-м разряде регистра сдвига 22, 2-й символ - во 2-м разряде этого регистра сдвига и т.д.. Таким образом, кодовая комбинация первого цикла Тц1 с условным порядковым номером j=3, т.е. 3) 11011, полностью размещается в разрядах 5-разрядного регистра сдвига 22. После поступления следующих ТИ данного цикла в синхронном состоянии (в 5-разрядном регистре сдвига 22) будет находиться следующая кодовая комбинация второго цикла Тц2. - 4) 01011 и т.д. При этом в каждом из элементов равнозначности 241, …, 245 с порядковым номером i=1, 2, 5, 4, 5, в котором к двум его входам подключены соответственно разрядный выход 5-разрядого регистра сдвига 22 с таким же порядковым номером и выход блока памяти разрешенных кодовых комбинаций (БПРКК) 23 с таким же порядковым номером, производится сравнение значений логических уровней (напряжений) i-го символа (0 или 1) кодовой комбинации регистра сдвига 22 и i-го символа каждой из No разрешенных кодовых комбинаций, последовательно коммутируемых в БПРКК 23 в пределах соответствующего тактового интервала длительностью Т (фиг. 2, а).

БПРКК может состоять, например, из No n-разрядных регистров хранения [11], каждому из которых присвоен условный порядковый номер j=1, 2,…, No с соответствующим адресом в цифровой форме, и в разряды каждого из которых с порядковыми номерами, аналогичными порядковым номерам разрядов n-разрядного регистра сдвига 22, записана посимвольно соответствующая разрешенная кодовая комбинация с условным порядковым номером j и порядковыми номерами символов, совпадающих с порядковыми номерами разрядов, в которых они записаны. При поступлении на адресный вход БПРКК выбранного адреса j в цифровой форме, n разрядных выходов соответствующего j-го регистра хранения с помощью устройств коммутации подключаются к соответствующим n выходам БПРКК, порядковые номера которых совпадают с порядковыми номерами разрядов каждого из 77-разрядных регистра хранения.

В качестве БПРКК также может быть использовано перепрограммируемое постоянное запоминающее устройство (ППЗУ), в n-разрядные ячейки памяти которого записаны (прошиты) разрешенные кодовые комбинации с учетом порядка записи символов кодовых комбинаций, изложенного выше. Различные модификации ППЗУ широко выпускаются промышленностью многих стран мира в виде интегральных микросхем.

Под управлением счетчика управления 20 производится последовательная коммутация на выходы БПРКК логических уровней соответствующих символов разрешенных кодовых комбинаций в параллельном коде, каждая из которых записана в соответствующие n-разрядные ячейки памяти БПРКК по соответствующему адресу. Для этого при поступлении каждого тактового импульса (ТИ) с выхода третьего элемента задержки 182 (фиг. 2, г), задержанного на некоторую величину τ относительно ТИ входной последовательности тактовых импульсов (фиг.2, а), на выходе формирователя управляющих импульсов 19 формируется последовательность из No+1=5 управляющих импульсов (фиг. 2, д) в пределах каждого тактового интервала длительностью Т (фиг. 2, а).

Формирование последовательности управляющих импульсов в формирователе управляющих импульсов 19 может осуществляться, например, с помощью D=2No+1 идентичных последовательно соединенных формирователей одиночных импульсов с порядковыми номерами d=1, 2, 3, …, D. Причем каждый последующий формирователь одиночного импульса выбранной длительности 2τ (фиг. 2, д), запускается от заднего фронта импульса, формируемого предыдущим формирователем одиночного импульса, первый из которых с порядковым номером d=1, запускается от соответствующего ТИ с выхода третьего элемента задержки 183 (фиг. 2, г). При этом выход каждого формирователя одиночного импульса с нечетным порядковым номером должен быть подключен к соответствующему входу элемента «ИЛИ», выход которого должен является выходом формирователя управляющих импульсов 19, формирующим последовательность из No+1=5 управляющих импульсов. Каждый формирователь одиночного импульса может быть выполнен, например, на основе мультивибратора. Возможны и другие варианты реализации формирователя 19.

В исходном состоянии (до прихода очередного ТИ с выхода третьего элемента задержки 183) второй триггер 152 установлен в «единичное» состояние, при котором с его первого выхода на вход сброса счетчика управления 20 поступает «единичный» логический уровень - лог. 1. При этом счетчик управления 20 установлен в «нулевое» состояние, при котором на каждом из его разрядных выходах, совокупность которых образует цифровой управляющий выход, фиксируется «нулевой» логический уровень - лог. 0. Этот «нулевой» управляющий цифровой сигнал («ООО») в параллельном коде, формируемый в данном случае из трех разрядных выходов счетчика управления 20, подается на адресный вход дешифратора 21 и БПРКК 23, который подключает на его выходы логические уровни 5-символьной кодовой комбинации в параллельном коде, которая оказалась записанной в n-разрядную ячейку памяти по «нулевому» адресу. При этом третий элемент «И» 33 при любой кодовой комбинации, записанной в БПРКК 22 по «нулевому» адресу, не срабатывает - на его выходе сохраняется лог 0, поскольку блокируется «нулевым» логическим уровнем (лог. 0), на (n+1=6)-м входе этого элемента (вход блокировки), поступающим с второго выхода второго триггера 152.

Каждый очередной тактовый импульс с выхода третьего элемента задержи 183 устанавливает второй триггер 152 в «нулевое» состояние - лог. 0, на первом его выходе (фиг. 2, ж) и лог. 1 - на втором выходе. В результате на вход сброса счетчика управления 20 поступит лог. 0, разрешающий счет управляющих импульсов, поступающих на его тактовый вход. Одновременно на 6-й вход (вход блокировки) третьего элемента «И» 33 поступит лог. 1, разрешая его срабатывание - формирование лог. 1 на его выходе при наличии лог.1 на каждом из других его 5-ти входах с выходов соответствующих элементов равнозначности 241, …, 245. Кроме того, каждый очередной тактовый импульс запускает в соответствующем тактовом интервале формирование последовательности из No+1=5 управляющих импульсов с выхода формирователя управляющих импульсов 19 (фиг.2 , д). Счетчик управления 20 в каждом тактовом интервале с приходом первого управляющего импульса производит счет одного импульса - на трех его разрядных выходах формируется управляющий цифровой сигнал «001» в двоичном коде, по которому БПРКК 23 обеспечивает коммутацию на свои 5 выходов логических уровней соответствующих символов разрешенной кодовой комбинации, хранящихся в n-разрядной ячейке памяти с условным порядковым номером j=1, т.е. 1) 00110 (фиг. 2, з, и, к, л, м). Логические уровни символов этой комбинации сравниваются в элементах равнозначности 241, …, 245 с логическими уровнями соответствующих символов кодовой комбинации, находящихся в данном тактовом интервале в соответствующих разрядах 5-разрядого регистра сдвига 22, т.е. 11011 (фиг. 2,.в). Если, хотя бы в одном из элементах равнозначности 241, …, 245 имеет место несовпадение логических уровней на его входах, то на выходе этого элемента появится лог.0, который блокирует срабатывание третьего элемента «И» 33. Соответственно на выходе этого элемента «И» 33 будет фиксироваться лог.0, поступающий на первый вход второго элемента запрета 2 г, при котором на его выходе также будет фиксироваться лог.0 при любых значениях логического уровня на другом его входе. При этом состояние второго триггера 152 не изменится, поскольку на выходе третьего элемента «ИЛИ» 93 также будет лог. 0.

При поступлении 2-го управляющего импульса (фиг. 2,.д) на вход счетчика управления 20, на его разрядных выходах появится число 2 в двоичном коде «010», по которому БПРКК 23 обеспечит коммутацию на свои выходы логических уровней соответствующих символов разрешенной кодовой комбинации, записанной в его память с условным порядковым номером j=2, т.е. 2) 10011 (фиг. 2, з, и, к, л, м). Некоторые уровни символов этой кодовой комбинации, как и предыдущей кодовой комбинации, не совпадают с уровнями символов сравниваемой кодовой комбинации (11011), в результате на выходах соответствующих элементов равнозначности 241, …, 245 фиксируются «нулевые» логические уровни (лог. 0), любой из них блокирует срабатывание третьего элемента «И» 33, и состояние второго триггера 152 также не изменится.

При поступлении 3-го управляющего импульса с выхода формирователя управляющих импульсов 19, на выходе счетчика управления 20 появится число 3 в двоичном коде «011», по которому БПРКК 23 обеспечит коммутацию на свои выходы логических уровней соответствующих символов разрешенной кодовой комбинации с условным порядковым номером j=3, т.е. 3) 11011 (фиг. 2, з, и, к, л, м). Логические уровни символов этой кодовой комбинации полностью совпадают с уровнями символов синхронной разрешенной кодовой комбинации (11011), полностью располагаемой в разрядах 5-разрядного регистра сдвига 22. В результате на выходе каждого элемента равнозначности 241, …, 245 появится лог. 1, в результате третий элемент «И» 33 срабатывает - на его выходе появляется лог. 1, который подается на вход второго элемента запрета 22. На выходе этого элемента запрета и на выходе третьего элемента «ИЛИ» 93 (фиг. 2, е) будет сохраняться лог. 0 до окончания действия 3-го управляющего импульса длительностью 2τ. С приходом лог. 0 на второй вход второго элемента запрета 22 с выхода формирователя импульсов 19 после окончания 3-го управляющего импульса, на выходе второго элемента запрета 22 и на выходе третьего элемента «ИЛИ» 93 появится лог. 1. Этот лог. 1 устанавливает второй триггер 152 в исходное состояние, обнуляя счетчик управления 20 и блокируя третий элемент «И» 33, из-за чего лог. 1 на выходе второго элемента запрета 22 и третьего элемента «ИЛИ» 93 обрывается, и на выходе третьего элемента «ИЛИ» 93 формируется узкий импульс (фиг. 2, е). Одновременно по переднему фронту этого импульса третий триггер 153 устанавливается в «единичное» состояние, и лог. 1 с его выхода поступает на выход опознавателя синхросигнала 1. На этом процесс обнаружения разрешенной кодовой комбинации в данном (первом) тактовом интервале считается завершенным, т.к. обнаружена разрешенная кодовая комбинация 11011.

Перед приходом следующего, 2-го ТИ с выхода третьего элемента задержки 183 , двоичная последовательность в 5-разрядном регистре сдвига 22 под действием 2-го ТИ на входе опознавателя синхросигнала 1 (фиг. 2, а) сдвигается на один разряд - на временной диаграмме (фиг. 2, г) такой сдвиг означает сдвиг в левую сторону. В данном случае в разрядах 5-разрядного регистра сдвига 22 будет находиться запрещенная кодовая комбинация 10110. С приходом 2-го ТИ с выхода третьего элемента задержки 183 триггеры 152 (фиг. 2, ж) и 153 устанавливаются в нулевое состояние, причем, третий триггер 153 (фиг. 2, о) устанавливается в «нулевое» состояние с задержкой 4τ, определяемой четвертым элементом задержки 184 (фиг. 2, н). При этом на выход опознавателя синхросигнала 1 поступает сформированный третьим триггером 153 импульсный отклик (фиг.2, о), соответствующий во времени первой разрешенной кодовой комбинации 1-го цикла Тц1.

Одновременно с приходом 2-го ТИ с выхода третьего элемента задержки 183 во 2-м тактовом интервале начинается процесс, аналогичный процессу в предыдущем 1-м тактовом интервале. Однако, поскольку запрещенная кодовая комбинация 10110, находящаяся в данном тактовом интервале в разрядах 5-разрядого регистра сдвига 22 не совпадает ни с одной разрешенной кодовой комбинацией БПРКК, то третий элемент «И» 33. не срабатывает после поступления каждого из четырех управляющих импульсов (фиг. 2, д) на вход счетчика управления 20. Поэтому этот счетчик начинает счет следующего (максимально возможного) 5-го управляющего импульса. При этом, как только на выходе счетчика управления 20 появляется управляющий цифровой сигнал «101» (число 5 в двоичном коде), на которое реагирует дешифратор 21, и на выходе этого дешифратора появится лог. 1. Этот «единичный» логический уровень, проходя через третий элемент «ИЛИ» 93, устанавливает второй триггер 152 в исходное состояние, обнуляя счетчик управления 20, из-за чего лог.1 на выходах дешифратора 21 и третьего элемента «ИЛИ» 93 обрывается, и на выходе третьего элемента «ИЛИ» 93 формируется узкий импульс (фиг. 2, е). Это означает, что при поступлении 2-го ТИ на вход опознавателя синхросигнала 1 (фиг. 2, а) в 5-ти разрядах регистре сдвига 22 размещается в течении 2-го тактового интервала запрещенная кодовая комбинация, в данном случае - 10110.

Аналогичные действия происходят и при поступлении на вход опознавателя синхросигнала 1 3-го, 4-го и 5-го ТИ первого цикла Тц1 за исключением того, что на выходе опознавателя синхросигнала 1 импульсный отклик отсутствует (фиг.2, о). В этих случаях в регистре сдвига 22 будут размещаться последовательно следующие запрещенные кодовые комбинации: 01101, 11010, 10101,

При поступлении следующего ТИ, которым является 1-й тактовый импульс 2-го цикла Тц2 (фиг. 2, а), в 5-разрядном регистре сдвига 22 будет размещаться разрешенная кодовая комбинация 01011, копия которой хранится в БПРКК с условным порядковым номером j=4. Процесс обнаружения в пределах 1-го тактового интервала 2-го цикла Тц2 в разрядах регистра сдвига 22 другой разрешенной кодовой комбинации 01011 аналогичен ранее приведенному процессу обнаружения разрешенной кодовой комбинации 11011 в пределах 1-го тактового интервала 1-го цикла Тц1. Отличие заключается только в том, что обнаружение разрешенной комбинации 01011 происходит при поступлении 4-го управляющего импульса с выхода формирователя импульсов 19 (фиг. 2, д). При этом на выходе счетчика управления 20 появится число 4 в двоичном коде (100), по которому БПРКК 23 обеспечивает подключение на свои выходы логические уровни соответствующих символов разрешенной кодовой комбинации с условным порядковым номером j=4, т.е. 4) 01011 (фиг. 2, з, и, к, л, м). Логические уровни символов этой кодовой комбинации полностью совпадают с уровнями символов синхронной кодовой комбинации (01011), полностью располагаемой в разрядах 5-разрядного регистра сдвига 22. Дальнейшие действия аналогичны изложенным выше при описании обнаружения разрешенной кодовой комбинации 11011 при поступлении 3-го управляющего импульса. При этом на выход опознавателя синхросигнала 1 поступает сформированный третьим триггером 153 импульсный отклик на разрешенную кодовую комбинацию (фиг. 2, о), в результате на выходе опознавателя синхросигнала 1 формируется последовательность откликов на разрешенные кодовые комбинации (в том числе и возможные ложные отклики на ложные разрешенные комбинации).

Последовательность откликов с выхода опознавателя синхросигнала 1 подается на первый вход сумматора 4. На второй вход сумматора 4 с выхода блока регистров сдвига 5 подаются с тактовой частотой следования двоичные z-разрядные числа в параллельном коде.

Сумматор 4 представляет собой параллельный комбинационный сумматор [6], у которого младший разрядный вход первого слагаемого и z разрядных входов второго слагаемого являются соответственно первым и вторым входами сумматора 4, при этом другие (z - 1) разрядные входы первого входа подключены к источнику «нулевого» уровня.

Блок 5 регистров сдвига включает в себя z n-разрядных (n - число позиций в одном цикле или число символов в одной кодовой комбинации) регистров сдвига, у которых раздельно объединены тактовые входы и входы сброса. При этом объединенные тактовые входы и объединенные входы сброса регистров сдвига в составе блока регистров сдвига 5 являются, соответственно тактовым входом и входом сброса блока регистров сдвига 5, а сигнальные входы, выходы последних разрядов и выходы первых разрядов всех z регистров сдвига являются соответственно сигнальным входом, выходом и дополнительным выходом блока регистров сдвига 5.

Таким образом, отклик опознавателя синхросигнала 1, имеющий место в i-ом тактовом интервале, складывается в сумматоре 4 с результатом предыдущего счета откликов на i-й позиции цикла, поступающим с выхода блока регистров сдвига 5, и новый результат счета откликов, больший на единицу прежнего, записывается в виде z-разрядного двоичного числа в первые разряды z регистров сдвига блока регистров сдвига 5.

При этом двоичное число, записанное до этого в первые разряды блока регистров сдвига 5, а также все остальные числа, хранящиеся в последующих однотипных разрядах, параллельно сдвигаются на один разряд, и с выхода блока регистров сдвига 5 на второй вход сумматора 4 поступает уже следующий результат счета откликов - на (i+1)-й позиции цикла, который перезаписывается в первые разряды блока регистров сдвига 5, а остальные числа, хранящиеся в однотипных разрядах блока 5 регистров сдвига, сдвигаются на один разряд и т.д. т.е. блок регистров сдвига 5 обеспечивает запоминание результатов счета откликов на каждой позиции цикла в течении длительности цикла. При этом величина z определяет емкость памяти результатов счета.

Одновременно результаты счета откликов на каждой из позиций цикла с дополнительного выхода блока регистров сдвига 5 последовательно поступают на сигнальный вход решающего узла 6. В решающем узле 6, например, на i-м тактовом интервале, двоичное число в параллельном коде, представляющее текущий результат счета откликов на i-й позиции цикла, одновременно подается на соответствующие входы первого блока сравнения 111 первого блока памяти 121 и первого блока вычитания 131. В первом блоке сравнения 111 входное число сравнивается с двоичным числом, хранящимся в первом блоке памяти 121 и, если оно превышает число первого блока 121 памяти, то на выходе первого блока 111 сравнения формируется импульс, который поступая на вход управления первого блока 121 памяти, обеспечивает стирание прежнего и запись нового (входного) числа. После этого на входах первого блока 111 сравнения оказываются равные двоичные числа. Если же входное число равно или меньше числа, хранящегося в первом блоке 121 памяти, то содержимого последнего не изменяется.

Таким образом, в первый блок 121 памяти перезаписывается наибольший текущий результат счета откликов на какой-либо позиции цикла, который далее сравнивается с результатами счета на последующих позициях цикла.

Получающаяся разность (между числом первого блока 121 памяти и входным числом) на выходе первого блока 131 вычитания 131 в виде двоичного числа в параллельном коде сравнивается во втором блоке сравнения 112 с пороговым числом Mr, поступающем на второй его вход (являющийся управляющим входом решающего узла 6) с выхода первого блока выбора порога 101. При этом, если число с выхода первого блока вычитания 131 меньше порогового числа Mr, то с выхода второго блока сравнения 112 на вход сброса счетчика сравнения 14 поступает «единичный» (запрещающий) потенциал, который устанавливает и удерживает его в «нулевом» состоянии. В противоположном случае, когда в i-м тактовом интервале число с выхода первого блока вычитания 131 равно или больше числа Mr, то с выхода второго блока сравнения 112 поступает «нулевой» (разрешающий) потенциал, и счетчик 14 сравнения производит счет одного тактового импульса, поступающего на его тактовый вход, являющийся тактовым входом решающего узла 6. При этом, если наибольшее двоичное число, записанное в первый блок памяти 121, в каком-либо j-м тактовом интервале и соответствующее результату накопления на j-й позиции цикла, будет превышать на величину равную или большую порогового числа Mr, поступающего с управляющего входа решающего узла, каждое из n-1 последующих чисел, поступающих друг за другом с дополнительного выхода блока регистров сдвига 5, то счетчик 14 сравнения произведет счет следующих подряд n-1 тактовых импульсов, поступающих с тактового входа решающего узла, после чего на его выходе формируется импульсный сигнал синхронизации. Этот сигнал, поступает через первый вход второго элемента «И» 32 на выход решающего узла, если на его первый дополнительный решающий вход, которым является второй вход второго элемента «И» 32, поступает «единичный» логический уровень с выхода первого триггера 151. С выхода решающего узла 6 импульсный сигнал синхронизации поступает через первый вход первого элемента ИЛИ 91 на вход сброса первого блока памяти 121, являющийся вторым дополнительным управляющим входом решающего узла 6, и вход сброса блока регистров сдвига 5, обнуляя их и на вход сброса формирователя цикловых импульсов 7, устанавливая фазу выходной последовательности цикловых импульсов 7 в синхронное состояние с последовательностью кодовых комбинаций входного сигнала. Одновременно с выхода решающего узла сигнал синхронизации поступает через третий вход второго элемента «ИЛИ» на входы сброса первого и второго накапливающих сумматоров, обнуляя их. Приведенный выше процесс поиска цикловой фазы или временного положения позиции синхронизма принимаемой двоичной последовательности с коррекцией фазы выходных цикловых импульсов проводится только тогда, когда обнаружен сбой синхронизма кодовых комбинаций. Процессы установления сбоя и восстановления синхронизма в данном устройстве будут рассмотрены ниже.

Процесс формирования пороговых чисел для решающего узла 6 производится следующим образом.

На первые входы первых элементов запрета 21 и «И» 31 поступают импульсы (отклики) опознавателя синхросигнала 1 (фиг.2, о), а на вторые их входы - импульсы формирователя цикловых импульсов 7 (фиг. 2, п). В режиме синхронизма совместное взаимодействие каждого из этих импульсов происходит на временном интервале длительностью 4τ, отсчитываемом относительно заднего фронта импульса с выхода опознавателя синхросигнала 1 (фиг. 2, о). Поэтому длительность выходных импульсов элементов запрета 21 и «И» 31, которую в дальнейшем необходимо учитывать в каждом цикловом интервале входного сигнала не должна превышать интервал времени длительностью 4τ (фиг.2, о, п, р, с, т).

При этом на выходе первого элемента «И» 31 формируется одиночный двоичный символ 1 длительностью 4τ (фиг. 2, р), если отклик опознавателя синхросигнала 1 не искажен - это означает, что соответствующая разрешенная кодовая комбинация принята правильно. В противном случае, на выходе первого элемента «И» 31вместо символа 1 длительностью 4τ появится символ 0 длительностью 4τ, если отклик искажен, т.е. отклик отсутствует во время действия соответствующего циклового импульса.

На выходе первого элемента запрета 21 формируется символ 1 длительностью 4τ, если отклик искажен. В противном случае, на выходе первого элемента запрета 21 вместо символа 1 длительностью 4τ, появится символ 0 длительностью 4τ (фиг. 2, с), если отклик не искажен.

Подсчитывая число R искаженных откликов в течении времени счета довольно большого Q числа цикловых импульсов, можно с определенной степенью точности периодически определять вероятность (частость) ошибочного приема разрешенной кодовой комбинации по формуле РОРК=R/Q, т.е. производить текущую оценку степени искажений n-элементных кодовых комбинаций.

Для этого на вход младшего разряда сигнального входа каждого из накапливающих сумматоров 161 и 163, подается с выхода второго элемента запрета 22 либо двоичный символ 0 (фиг. 2. с), либо двоичный символ 1, каждый длительностью 4τ. Остальные разрядные входы сигнальных входов накапливающих сумматоров 161 и 163 подключены к источнику «нулевого» уровня. Соответственно поступающий на входы этих устройств двоичный символ 1, либо двоичный символ 0, каждый длительностью 4τ совместно с символами 0 на остальных разрядных входах сигнальных входах следует считать как число один, либо число ноль каждое параллельном в двоичном коде, действующее на временном отрезке длительностью 4τ с условным обозначением «1» и «0» соответственно. Каждый из накапливающих сумматоров 161 и 163, в том числе и второй накапливающий сумматор 162, обладает селективными свойствами, т.е. позволяет производить операции сложения чисел в двоичном коде, подаваемых последовательно на их сигнальные входы только в пределах интервала, не превышающего длительность (в данном случае) 4τ в каждом цикловом интервале длительностью Тц (фиг. 2, с), поскольку тактируются задержанными на время 2τ во втором элементе 182 задержки цикловыми импульсами (фиг.2, т) с выхода формирователя 7.

Это объясняется тем, что каждый накапливающий сумматор (161, 162, 163) состоит из устройства сложения (комбинационного сумматора, либо арифметического устройства - АУ), выходные разряды которого подключены к соответствующим разрядным входам регистра хранения, разрядные выходы которого подключены к соответствующим разрядным входам цифрового входа устройства сложения [6]. Суммируемое число, например, «1» (один) в двоичном коде подается на другой цифровой вход (сигнальный вход) устройства сложения. Результат сложения, на единицу больший прежнего числа, хранящегося в соответствующем регистре хранения, появляется на выходе соответствующего устройства сложения. Этот результат перезаписывается в регистр хранения вместо прежнего числа в каждом накапливающем сумматоре, только при поступлении на вход синхронизации каждого накапливающего сумматора переднего фронта циклового импульса, задержанного во втором элементе задержки 182 на время 2 τ (фиг. 2, т) и совпадающего с интервалом 4τ. Другие уровни, действующие на входе младшего разряда сигнального входа каждого накапливающего сумматора до или после указанного временного интервала 4τ (фиг. 2, с), на результаты суммирования влияния не оказывают.

Следует отметить, что при использовании в качестве устройства сложения АУ, в накапливающих сумматорах обеспечивается и сложение и вычитание чисел в двоичном коде, подаваемых на сигнальный вход, т.е. алгебраическое сложение положительных и отрицательных чисел [6].

Таким образом, с помощью третьего накапливающего сумматора 163 производится подсчет R искаженных разрешенных кодовых комбинаций, а с помощью счетчика циклов 8 - общее число Q цикловых импульсов (ЦИ) или кодовых комбинаций. Коэффициент емкость счетчика циклов 8 выбирается равной величине Q, поэтому после счета каждых Q ЦИ на его выходе формируется одиночный импульс, поступающий на вход управления второго блока памяти 122 и на вход сброса третьего накапливающего сумматора 163 через первый элемент задержки 181 на время 2τ. В результате во второй блок памяти 122 записывается новый результат счета R искаженных разрешенных кодовых комбинаций с выхода третьего накапливающего сумматора 163, после чего этот накапливающий сумматор обнуляется и процесс подсчета количества R искаженных разрешенных кодовых комбинаций и Q цикловых импульсов повторяется.

Первый блок выбора порога 101 в зависимости от записанного во второй блок памяти 12 г двоичного числа R производит выбор определенного двоичного порогового числа Mr, которое с его выхода в параллельном коде подается на управляющий вход решающего узла 6.

Таким образом, в течении времени счета каждых Q циклов в решающий узел 6 подается определенное поровое число Mr, которое может принимать в каждом конкретном случае одно из l дискретных значений (градаций) в зависимости от качества приема кодовых комбинаций. Необходимое число градаций l порогового числа Mr выбирается из расчета поддержания вероятности ложного срабатывания устройства (ложного обнаружения синхронизма) в требуемых пределах при различных изменений величины РОРК.

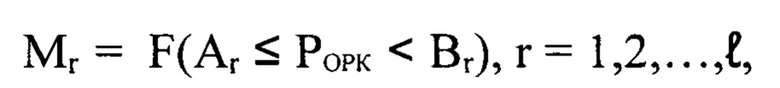

При этом закон формирования конкретных значений пороговых чисел Мг первым блоком 101 выбора порога символически можно записать в виде

де F - заранее выбранное правило для первого блока выбора порога 101, по которому величине РОРК ≈ R/Q, принимающей значение в пределах r-го интервала измерений, приводится в соответствие вполне определенное значение порогового числа Mr;

Ar и Br - соответственно нижняя и верхняя границы величины для РОРК r-го интервала.

Соответственно требуемая помехоустойчивость устройства которая определяется вероятностью ложного срабатывания, обеспечивается выбором закона формирования пороговых чисел Mr для первого блока выбора порога 101 по соответствующим измеренным значениям величины РОРК, попадающим в пределы какого-либо r-го интервала с границами Ar и Br, по принципу: чем больше величина РОРК, тем большим должно быть пороговое число Mr.

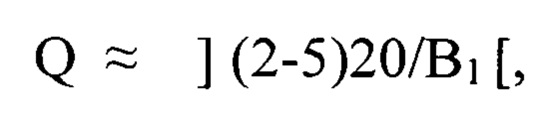

Величина Q, определяющая коэффициент счета счетчика 8 циклов, должна выбираться, с одной стороны, достаточно большой, для того, чтобы обеспечить требуемую точность оценки вероятности ошибки РОРК разрешенной кодовой комбинации, с другой стороны - достаточно малой, чтобы обеспечить измерение величины РОРК в пределах между двумя сбоями синхронизма кодовых комбинаций и слежение за изменениями условий связи. Если считать, что сбои синхронизма кодовых комбинаций происходят относительно редко, т.е. через интервалы времени, намного превышающие время счета Q цикловых импульсов (что имеет место на практике), то величина Q может быть выбрана в следующем виде [7]:

где B1 - верхняя граница величины РОРК в пределах первого интервала измерений, который соответствует наименьшему пороговому числу Mr;

][ - означает округление до целого числа.

Как было указано выше, поиск цикловой фазы или временной позиции синхронизма входного сигнала и корректировка цикловой фазы выходного сигнала устройства выходным сигналом синхронизации решающего узла 6 производится тогда, когда с выхода первого триггера 151 начинает поступать лог.1 на первый дополнительный управляющий вход решающего узла 6. Соответственно блокировка выходного сигнала синхронизации решающего узла 6 осуществляется при другом состоянии первого триггера 151, когда с его выхода поступает лог. 0, сигнализирующий установление синхронизма кодовых комбинаций.

Рассмотрим боле подробно установку логического уровня на выходе первого триггера 151 в каждое из двух состояний, определяющих режим работы устройства:

1) лог. 0 - установлен факт восстановления синхронизма кодовых комбинаций после корректирования фазы последовательности выходных импульсов формирователя цикловых импульсов 7 сигналом синхронизации решающего узла 6, после чего выход решающего узла 6 заблокирован;

2) лог. 1 - установлен факт сбоя синхронизма кодовых комбинаций, в результате выход решающего узла 6 разблокирован и производится поиск нового временного положения синхронизма.

Процесс установки первого триггера 151 в первое состояние (лог. 0) происходит следующим образом.

После завершения процесса поиска новой цикловой фазы сигнала или временного положения границ кодовых комбинаций и корректирования фазы выходных цикловых импульсов (фиг. 2, п), как отмечалось выше, устанавливается синхронное временное соотношение между последовательностью откликов на выходе опознавателя синхросигнала 1 на разрешенные кодовые комбинации (фиг. 2, о) и регулярно следующими цикловыми импульсами. При этом каждый отклик опознавателя синхросигнала 1 на разрешенную кодовую комбинацию должен совпадать во времени с соответствующим выходным импульсом формирователя цикловых импульсов 7 (фиг. 2, п) в каждом цикле на интервале длительностью 4τ.

При этом требуется определить достоверность восстановления синхронизма и заблокировать выход решающего узла с целью исключения его ложного срабатывания. Для этого последовательность одиночных символов 1 и 0 с выхода первого элемента «И» 31 подается на вход младшего разряда первого входа второго блока вычитания, а на вход младшего разряда второго входа блока вычитания подается другая последовательность одиночных символов 0 и 1 с выхода первого элемента запрета 21, на остальные разрядные входы первого и второго входов второго блока вычитания подаются символы 0 путем подключения их к источнику «нулевого» уровня. При этом на каждом из входов второго блока вычитания поступающие символы 1 или О совместно с остальными символами 0 на других разрядных входах образуют, как и на сигнальных входах первого и третьего накапливающих сумматоров, двоичное число «1» или двоичное число «О» в параллельном коде длительностью 4τ. Двоичное число «1» или «0» длительностью 4τ на первом входе второго блока вычитания является уменьшаемым, а двоичное число «О» или «1» длительностью 4τ на втором входе блока вычитания является вычитаемым, при этом на выходе второго блока вычитания будет появляться либо первый результат вычитания: «1» - «0»=«1» - плюс единица в параллельном двоичном коде, если соответствующая разрешенная кодовая комбинация не искажена, либо второй результат вычитания: «0» - «1»=- «1» - минус единица в параллельном двоичном коде, если соответствующая разрешенная кодовая комбинация искажена. Соответственно с момента появления импульсного сигнала синхронизации на выходе решающего узла вероятность появления на выходе первого элемента «И» одиночного символа 1 или двоичного числа «1» на сигнальном входе второго накапливающего сумматора 162, соответствующего не искаженной или правильно принятой разрешенной кодовой комбинации РПPK становится больше вероятности появления на выходе первого элемента запрета одиночного символа 1 или двоичного числа минус «1» на сигнальном входе этого сумматора 162, соответствующего искаженной или принятой с ошибками разрешенной кодовой комбинации РОРК при вероятности ошибки двоичного символа последовательности кодовых комбинаций Poc>0,5. При этом с помощью второго накапливающего сумматора производят суммирование одиночных положительных чисел «1», соответствующих количеству неискаженных разрешенных кодовых комбинаций, которые поступают на его сигнальных вход и вычитание из них суммы одиночных отрицательных чисел - минус «1», соответствующих количеству искаженных разрешенных кодовых комбинаций. С помощью первого накапливающего сумматора 161 производят суммирование одиночных положительных чисел «1», соответствующих количеству искаженных разрешенных кодовых комбинаций, которые поступают на его сигнальный вход. Результаты счета с выходов первого и второго накапливающих сумматоров (161, 162) подаются на первые входы третьего и четвертого блоков сравнения (113, 114) соответственно, на вторые входы которых подается пороговое число Wr с выхода второго блока выбора порога 102. При этом второй накапливающий сумматор 162 по сравнению с первым накапливающим сумматором 161 достигнет результата счета установленного порогового числа Wr первым, поскольку РПРК>РОРК, в результате первым сработает четвертый блок сравнения 114, перепад напряжения с выхода которого подается на вход второго формирователя импульса 172, выходной импульсный сигнал которого подается через второй вход второго элемента «ИЛИ» 92 на входы сброса первого и второго накапливающих сумматоров (161, 162), обнуляя их, и процесс счета искаженных и неискаженных разрешенных кодовых комбинаций повторяется.

Одновременно импульсный сигнал второго формирователя импульса 172, подается на второй вход первого триггера 151, устанавливая его в «нулевое» состояние, с выхода которого запрещающий «нулевой» уровень, подают на первый дополнительный управляющий вход решающего узла 6, блокируя выходной сигнал синхронизации и подтверждая тем самым достоверность восстановления синхронизма кодовых комбинаций.

Рассмотрим процесс обнаружения сбоя синхронизма. При сбое синхронизма кодовых комбинаций при любых условиях связи можно предположить, что n-символьные комбинации двоичной последовательности размещаются в n-разрядном регистре сдвига (фиг. 1) в момент поступления каждого ЦИ с выхода формирователя ЦИ 7 равновероятно. Тогда вероятность размещения ложной разрешенной кодовой комбинации в n-разрядном регистре сдвига в момент поступления ЦИ составляет величину Рлрк=No/N=2k/2n. Вероятность размещения в этом регистре сдвига любой другой (запрещенной) комбинации составляет Рзк=(N-No)/N=1-2k/2n. Очевидно, что РЗК- РЛРК, т.е. первый накапливающий сумматор 161 по сравнению с вторым накапливающим сумматором 162 достигнет результата счета установленного порогового числа Wr первым. При этом, чем больше информационных символов k содержится в одной разрешенной кодовой комбинации, т.е. чем меньше избыточность кода, определяемая как ry=1-k/n [1], тем за большее время (в цикловых интервалах, каждый длительностью Тц) можно с заданной степенью достоверности определять сбой синхронизма кодовых комбинаций, используя предложенный алгоритм сравнительного накопления откликов опознавателя синхросигнала 1 на ложные разрешенные и запрещенные кодовые комбинации до выбранного порогового числа Wr. Например, при использовании кода с минимальной избыточностью (n,n-1) при k=n-1 (код с проверкой на четность или нечетность), то вероятности РЛРК=2n-1/2n=1/2 и РЗК=1-РЛРК=1/2 раны, т.е. РЛРК=РЗК. Определить сбой синхронизма в этом случае практически невозможно без использования предложенного алгоритма сравнительного накопления откликов опознавателя синхросигнала 1 на выходах первого элемента запрета 21 и первого элемента «И» 31, преобразованных в одиночные двоичные числа для подсчета первым и вторым накапливающими сумматорами. В этом случае, учитывая равные вероятности появления импульсов на выходах первого элемента запрета 21 и первого элемента «И» 31, в среднем, результат алгебраического сложения положительных и отрицательных одиночных двоичных чисел «1» и минус «1» вторым накапливающим сумматором 162 будет около нуля за выбранный интервал времени. При этом математическое ожидание числа ЦИ, которые требуется затратить для того, чтобы результат накопления откликов на запрещенные кодовые комбинации в виде одиночных двоичных чисел «1», подсчитываемым первым накапливающим сумматором 161 достиг порогового числа Wr, будет равно М=Wr/Рзк=2Wr [8]. При увеличении избыточности кода путем уменьшения количества информационных символов (k<n-1) в разрешенной кодовой комбинации, возрастает вероятность Рзк>РЛРК при сбоях синхронизма. Соответственно, будет уменьшаться вышеприведенная величина М<2 Wr, т.е. первый накапливающий сумматор 161 при каждой конкретной величие Рж ≥ Рлрк первым достигнет результата счета установленного порогового числа Wr при любой избыточности кода. В результате первым сработает третий блок сравнения 113, перепад напряжения с выхода которого подается на вход первого формирователя импульса 171, выходной импульсный сигнал которого подается на через первый вход второго элемента «ИЛИ» 92 на входы сброса первого и второго накапливающих сумматоров 161, 162, обнуляя их, и процесс подсчета соответствующих кодовых комбинаций повторяется. Одновременно импульсный сигнал первого формирователя импульса 171 подается на первый вход первого триггера 151, устанавливая его в «единичное» состояние, с выхода которого разрешающий «единичный» уровень (лог. 1) подается на первый дополнительный управляющий вход решающего узла 6, снимая блокировку импульсного сигнала синхронизации на выходе решающего узла 6. Кроме того импульсный сигнал первого формирователя импульсов 171 подается через второй вход первого элемента «ИЛИ» 91 на входы сброса, блока регистров сдвига 5 и первого блока памяти 121 решающего узла 6, обнуляя их, после этого начинают поиск нового временного положения позиции синхронизма.

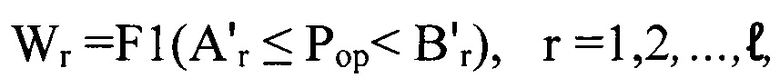

Закон формирования конкретных значений пороговых чисел Wr вторым блоком выбора порога 102, как и для первого блока выбора порога 101 символически можно записать в виде

где F1 - заранее выбранное правило для второго блока выбора порога 102, по которому величине РОРК ≈ R /Q, принимающей значения в пределах r-го интервала измерений, приводится в соответствии вполне определенное значение порогового числа Wr;

А'r и В'r - соответственно нижняя и верхняя границы величины РOPK для r-го интервала.

Соответственно требуемое быстродействие устройства при установлении факта сбоя синхронизма и достоверного установления факта восстановления синхронизма, обеспечивается выбором закона формирования пороговых чисел Wr для второго блока выбора порога 102 по соответствующим измеренным значениям величины РОРК, попадающим в пределы какого-либо г-го интервала с границами А'r и В'r, по принципу: чем больше величина РОРК, тем большим должно быть пороговое число Wr.

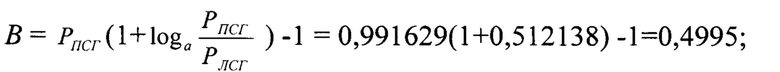

Рассмотрим эффективность предлагаемого устройства путем сравнения его с известным устройством - прототипом, при работе сравниваемых устройств в равных условиях. В [4] приведены результаты моделирования работы устройства - прототипа, исходные данные и полученные характеристики которого следующие:

- количество двоичных символов в одном цикле, содержащем синхрогруппу из m=9 синхросимволов (000111011) составляет N=1200;

- длительность одного цикла или циклового интервала (ЦИ) Тц=2,5 мс;

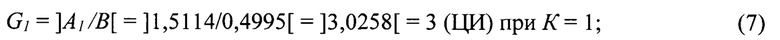

- время восстановления синхронизма ТВС = 14,7 мс или количество ЦИ, требуемых для восстановления синхронизма GBC=14,7 мс/2,5 мс=6 ЦИ;

- вероятность ложного установления синхронизма РЛС=2,5⋅10-3;

- вероятность ошибки двоичного символа Рош = 5⋅10-2.

Предположим, что основная информация передается равномерным корректирующим кодом (9,5), и требуется обеспечить синхронизацию кодовых комбинаций при приеме информации. Для выполнения этой задачи, с использованием прототипа [4], на передающей стороне в исходный передаваемый сигнал, представляющий собой последовательность 9-символьных кодовых комбинаций кода (9,5), требуется ввести цикловой 9-символьный (m=n) цикловой синхросигнал (периодически повторяемую среди 9-символьных информационных кодовых комбинаций синхрогруппу (000111011) с соответствующим увеличением скорости передачи двоичной последовательности. При этом передаваемый сигнал, используемый для сравнения параметров прототипа и предлагаемого устройства, должен максимально соответствовать передаваемому сигналу, приведенному выше.

Поскольку длина цикла двоичной последовательности, содержащей цикловой синхросигнал, должна составлять N=1200 двоичных символов, то количество 9-символьных комбинаций, содержащихся в одном цикле (одной 9-символьной синхрогруппы и (L-I) 9-символьных информационных кодовых комбинаций), составляет величину L=N/m=1200/9=133,333≈133 ЦИ (или 9-символьных комбинаций). В данном случае каждый цикл или ЦИ должен состоять из 9-символьной синхрогруппы (111000011) и 132-х 9-символьных разрешенных информационных кодовых комбинаций При этом длина цикла передаваемого сигнала N'=m⋅133=9⋅133=1197 (двоичных символов), что примерно равно N=1200 (двоичных символов). При вероятности ошибки двоичного символа Рош = 5⋅10-2 такая структура испытательного сигнала с достаточной степенью точности соответствует двоичному сигналу, использованному при моделировании работы прототипа [4].

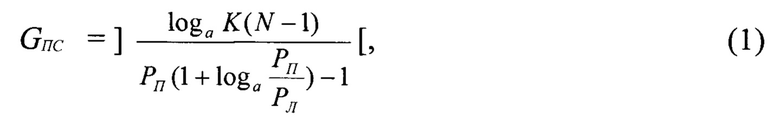

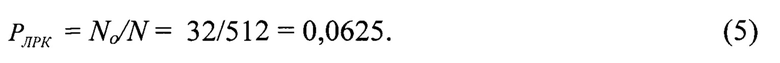

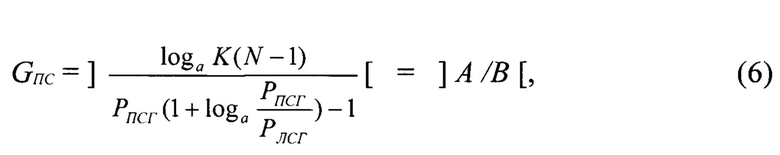

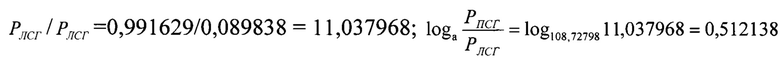

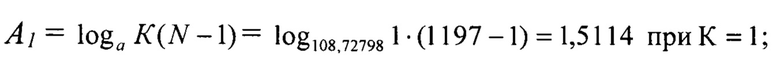

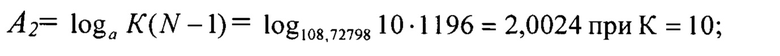

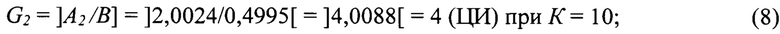

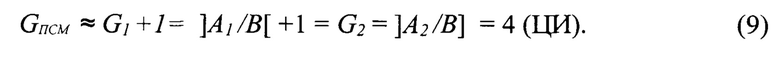

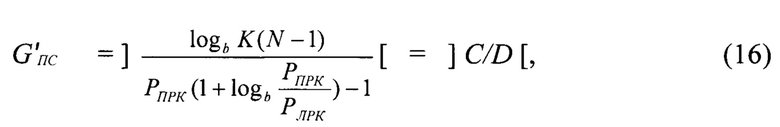

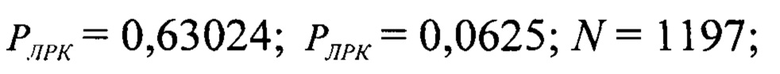

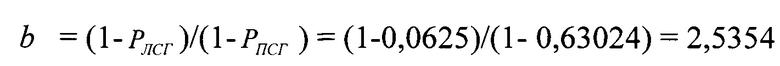

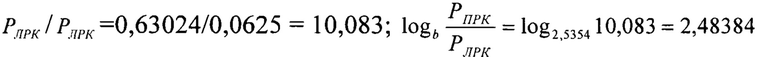

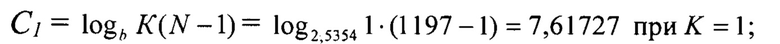

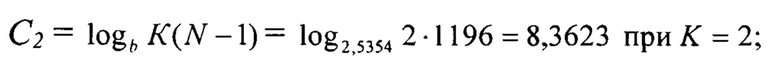

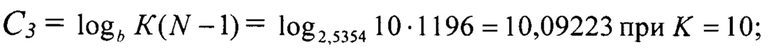

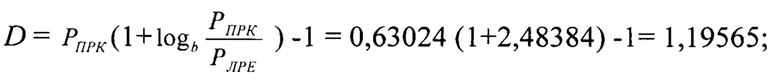

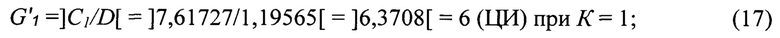

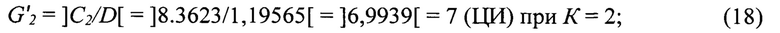

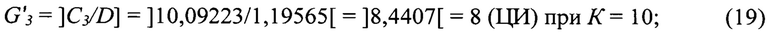

Проведем сравнение полученных в [4] результатов моделирования работы прототипа, например, по времени восстановления синхронизма Твс=14,5 мс=6 ЦИ с результатами, которые можно получить теоретически. В работе [5] на основе критерия максимума апостериорной вероятности получено аналитическое выражение, описывающее оптимальный алгоритм поиска временного положения позиции синхронизма (цикловой фазы) односимвольного циклового синхросигнала (ЦС) в составе потока информационных двоичных символов с параллельным анализом всех позиций цикла. При этом время поиска позиции синхронизма GПС (в ЦИ) или длительность интервала анализа, в конце которого следует производиться выбор искомой позиции цикла с вероятностью правильного выбора, определяемой величиной К, можно определить из соотношения [5]:

где символ] [означает округление до ближайшего целого числа;

K - отношение апостериорных вероятностей истинности альтернативных гипотез H1 и Н2, где гипотеза H1 означает, что анализируемая i-ая позиция цикла соответствует фазе ЦС;

N - число позиций (двоичных символов) в цикле;

РП - вероятность правильного приема одиночного синхросимвола (РП>0,5);

РЛ - вероятность появления информационного символа, аналогичного синхросимволу (ложный синхросимвол) на любой из N-1 информационных позиций ЦИ, в большинстве случаев можно считать, что РЛ ≈ 0,5;

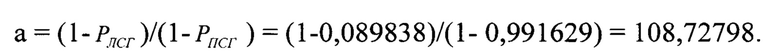

а=(1-РЛ)/(1-РП).

Следует отметить, что все опознаватели синхросигнала имеют одинаковые для всех функциональные элементы, такие, как входной поразрядный регистр сдвига, m элементов равнозначности, регистра хранения, элемента «И» например, как приведено на фиг. 1. Соответственно и выходные сигналы различных опознавателей синхросигнала, в том числе и предлагаемого устройства и прототипа, представляют собой двоичные последовательности откликов (символов) с односимвольным цикловым синхросигналом (периодически повторяемый среди других символов (откликов) «единичный» синхросимвол). В этой последовательности каждый синхросимвол, располагаемый на временной позиции синхронизма, представляет собой отклик опознавателя синхросигнала на синхрогруппу (разрешенную кодовую комбинацию) из m=n синхросимволов (информационных символов) с соответствующей вероятностью правильного приема синхрогруппы (разрешенной кодовой комбинации). Любой другой символ, последовательности откликов, временное положение позиции которого в цикле не соответствует позиции синхронизма, представляет собой отклик опознавателя синхросигнала на ложную синхрогруппу из m=n символов с соответствующей вероятностью обнаружения ложной синхрогруппы.

Поэтому выражение (1) справедливо и для определения времени поиска GПС (в ЦИ) позиции синхронизма в двоичной последовательности на выходе соответствующего опознавателя синхросигнала как для прототипа, так и для предлагаемого устройства. Для выходных сигналов опознавателей синхросигналов этих устройств вероятность появления отклика на синхрогруппу или разрешенную кодовую комбинацию должна определяться как вероятность правильного приема синхрогруппы из m синхросимволов РПСГ с учетом коррекции искаженных синхросимволов или вероятность правильного приема разрешенной m-символьной кодовой комбинации РПРК. Соответственно в выражении (1) следует провести замену вероятности правильного приема одиночного синхросимвола Рп на РПСГ или..РПРК для расчета величины GПС для прототипа и для предлагаемого устройства соответственно. Для определения GПС предлагаемого устройства вероятность правильного приема разрешенной m-символьной кодовой комбинации равна

Здесь не учитывается некоторое увеличение вероятности РПРК за счет возможного появления в регистре сдвига 22 в синхронном состоянии какой либо искаженной разрешенной кодовой комбинации, полностью совпадающей с одной из разрешенных комбинаций, записанных в блок памяти 23 (фиг. 1), т.е. не учитывается трансформация одной разрешенной кодовой комбинации под действием помех в другую разрешенную кодовую комбинацию. Это упрощение заведомо незначительно ухудшает расчетные характеристики предлагаемого устройства при сравнении его с прототипом.

Однако в прототипе предусмотрено корректирование ошибочно принятых синхросимволов в каждой синхрогруппе из 9-ти синхросимволов. В [10] не указано количество корректируемых ошибочных синхросимволов в синхрогруппе ООО 111011 при вероятности ошибки двоичного символа Рош=5⋅10-2, поэтому примем максимально возможное число 2 (символа) для 9-символьной синрхрогруппы, т.е. возможно корректировать от 1-го до 2-х синхросимволов в синхрогруппе и в ложной синхрогруппе. Отклик на синхрогруппу может появиться на выходе опознавателя синхросигнала, например, в 1-ом тактовом интервале каждого цикла с определенной вероятностью на 9-символьную комбинацию с учетом возможной коррекции от 1 до 2 синхросимволов, в следующих случаях:

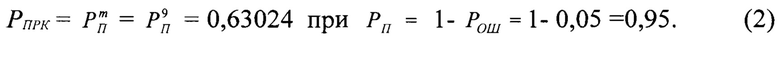

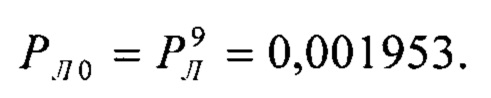

1. Когда 9 синхросимволов синхрогруппы, находящихся в опознавателе синхросигнала (9-разрядном регистре сдвига) совпадают с соответствующими 9 синхросимволами сравниваемой синхрогруппы (000111011) опознавателя синхросигнала (9-разрядного регистра хранения), при этом ошибок нет и коррекция ошибочных символов не производится. Вероятность такого события РПО=Р9П=0,630249.

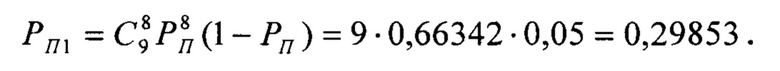

2. Когда из 9 синхросимволов синхрогруппы, находящихся в опознавателе синхросигнала совпадают с соответствующими 8-ми синхросимволами сравниваемой синхрогруппы, а один ошибочный символ подлежит коррекции. Вероятность такого события

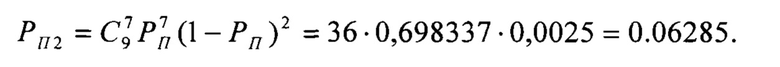

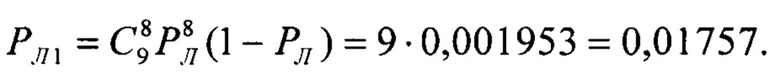

3. Когда из 9 синхросимволов синхрогруппы, находящихся в опознавателе синхросигнала совпадают с соответствующими 7-ми синхросимволами сравниваемой синхрогруппы, а два ошибочных символа подлежит коррекции. Вероятность такого события

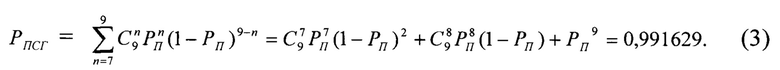

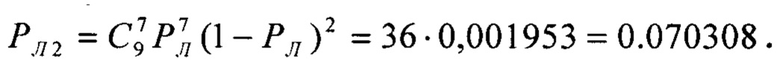

Вероятность правильного обнаружения синхрогруппы с учетом возможной коррекции от 1-го до 2-х ошибочно принятых синхросимволов в одной синхрогруппе будет равна

При каждом сдвиге входного сигнала в регистре сдвига опознавателя синхросигнала относительно синхронного состояния, в разрядах регистра сдвига как прототипа, так и предлагаемого устройства будет размещаться с большой вероятностью случайный набор символов 1 и 0. Максимально возможное число 9-символьных комбинаций, каждая из которых может размещаться в 9-разрядном регистре сдвига равно Nобщ=29=512. Вероятность появления на выходе опознавателя синхросигнала прототипа ложного отклика на ложную синхрогруппу равна РЛСГ=1/Nобщ=1/512=0,0019531. Однако, с учетом коррекции до 2-х символов в 9-символьной комбинации, ложный отклик может появиться в любом тактовом интервале на одну из случайных 9-символьной комбинации, располагаемой в j-ом ТИ в 9-разрядном регистре сдвига опознавателя синхросигнала в следующих случаях:

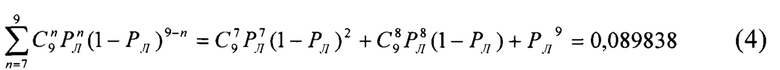

1. Когда в 9-разрядном регистре сдвига в j-ом ТИ располагается 9-символьная комбинация, 9 символов которых совпадают с соответствующими 9 синхросимволами синхрогруппы (000111011) с выходов регистра хранения, коррекция «ошибочных» символов не производится. Вероятность такого события

2. Когда в 9-разрядном регистре сдвига в j-ом ТИ располагается 9-символьная комбинация, 8 символов которых совпадают с 8 из 9 синхросимволов синхрогруппы с выходов регистра хранения, а один «ошибочный» символ подлежит ложной коррекции. Вероятность такого события

3. Когда в 9-разрядном регистре сдвига в j-ом ТИ располагается 9-символьная комбинация, 7 символов которых совпадают с 7 из 9 синхросимволов синхрогруппы регистра хранения, а два «ошибочных» символа подлежит ложной коррекции. Вероятность такого события  регистра хранения

регистра хранения

Вероятность ложного обнаружения ложной синхрогруппы с учетом возможной коррекции от 1 -го до 2-х ложных ошибочных синхросимволов в одной ложной синхрогруппе будет равна РЛСГ=