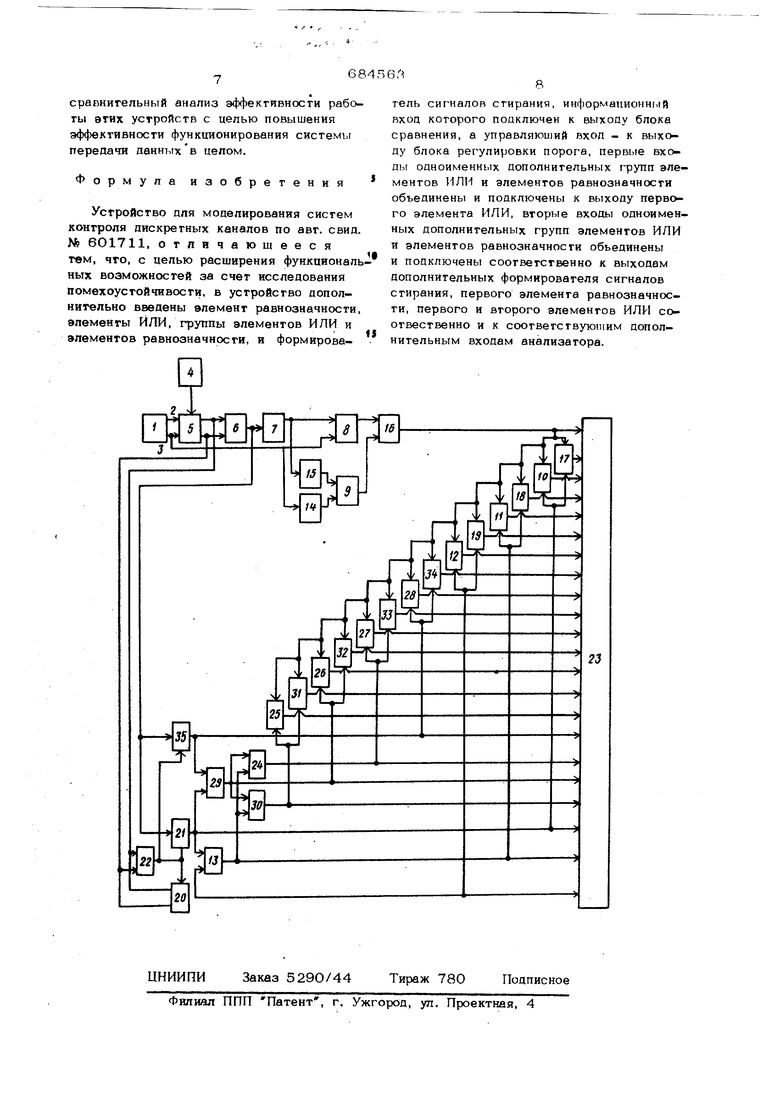

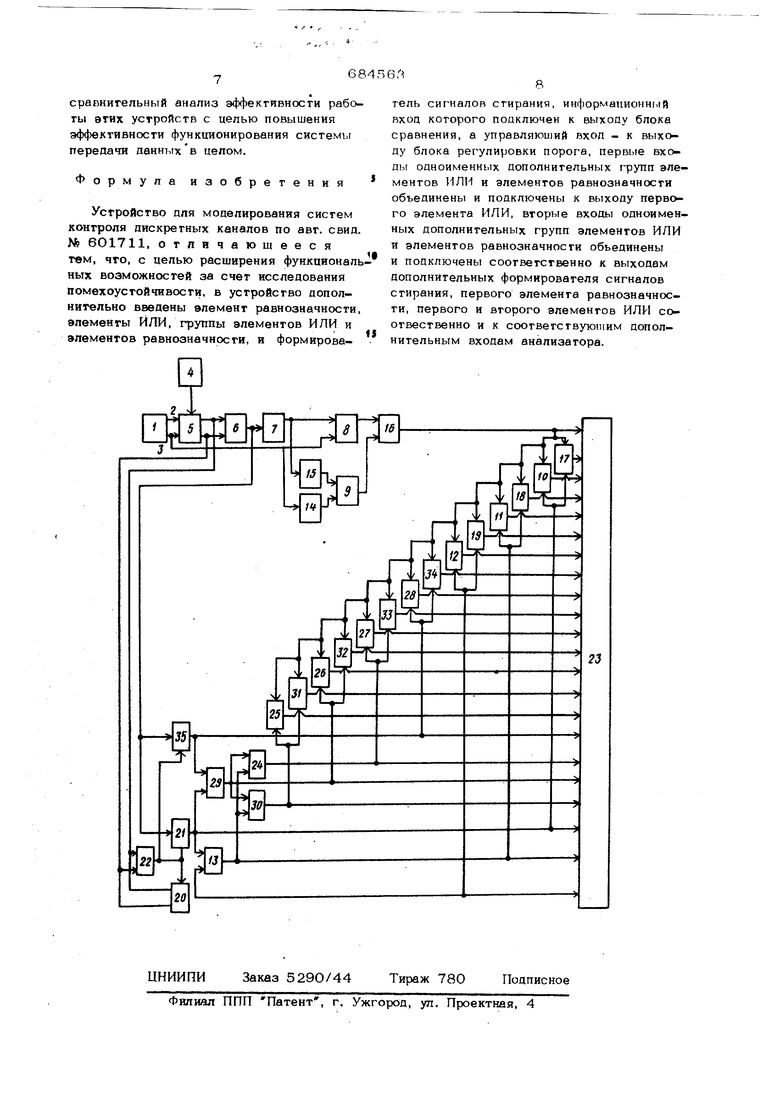

.{54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМ КОНТРОЛЯ ДИСКРЕТНЫХ КАНАЛОВ поп 5, блок сравнения G, пороговый эпемент 7, элементтл равнозначности 8-13, ин }ергоры 14, 15, эпемент г ИЛИ 16-К формиропагели сигналов стирания 20, 21 блок регулировки порога 22, анапизатор 23, пополннтепьный элемент равнозначно ти 24, аополнительн1,те группы элементов равнозначности 25-28, дополнительные элементы ИЛИ 20, 30, пополнительные группы элементов ИЛИ 31-34 и дополни тельный формиропагель сигналов стирания 35. Устройство работает следующим образом. При включении устройства (на черт, цепь включения не показана) датчик исхо ных сообщений 1 случайным образом формирует на выходах 2 и 3 сигналы (последовательность 1 и О). С выхода 2 (моделируемая 1) сигнал поступает на управляющий вход блока преобразования случайных сигналов 5, на информационный вход которого подается сигнал с выхода датчика случайных сигналов 4. При выработке О датчиком 1 сигнал с выхода 3 поступает на другой управляющий вход блока преобразования случайных сигналов 5, на входе элемента равнозначности 8 и инвертора 14. При появлении например, сигнала на выходе 2 по этому сигналу блок 5 форми рует случайные сигналы (моделируются сигналы на выходах, например, интеграто ров корреляционного приемника дискрет ных сигналов). . Эти сигналы с выходов блока 5 поступают на соответствующие входы блока регулировки порога 22, формирователя сигналов стирания 20 и на входы блока сравнения 6. Сигнал, соогветствуюишй разности случайных сигналов на выходах, блока 5, поступает на входы порогового элемента 7 и формировате лей сигналов стирания 21 и 35. Если величина сигнала с выхода блоха сравнения 6 больше вепичины порога срабатыва ния элемента 7, то на его единичном выходе появляется сигнал, который поступает на входы ингзертора 15 и элемента равнозначности 8. Таким образом, на выходе элемента равнозначности 8 сигнал будет только в том случае, если имеется сигнал на выходе 3 датчика .1 и разность между сиг налами на выходах блока 5 больше некоторой величинь 1 (величины порога срабатрлвания порогового элемента). Это соответствует случак, когда, например, при передаче О по пнскретному каналу получают 1, т. е. моделируются случаи трансформации О р 1. Ма выходе элек)ента равнозначности : сигнал появляется только в том случае если сигнал на выходе 3 датчика 1 отсутствует (т. е. имеется сигнал на вы ходе 2) и разность между сигналами на В1;1ходах блока 5 много меньше порога срабатывания элемента 7. Это соответствует случаю, когда,например, при передаче, по дискретному каналу получили О, т. е. моделируются случаи трансформации l.Q. Сигналы с выходов элементов равнозначности 8 и 9 через элемент ИЛИ 16 поступают на вход анализатора 23 например, в один и его счетчиков, подсчитывающий ошибки, (на чертеже не показан) и на входы элементов равнознач™ ности 10-12 элементов ИЛИ и элементов равнозначности 25-28 элементов ИЛИ 31-34. Таким образом, на выходе элементов ИЛИ 16 сигнал появляется при выполнении следующих условий: .)u jy|-o A(,-,)u,(0 где ,, - сигналы на выходах блока 5; д знак логического умножения; V - знак логического сложения; и - порог срабатывания. Если величины случайных сигналов, подаваемых с выходов блока 5 на информационные входы блока 20, одновремекно больше или меньше, порогового сигнала, подаваемого с выхода блока 22 на jTipaa-. ляюший вход формирователя сигналов стирания 2О, т. е. если выполняете я, например, условие fe-,i))Hfe-.).t2 рде (J, - порог срабатывания, то на выхо де формирователя 20 появляется сигнал, который поступает на вход элемента равнозначности 13, на вход анализатора 23, например, в его счетчик сигналов стирания, подсчитывающий число событий, соот ветсгвуюших выполнению условия (2), и на входы элементов 12, 1. На выходе формирователя сигналов с тирания 21 сигнал появляется в том случае,, если выполняется например, условие (... где Uj.- порог срабатывания. Сигналы с выхода формирователя 21 поступают на элемент равнозначности 13, элемент ИЛИ 29, на вход анализатора 23,например, в один из его счетчиков. подсчитывающий число событий, соответсгвуюших п лполнению условия (з) и на входы элементов Ю и 17. На выходе элемента равнозначности 13 сигнал поя утяется в том случае, если имеются опновроменно сигналы на формирователей 20 и 21, т. е. когда выполняется условие )4ft.U );(4 Сигнал с выхода элемента равнозначности 13 nocTviiaeT в анализатор, например, в один из его счетчиков, подсчитывающий число событий, соответствующих выполнению условия (4), и на входы элементов 11, 18, 24 и 30. На выходе формирователя сигналов ст рания 35. сигнал появляется в том случае, если в 1пол} яется, например условие . где Uj - порог срабатывания. Сигналы с выхода формирователя 35 поступают на эцементы ИЛИ 20 и 34 на элемент равнозначности 28 и на вход ан ли затора 23, например, в один из его счетчиков, подсчитывающий число событи соответствующих выполнению условия (5) На выходе элемента ИЛИ 29 сигнал появляется в том случае, когда выполняется, условие, , ,, , (/«г.)Ч(.К) выходе элемента ИЛИ 30 сигнал появляется в том случае, когда ВР ШОЛНЯется условие ()Wfei (2U,)V1(.|4 выходе элемента равнозначности 24 сигнал появляется в то( случае, когда выполняется условие WSг..2) )U.) (8) Сигналы с выходов этих элементов поступают на соответствующие входы анализатора, например,..в соответствующие счетчики, подсчитывающие число событий, соответствующих выполнению условий (6), (7), (8). На вы ходе элемента равнозначности 12 появляются сигналы в тех случаях, когда одновременно им ются сигналы на выходах элементов 16 и 2 т.е. моделируются события, соответствуюшие одновременному выполнению условия (2) и появлению нщибки. На выходе равнозначности 11 появляются сиг-нал1 г в тех случаях. когда одновременно имеются сигналы на выходах элементов 16 и 13, т. е. моделируются события, соответствующие одновременному появлению ошибки и выполнению условия (4). На выходе элемента v- внозначности 10 появляются сигналы в тех случаях, когда одновременно имеются сигналы на выходах элементов 16 и 21, т. е. моделируются события, соответствующие одновременному появлению ошибки и выполнению условия (з). На выходе элемента равнозначности 25сигнал появляется в тех случаях, когда одновременно имеются сигналы на выходах элементов 16 и 30, т. е. моделируются события, соответствующие одновременному появлению ошибки и выполнению условия (7). На выходе элемента равнозначности 26сигнал появляется в тех случаях, KOI да одновременно имеются сигналы на выходах элементов 16 и 29, т. е. моделируются события, соответствующие одновременному появлению ошибки и выполнению условия (б). На выходе элемента равнозначности 27сигнал появляется в тех случаях, когда одновременно имеются сигналы на вы- . ходах элементов 16 и 24, т. е. моделируются события, соответствующие одновременному появлению ошибки и выполнению условия (в). . На выходах элементов ИЛИ 17-If), и 31-34 появляются сигналы в тех случаях, если хотя бы на одном из их входов появляется сигнал, т. е. моделируются события, заключающиеся в появлении или ошибки, или соответствующего сигнала стирания,или их одновременного появления. С выходов элементов 10-12, 17-10, 25-27, 28 и 31-34 сигналы поступают на соответствующие входы анализатора (.например, в соответствующие счетчики). Анализатор 23 обрабатывает результаты моделирования, например, содержимое счетчиков, полученное за определенный отрезок времени моделирования (например, за время анализа разрядов информации случайной последовательности с Bt.ixoua датчика l). Применение данного устройства позволяет исследовать качество работы более широкого класса систем контроля дискретных каналов при более (иироких принципах их построения, работу этих систем при различных параметрах схем и произвоцить

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем контроля дискретных каналов | 1976 |

|

SU601711A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1987 |

|

SU1559415A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Устройство для определения вероятностных характеристик фазы случайного процесса | 1985 |

|

SU1300510A2 |

| Устройство для измерения дисперсии | 1988 |

|

SU1635197A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для приема информации с подавлением помех | 1981 |

|

SU966928A2 |

| Устройство для определения распределений вероятностей параметров импульсных сигналов | 1985 |

|

SU1416972A1 |

| Статистический анализатор | 1977 |

|

SU693398A1 |

Авторы

Даты

1979-09-05—Публикация

1976-12-27—Подача