(54) МНОЖИТЕЛЬНО-ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО ШАГОВОГО ТИПА | 1972 |

|

SU432528A1 |

| ВРЕМЯ- ИМПУЛЬСНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU253449A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| Время-импульсное множительноеуСТРОйСТВО | 1979 |

|

SU805344A1 |

| Времяимпульсное множительное устройство | 1988 |

|

SU1642481A1 |

| Электронный счетчик электроэнергии | 1979 |

|

SU866491A1 |

| Время-импульсное множительно-делительное устройство | 1982 |

|

SU1032459A1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU868783A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU432527A1 |

| ЗНАКОЧУВСТВИТЕЛЬНОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1965 |

|

SU173024A1 |

Предлагаемое изобретение относится к области вычислителы-юй техники и может быть использовано в устройствах обработки информации.

Известны интегрирующие устройства, выполненные на четырех ключах, соединенных по мостовой схеме; в первую диагональ которой включен интегрирующийконденсатор и во вторую диагональ включен управляемый 1енератор тока ij,

Недостаток этих устройств состоит в том, что они предназначены для интегрирования сигналов, что сужает их функциональные возможности.

Известно множительно-.штегрируюшее

устройство, содержащее блок интегрирования, выполненный на четырех ключах, соединен ных по мостовой схеме, в первую, диагональ которой включен интегрирующий конденсатор, а во вторую диагональ включен упра влпемый генератор тока, триггер, широтяо-импульсный модулятор, пятый ключ, бло сравнения, к управляющему входу управляемого генератора тока подключен источник сигнала первого солшож;ителя, выходы

триггера соединены с управляющими входаMii четырех ключей блока интегрирования, а счетный вход триггера соединен с выходом блока сравнения, первый вход которого соединен с источником опорного напряжения, а второй вход соединен с выходом управляемого генератора тока, источник сигнала второго сомножителя соединен со входом широтно-импульсного модулятора, выход которого соединен с управляющим входом пятого ключа, потенциальный вход которого соединен с источником питающего напряжения 2,

Недостаток этого устройства заключаетс в низкой помехоустойчивости.

Цель изобретения - повышение помехоустойчивости.

Зто достигается тем, что в предлагаемом устройстве выход пятого ключа соединен со вторым входом блока сравнения.

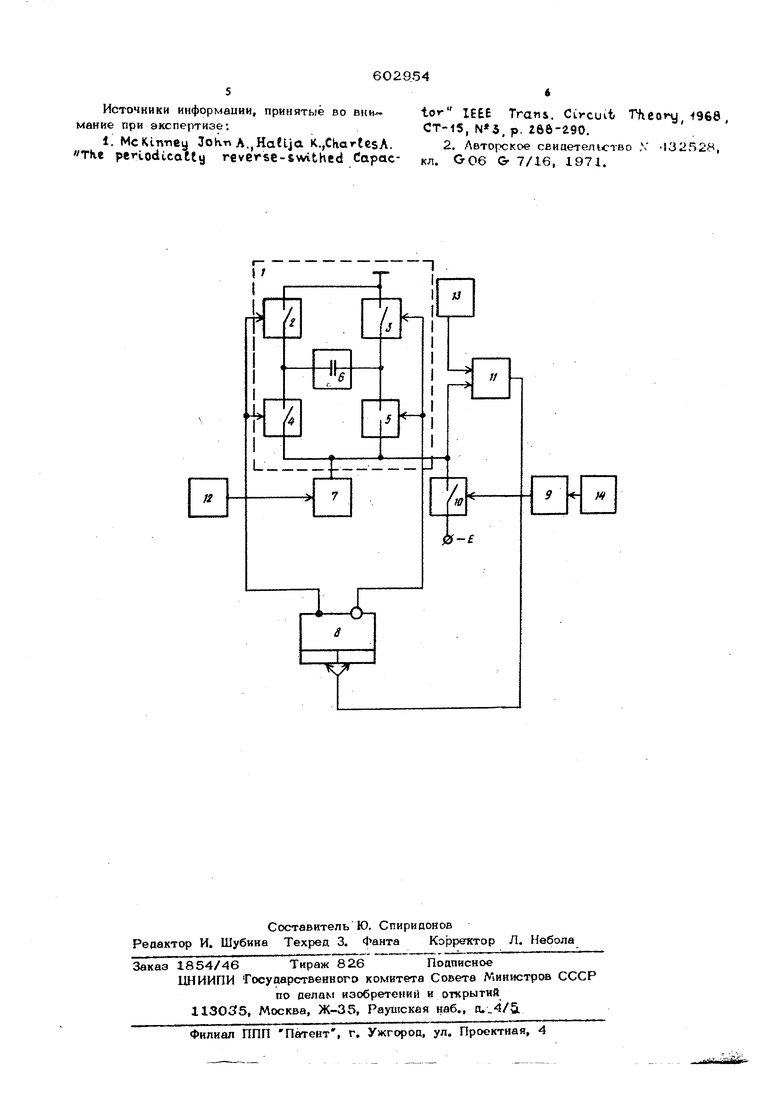

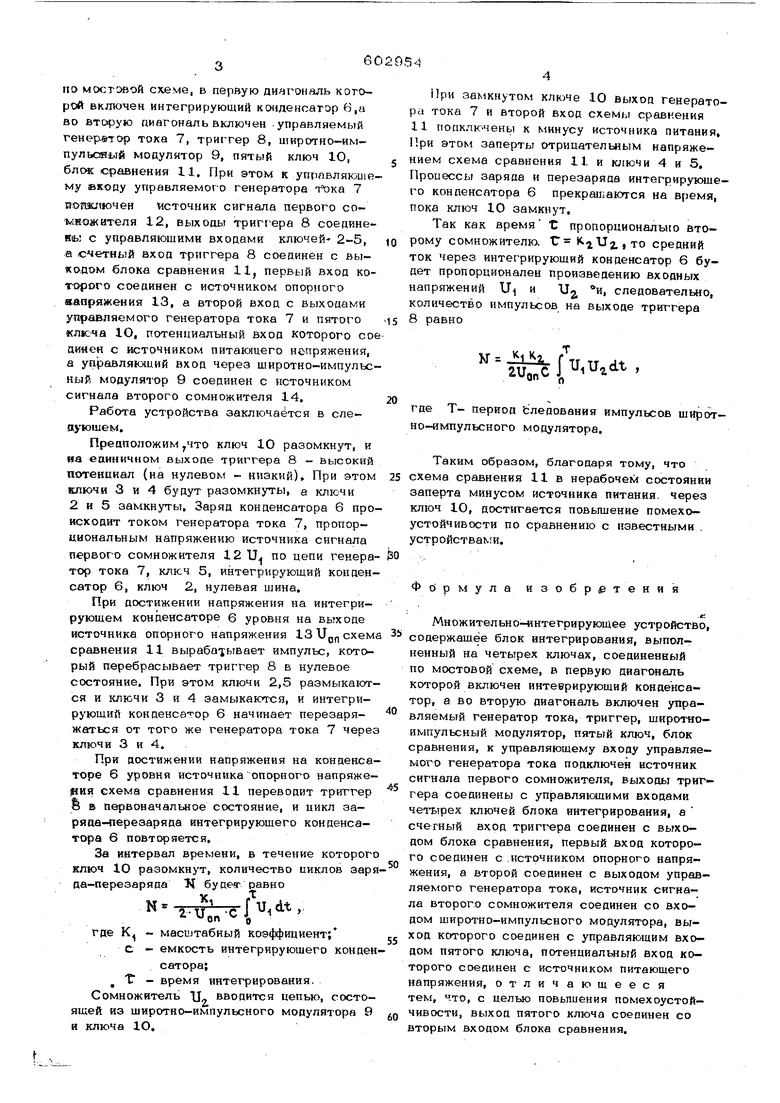

На чертеже приведена блок-схема предлагаемого устройства,

Множительно-интегрируюшее устройство содержит блок интегрирования 1, выполненнь й на четырех ключах , соединенных no мсх;товой схеме, в первую диагональ которой включен интегрирующий конденсатор 6,а во вторую пиагональ включен .управляемый генервтор тока 7, триггер 8, широтно-импульсзяый модулятор 9, пятый ключ 1О, блеж сравнения 11. При этом к управляющему вкоду управляемого генератора тЪка 7 иойзключен Источник сигнала первого сомножителя 12, выходы трипера 8 соедине в1ь; с управляющими входами ключей- 2-5, а счетный вход триггера 8 соединен с выходом блока сравнения 11, первый вход которого соединен с источником опорного запряжения 13, а второй вход с выходами управляемого генератора тока 7 и пятого клкча Ю, потенциальный вход которого сое дийен с источником питающего нспряжения, а уп1равляющий вход через широтно-импульс ный модулятор 9 соединен с источником сигнала второго сомножителя 14. Работа устройства заключается в слея тошем. Предположим что ключ Ю разомкнут, и на еаиничном выходе триггера 8 - высокий потенциал (на нулевом - низкий). При этом 25 ключи 3 и 4 будут разомкнуты, а ключи 2 и 5 замкнуты. Заряд конденсатора 6 проискоднт током генератора тока 7, пропорциональным напряжению источника сигнала первого сомножителя 12 Uj по цепи генера- 00 тор тока 7, ключ 5, интегрирующий конденсатор 6, ключ 2, нулевая шина. При достижении напряжения на интегрирующем конденсаторе 6 уровня на выходе

13 Upn схема Зь источника опорного напряжения сравнения 11 вырабатывает импульс, который перебрасывает триггер 8 в нулевое состояние. При этом ключи 2,5 размыкаются и ключи 3 и 4 замыкаются, и интегрирующий конденсатор 6 начинает перезаря- жаться от того же генератора тока 7 через ключи 3 и 4. При достижении напряжения на конденсаторе 6 уровня источника опорного напряже|ния схема сравнения 11 переводит триггер fe в первоначальное состояние, и цикл заряда-перезаряда интегрирующего конденсатора 6 повторяется. За интервал времени, в течение которого ключ 10 разомкнут, количество циклов заря да-перезаряда Л будея- равно H--nit(4dt,: где К - масштабный коэффициент; С - емкость интегрирующего конден сатора; Т - время интегрирования, Сомножитель Ц вводится цепью, состоящей из широтно-импульсного модулятора 9 и ключа 1О,

Множительно-«нтегрирующее устройство, содержащее блок интегрирования, выполненный на четырех ключах, соединенный по мостовой схеме, в первую диагональ которой включен интеврирующий конденсатор, а во вторую диагональ включен управляемый генератор тока, триггер, щиротноимпульсный модулятор, пятый ключ, блок При замкнутом ключе 10 выход генератора тока 7 и второй вход схемы сравнения 11 попклк.чены к минусу источника питания. При этом заперты отрицательным напряжением схема сравнения 11 и ключи 4 и 5, Процессы заряда и перезаряда интегрирующего конденсатора 6 прекршпаются на время, пока ключ 10 замкнут. Так как время t пропорционально второму сомножителю, Т ., то средний ток через интегрирующий конденсатор 6 будет пропорционален произведению входных напряжений U и TJj, X следователшо, количество импульсов на выходе триггера 8 равно %Ju,, где Т- период Следования импульсов шйротно-импульсного модулятора. Таким образом, благодаря тому, что схема сравнения 11 в нерабочем состоянии заперта минусом источника питания, через ключ Ю, достигается повьпиение помехоустойчивости по сравнению с известными . устройствами, Формула изобретения сравнения, к управляющему входу управляемого генератора тока подключен источник сигнала первого сомножителя, выходы триггера соединены с управляющими входами четырех ключей блока интегрирования, а счетный вход триггера соединен с выходом блока сравнения, первый вход которого соединен с .источником опорного напряжения, а второй соединен с выходом управляемого генератора тока, источник сигнала второго сомножителя соединен со входом широтно-импульсного модулятора, выход которого соединен с управляющим входом пятого ключа, потенциалшый вход которого соединен с источником питающего напряжения, отличающееся тем. Что, с целью повьшения помехоустой- чивости, выход пятого ключа соединен со вторым входом блока сравнения.

Источники информации, принятые во вни мание при экспертизе:

±. МсМппеу John A.,Hatlja K.,CKartesA. «Ttie pertodicatty reveyse-swithed Capactor Trans. Circuit 968, CT-15, , p. 266-290.

Авторы

Даты

1978-04-15—Публикация

1976-03-04—Подача