(54) ПРЕОБРАЗОВАТЕЛЬ КОДА ВО ВРЕМЕННОЙ ИНТЕРВАЛ

грубого преобразования, содержащего последовательно соединенные счетчик, дешифратор нуля и элемент совпадения, введены дополнительные временные селекторы и триггеры по числу выходов формирователя сдвинутых импульсов и устройства переключения, содержащее последовательно соединенные регистр, дешифратор, логический узел и элемен ИЛИ. При этом дополнительные гременнь1е селекторы соединяют выходы формирователя сдвинутых импульсов со вторыми входами логического узла устройства переключения, его схемы ИЛИ выходами соединены с единичными входами дополнительных триггеров, единичные выходь которых соединены со вторыми входс1ми основных временных селекторов, нулевМе входы - с выходом преобразователя, а вторые входы дополнительных временны} селекторов через формирователь импульсов - со входом запуска преобразователя .

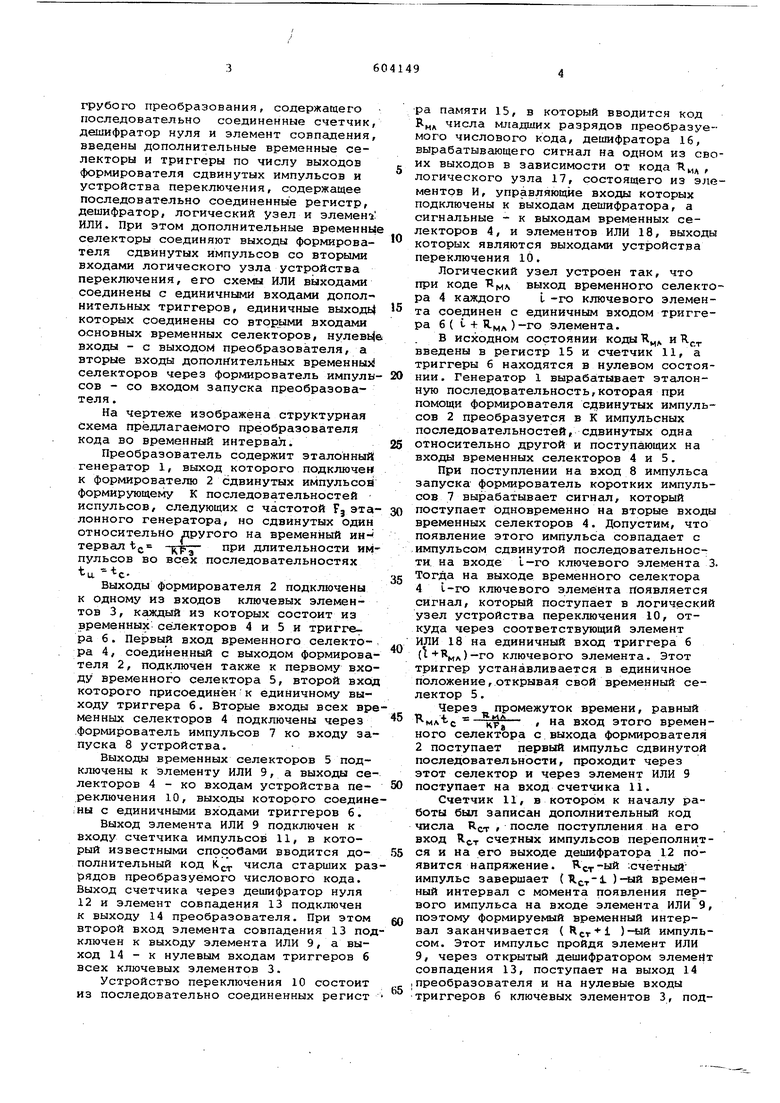

На чертеже изображена структурная Схема предлагаемого преобразователя кода во временный интервал.

Преобразователь содержит эталонный генератор 1, выход которого подключен; к формирователю 2 сдвинутых импульсов формирующему К последовательностей испульсов, следующих с частотой Fj эталонного генератора, но сдвинутых один относительно другого на временный иНтepвaлt, при длительности импульсов во всех последовательностях

tu -tc-,

Выходы формирователя 2 подключены к одному из входов ключевых элементов 3, каждый из которых состоит из временных селекторов 4 и 5 и триггера 6. Первый вход временного селекто-, ра 4, соединенный с выходом формирователя 2, подключен также к первому входу временного селектора 5, второй вход которого присоединёнк единичному выходу триггера б. Вторые входы всех временных селекторов 4 подключены через .формирователь импульсов 7 ко входу запуска 8 устройства.

Выходы временных селекторов 5 подключены к элементу ИЛИ 9, а выходы селекторов 4 - ко входам устройства переключения 10, выходы которого соединенны с единичными входами триггеров 6.

Выход элемента ИЛИ 9 подключен к входу счетчика импульсов 11, в который известными способами вводится дополнительный код К..р числа старших разрядов преобразуемого числового кода. Выход счетчика через дешифратор нуля 12 и элемент совпадения 13 подключен к выходу 14 преобразователя. При этом второй вход элемента совпадения 13 подключен к выходу элемента ИЛИ 9, а выход 14 - к нулевым входам триггеров 6 всех ключевых элементов 3.

Устройство переключения 10 состоит из последовательно соединенных регист

ра памяти 15, в который вводится код В.„д числа младших разрядов преобразуемого числового кода, дешифратора 16, вырабатывающего сигнал на одном из своих выходов в зависимости от кода Т1,д , логического узла 17, состоящего из элементов И, управляющие входы которых подключены к выходам дешифратора, а сигнальные - к выходам временных селекторов 4, и элементов ИЛИ 18, выходы которых являются выходами устройства переключения 10.

Логический узел устроен так, что при коде Т1| выход временного селектора 4 каждого I -го ключевого элемента соединен с единичным входом триггера б ( t + ЯМА)-го элемента.

В исходном состоянии коды К и R.j. введены в регистр 15 и счетчик 11, а триггеры б находятся в нулевом состоянии . Генератор 1 вырабатывает эталонную последовательность,которая при помощи формирователя сдвинутых импульсов 2 преобразуется в К импульсных последовательностей, сдвинутых одна относительно другой и поступающих на входы временных селекторов 4 и 5.

При поступлении на вход 8 импульса запуска формирователь коротких импульсов 7 вырабатывает сигнал/ который поступает одновременно на вторые входы временных селекторов 4. Допустим, что появление этого импульса совпадает с импульсом сдвинутой последовательноети, на входе 1-го ключевого элемента 3. Тогда на выходе временного селектора 4 1-го ключевого элемента появляется сигнал, который поступает в логический узел устройства переключения 10, откуда через соответствующий элемент ИЛИ 18 на единичный вход триггера б (1-|-К„д)-го ключевого элемента. Этот триггер устанавливается в единичное положение,открывая свой временный селектор 5.

промежуток времени, равный

Через 5 вход этого временного селектора с выхода формирователя 2 поступает первый импульс сдвинутой последовательности, проходит через этот селектор и через элемент ИЛИ 9

0 поступает на вход счетчика 11.

Счетчик II, в котором к началу работы был записан дополнительный код

после поступления на его

числа

СТ I

вход RC,T. счетных импульсов переполнится и на его выходе дешифратора 12 появится напряжение. .счетный импульс завершает ( времен- ный интервал с момента появления первого импульса на входе элемента ИЛИ 9, поэтому формируемый временный интервал заканчивается (Rcr )-ый импульсом. Этот импульс пройдя элемент ИЛИ 9, через открытый дешифратором элемент совпадения 13, поступает на выход 14 I преобразователя и на нулевые входы триггеров 6 ключевых элементов 3, под

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1983 |

|

SU1123022A2 |

| Устройство для считывания графической информации | 1980 |

|

SU963014A2 |

| Устройство для измерения частоты | 1982 |

|

SU1247773A1 |

| ПЛКЙТНО-ИХШЕСЙА*ЬИБ;1ИО'^ЕКАГ. Л. Биланов | 1972 |

|

SU342297A1 |

| Двухканальное устройство для сопряжения ЭВМ | 1989 |

|

SU1735860A1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU928635A1 |

| Цифровой измеритель температуры | 1981 |

|

SU974145A1 |

| Диапазонный измеритель временных интервалов последовательного счета | 1985 |

|

SU1307440A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

Авторы

Даты

1978-04-25—Публикация

1973-07-06—Подача