Шина записи кода задержки.

I 2g i JZ3

Шила записи кода длительности.

js

со

СП

Ъьт9

о

НИИ задержки 14, формирователя сигнала начального сброса 18. Устройство содержит также генератор стабильной частоты 1, триггеры 2,3, 4.1, 4.2, 4.3, 4.4, схемы совпадений 7 и 8, схемы совпадений 9.1, 9.2, 9.3, 9.4, 10.1, 10.2, 10.3, 10.4, 11.1,

11.2,11.3, 11.4 соответственно трех групп, линии задержки 12.1, 12.2,

12.3,13, 14, элементы ИЛИ 16, 17, 18, регистр 22 кода синтезируемой задержки, дешифратор 26, счетчик 27. Введенные элементы и их связи позволяют формировать как зн;ачение задержки, так и значение длительности задержанных импульсов в два этапа: грубо счетно-импульсным методом при помощи счетчика и точно в пределах грубого шага квантования шкалы при помощи хронотронной схемы, состоящей из последовательно соединенных линий задержки и группы схем совпадений. I ил

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения коэффициента прямоугольности амплитудно-частотной характеристики радиоприемников | 1990 |

|

SU1755383A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2001 |

|

RU2211540C2 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1388891A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ КОНТРОЛЯ ПО РАДИОКАНАЛУ | 2005 |

|

RU2280330C1 |

| Электронные часы с устройством коррекции | 1983 |

|

SU1278801A1 |

| Устройство для определения сопротивления до места однофазного короткого замыкания на землю линии электропередачи | 1987 |

|

SU1432428A1 |

| Устройство для контроля и сигнализации | 1990 |

|

SU1795494A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Устройство для сигнализации | 1990 |

|

SU1824645A1 |

Изобретение относится к контроль но-измерительной технике и может использоваться при создании и испытаниях различных устройств автоматики, телемеханики и аналого-цифрового преобразования информации. Цель изобретения - расширение функциональных возможностей путем обеспечения перестройки длительности задержанных импульсов с дискретностью, существенно меньшей периода генератора стабильной частоты, - достигается за счет введения дополнительного регистра 23, двух коммутаторов 24, 25 кодов, счетного триггера 5, формирователя 21 импульсов фронта, элементов ИЛИ 15, 19, 20, одновибратора 6, (п+1)-й лис Ц9 (Л с:

1

Изобретение относится к контрольно-измерительной технике и может использоваться при создании и испытаниях различных устройств автоматики, телемеханики и аналого-цифрового преобразования информации.

Цель изобретения - расширение фун I

циональньгх возможностей путем обеспечения перестройки длительности задержанных импульсов с высокой разрешающей способностью, существенно меньшей периода генератора стабильной частоты.

Поставленная цель достигается за счет введения в известное устройство дополнительного регистра, двух коммутаторов кодов, счетного триггера, формирователя импульсов фронта, трех элементов ИЛИ, одновибратора, линии задержки) формирователя сигнала начального сброса с соответствующими связями. Это позволяет формировать как значение задержки, так и значение длительности задержанных импульсов в два этапа: грубо-счетно- импульсным методом при помощи счетчика и точно в пределах грубого шага квантования шкалы - при помощи хронотронной схемы, состоящей из последовательно соединенных линий задержки и группы схем совпадений.

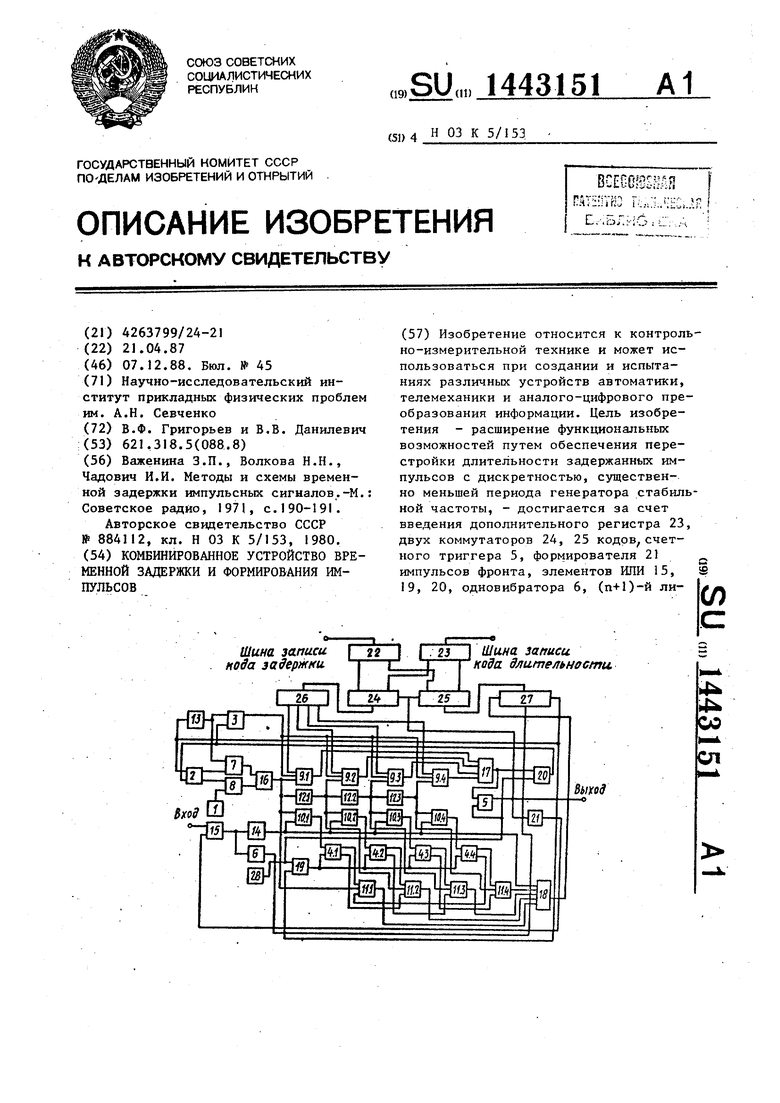

На .чертеже изображена схема устройства, (число п схем совпадений в каждой из групп выбрано равным четырем) .

Устройство содержит генератор 1 стабильной частоты, триггеры 2,3 и 4.1-4.4, счетный триггер 5, одновибратор 6, схемы 7 и 8 совпадений, схемы совпадений первой .4, второй 10.1-10.4 и третьей 11.1.-11.4 групп, линии 12.1-12.3, 13 и 14 задержки, логические элементы ИЛИ 15- 20, формирователь 2 импульсов фронта, первый регистр кода синтезируемой задержки 22, второй регистр кода длительности задержанного импульса 23, коммутаторы 24 и 25 кодов, дешифратор 26, счетчик 27, формиро- ватель 28 сигнала начального сброса.

Генератор 1 стабильной частоты соединен с первым входом схемы 8 совпадений, второй вход которой подключен к инверсному выходу триггера 2, а выход - к первому входу элемента ИЛИ 16, Схема 7 совпадений первым входом соединена с прямым выходом

триггера 2, а выходом подключена к второму входу элемента ИЛИ 16. Триггер 3 выходом подключен к первым входам схемы 9.1-9.4 совпадений первой группы, соединенных выходами со входами элемента ИЛИ 17. Каждая из схем 10.1-10.4 совпадений второй группы соединена своим выходом с входом установки единицы одного из триггеров 4.1-4.4, схем II.Л.-П.4 совпадений

третьей группы соединены своими первыми входами с прямыми выходами соответствующих триггеров 4. 1-4.4, а выходами - с четырьмя входами второго элемента ИЛИ 18.

Входы регистра 22 соединены пораз-

рядно с шинами записи кода задержки. Вторые входы схем 9.1-9.3, 10.. 1-10.3 и 11.1-11.3 совпадений во всех трех

группах подключены к йходам соответствующих линий 12.1-12.3 задержки, соединенных последовательно друг с другом, вторые входы схем 9.4,10.4 и 11.4 совпадений соединены с выходом линии 12.3 задержки, третьи входы схем 9.1-9.4 совпадений первой группы соединены с соответствующими выходами дешифратора 26, а вход ли- ю НИИ 12.1 задержки соединен с выходом элемента ИЛИ 16; Выход элемента ИЛИ 18 соединен с тактовым входом счетчика 27, выход которого подключен к входу установки единицы триггера 2 15 непосредственно и через линию 13 заержки - к входу установки единицы триггера 3 и второму входу схемы 7 совпадений. Входы установки нуля триггеров 2 и 3 соединены между со- 20 бой и подключены к выходу элемента ЛИ 20, инверсный выход каждого из триггеров 4.1-4.3 соединен с третьим входом соответствующей схемы 11.2, 11.3 и 11.4 совпадений, а триггер 25 4.4 инверсным выходом подключен к третьему входу схемы 11.1 совпадений. Регистр 23 соединен входами с щи- нами записи кода длительности выходных импульсов, коммутатор 24 со- 30 единен поразрядно своими первыми и вторыми входами с выходами младших разрядов регистров 22 и 23 соответственно, а выходами подключен поразрядно к соответствующим входам де- gg ифратора 26, коммутатор 25 соединен поразрядно своими первыми и вторыми входами с выходами старших разрядов регистров 22 и 23 соответственно, а выходами подключен пораз- 40 рядно к соответствующим информационым входам счетчика 27, счетный триггер 5 подключен своим тактовым вхоом к выходу элементов ИЛИ 17 и пер- ому взводу элемента ИЛИ 29, а выхо- 45 ом соединен с управляющими входами оммутаторов 24 и 25, выходной клемой устройства и через формирователь 21 импульсов фронта - с первым входом элемента ИЛИ 15, соединенного вторым 50 входом с входной клеммой устройства,, а выходом через одновибратор 6 - с входом установки режима счетчика 27 и, кроме того, чер ез линию 14 задержки - с первыми входами схем 10.1-10.4 55 совпадений второй группы и пятым входом элемента ИЛИ 18.

Формирователь 28 сигнала начального сброса своим выходом соединен с

входом установки нуля счетного триггера 5, вторым входом элемента ИЛИ 20 и первым входом элемента ИЛИ 19, второй вход которого соединен с выходом счетчика 27, а выход - с входами установки нуля триггеров 4. 1-4 .

Требуемое значение задержки в устройстве формируется в два этапа: грубо-счетно-импульсным методом при помощи счетчика и точно в пределах грубого шага квантования шкалы - при помощи хронотронной схемы, состоящей из последовательно соединенных линий 12.1.-12.3 задержки и группы схем 9.1-9.4 совпадений. Аналогичным образом задается длительность выходного импульса устройства.

В качестве эталона времени в схеме грубой задержки используется непрерывно работающий генератор стабилной частоты, неопределенность фазы которого относительно запускающих импульсов компенсируется с точностью до точного кванта при помощи устройства синхронизации, включающего в сбя, кроме упомянутых линий 12.1-12.3 задержки, две группы схем совп адений (10.I-I0.4, 11.1-11.4) и триггеры 4.1.-4.4.

При вк пючении питания устройства формирователь 28 сигнала начального сброса вырабатывает импульс, приводящий в нулевое состояние триггер 5, через элементы ИЛИ 19 - триггеры 4.1- 4,4, а через элемент ИЛИ 20 - триггеры 2 и 3. Перед началом работы в регистры 22 и 23 любым известным способом по шинам записи заносятся коды соответствующие требуемым значениям задержки и длительности выходного импульса.

Нулевому состоянию триггера 5, управляющего коммутаторами 24 и 25, соответствует подключение младших разрядов регистра 22 к входам дешифратора, а старших - к информационным входам счетчика. Триггер 2 блокирует схему 7 совпадений и деблокирует схему 8 совпадений, вследствие чего импульсы генератора 1, пройдя схему 8 совпадений и логический элемент ИЛИ 16, поступают на последовательно соединенные линии 12.1-12.3 задержки. Триггер 3 блокирует по первому входу схемы 9.1-9.4 совпадений первой группы. Выходы дешифратора 26 блокируют по третьему входу все схемы совпадений первой группы, за исключением

514

схемы, номер которой на единицу превышает число, занесенное в младшие разряды регистра 22. На входах дешифратора 26 присутствует код младших разрядов регистра 22, подключенного к нему через коммутатор 24.

Задерживаемый импульс через логический элемент ИЛИ 15 запускает одно- вибратор 6, сигналом с выхода которо- го счетчик 27 переводится в режим занесения. В это время сигналом элемент ИЛИ 15, прошедшим линию 14 задержки и элемент ИЛИ 18, осуществляется занесение в счетч ик 27 цифрового эквивален- та грубой части задержки, содержащегося в старших разрядах регистра 22. Одновременно схемы совпадений второй группы регистрируют совпадения выходного сигнала линии 14 задержки со сдвинутыми друг относительно друга во времени выходными импульсами элемента ИЛИ 16 и линий 12.1.-12.3 задержки. На выходах схем 10.1-10.4 совпадений группы, зарегистрировав- ших совпадения, появляются импульсы, которые устанавливают в единичное состояние соответствующие триггеры 4.1- 4.Д. группы. При этом первый из установившихся триггеров 4.1.-4.4 блоки- рует схему 11.1-11.4 совпадений третьей группы, номер которой превышает на единицу номер упомянутого триггера, и открывает схему совпадений с номером, равным номеру триггера. Так как вторые входы каждой схемы 11.1- 11.4 совпадений третьей группы присоединены к соответствующим отводам линий задержки 12.1-12.3 задержки, то в зависимости от момента прихода запускающего сигнала относительно фазы генератора 1 на выходе одной из icxeM 1 i . I - 1 . 4 совпадений третьей группы появляется серия импульсов , сфазиро- .ванная с моментом появления запускающе- го сигнала и начинающаяся следующим за совпадающим с этим сигналом импульсом об разцового генератора, С выхода логического элемента ИЛИ 18 эта серия импульсов поступает на тактовый вход счетчика 27, включенного в режим вычитания.

Для правильной работы схемы длительности входного з-адерживаемого и опорных сигналов, а следовательно, и временное разрешение схем 10.1-10-.4 совпадений выбираются так, чтобы совпадения могли регистрироваться только в одной или в двух смежных схемах

516

Минимальная длительность импульсов

I

определяется самой элементной базой.

При обнулении счетчика 27 его выходным сигналом устанавливается в единичное состояние триггер 2 и через элемент ИЛИ 19 сбрасываются триггеры 4.1.-4.4, Триггер 2 блокирует при этом схему 8 совпадений и деблокирует схему 7 совпадений, а на тактовый вход счетчика 27 прекращается поступление импульсов с логического , элемента ИЛИ 1 В.

Задержанный линией 13 задержки на время, необходимое для прекращения переходных процессов в линиях 2.1.- 12.3 задержки, выходной импульс счетчика 27 поступает на второй вход схв мы 7 совпадений и вход установки единицы, триггера 3, которьш при переключении в это состояние деблокирует по первым входам все схемы 9,1.-9.4 совпадений первой группы.

Импульс с выхода схемы 7 совпадений,пройдя логический элемент ИЛИ 16, поступает на вход линии 12.1 задержки , Дал ее этот импульс, пройдя по цепи линий 12.1-12.3 задержки и одну схему 9.1-9.4 совпадений первой группы, которая деблокирована по третьему входу дешифратором 26, подается на логический элемент ИЛИ 17 Выходным сигналом логического элемента ИЛИ 17 через логический элемент ИЛИ 20 сбра- сьшаются в исходк Ье состояние триггеры 2 и 3. Одновременно с этим выходным сигналом логического элемента ИЛИ 17 переключается в единичное состояние счетный триггер 5, что приводит к переключению коммутаторов 24 и 25, так, что входы дешифратора 26 ока зьшаются соединенными с младшими разрядами регистра 23 а выходы старщюс разрядов регистра 23 через коммутатор

Положительный перепад напряжения с выхода триггера 5 поступает на фор мирователь 21, вырабатывающий короткий импульс с длительностью, равной длительности входного задерживаемого сигнала, который, пройдя через логический элемент ИЛИ 15 и линию за- держки 14, запускает цикл формирования длительности выходного импульса.

Цикл формирования длительности повторяет предыдущий от момента поступления запускающего сигнала на второй вход логического элемента ИЛИ 15 до появления импульса на выходе логического элемента ИЛИ 17. Последним сбр сьшается в нулевое состояние счетный триггер 5 и схема переводится в исхо ное состояние. Наличие линии 14 задержки обеспечивает при этом запуск цикла формирования длительности толь когр после того момента, когда последний импульс цикла формирования за- держки покинет элементы 12.1.-12.3 и в них завершатся переходные процессы.

Величина временной задержки, формируемой устройством, определяется выражением:

Т, Т/+ KTi + МТ„

где Т, - постоянная величина, куда . входит временной сдвиг, создаваемый линиям.и 13 и 14 задержки, а также задержки логических элементов; Т - временной сдвиг, создаваемый одной секцией линии 12 задержкиi

К - число, занесенное в младшие разряды регистра 22 (для варианта устройства, приведенного на чертеже, оно может принимать значения от О до

3);

т - период следования импульсов генератора стабильной частоты 1 -, М - число, занесенное в старшие

разряды регистра 22. Величина Т должна выбираться из условия пТ TO. В реальной схеме это условие может не выполняться, из-за, чего возникнет несоответствие грубого и точного шагов квантования и неоднородность последнего. Для обеспечения работоспособности схемы и

518

исключения погрешностей по грубой шкале необходимо, чтобы превьпаение пТ над Тд не превосходило некоторо критической величины, когда возможн перекрытие очередного выходного импульса элемента 16 с предшествующим импульсом, еще не покинувшим цепь линий 12.1-12.3 задержки. Подобные ограничения накладываются и на пре- вьшгение Т над пТ, т.е. на отклонение их разности в противоположную сторону. Это необходимо для тогр, чтобы исключить тройные совпадения и просчеты по точной шкале.

Величина длительности импульса, формируемого на выходе устройства, определяется аналогичным образом через числа, занесенные в старшие и младшие разряды регистра 23, а также содержит постоянную составляющую, ограничивающую снизу диапазон длительности выходных сигналов.

Скважность импульсов опорного генератора в предлагаемом устройств зависит от выбранного значения шагов квантования по точной и грубой шкале. Определяющим при этом является значение точного шага кван- тования, минимально достижимое значение которого зависит, прежде всег от временного разрешения цепочек схем совпадений группы 10. Разрешение должно быть больше устанавливаемого шага квантования во избежание пропуска дискретов по точной шкале. С другой стороны оно не должно превьш1ать 2Т во избежание фиксации тройных совпадений импульсов образцового генератора с входными импульсами.

.Длительность выходного импульса задается с высокой точностью и может перестраиваться с малым шагом в пределах, соответствующих пределам перестройки значения задержки. Достигается данный результат без существенного усложнения устройства, поскольку основные цепи формирования задержки используются также и для задания длительности импульса

Конструктивно устройство полностью реализуется на интегральных схемах эмиттерно-связанной и тран- зисторно-тразисторной логики.

Формула изобретения

Комбинированное устройство временной задержки и формирования им9i

пульсов, содержащее n-1 последовательно соединенные линии задержки однаковой длины, первую группу из п схем совпадений, соединенных выхода- ми с первыми п входами первого элемента ИЛИ, вторую группу из п схем совпадений, каждая из которых соединена своим выходом с входом установки единицы одного из п триггеров, третью группу из п схем совпадений, соединенных свош-ги первыми входами с прямыми выходами соответствующих триггеров, а выходами - с первыми п входами второго элементами ИЛИ, ге- нератор стабильной частоты, соединенный с первым входом (Зп+1)-й схемы совпадений, второй вход которой подключен к инверсному выходу (п+1)- го триггера, а выход - к первому вхо ду третьего элемента ИЛИ, (Зп+2)-ю схему совпадений, первым входом соединенную с прямым выходом Сп+1)-го триггера, а выходом подключенную к второму входу третьего элемента ИЛИ, (п+2)-й триггер, выходом подключенный к первым входам п схем совпадений первой группы, регистр, входы которого соединены с шинами записи кода задержки, причем первые п-1 од- ноименных схем совпадений во всех трех группах соединены своими вторыми входами с входами соответствую1ЩИХ линий задержки, вторые входы схем совпадений с номером п всех трех

групп соединены с выходом (п-1)-и

линии задержки, вход первой линии

задержки соединен с выходом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с тактовым входом счетчика, третьи входы каждой из п

схем совпадений первой группы соединены с соответствующими выходами дешифратора, выход счетчика подключен к входу установки единицы (п+)- rt) триггера и через п-ю линию задержки - к входу установки единицы (п+2)-го триггера и второму входу (Зп+2)-й схемы совпадений, входы установки нуля (п+1)-го и (п+2)-го триггеров соединены между собой, инверсный выход каждого из n-l первых триггеров соединен с третьим входом одной схемы совпадений третьей груп- .пы с номером, на единицу большим но- мера триггера, а п-й триггер инверс- Hbw выходом подключен, к третьму вход первой схемы совпадений третьей груп51

10

пы, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения перестройки длительности задержанных импульсов с дискретностью, существенно меньщей периода генератора стабильной частоты, в него введены дополнительный регистр, соединенный входами с шинами записи кода длительности выходных импульсов, два коммутатора кодов, счетный триггер, формирователь импульсов фронта, четвертый, пятый и шестой элементы ИЛИ, одновибратор, ()-я линия задержки формирователь сигнала начального сброса, причем первый коммутатор соединен поразрядно своими первыми и вторыми входами с выходами младших разрядов соответственно основного и дополнительного регистров, а выходами подключен поразрядно к соответствующим входам дешифратора, второй комутатор соединен поразрядно своими первыми и вторыми входами с выходами старших разрядов соответственно основного и дополнительного регистров, а выходами подключен поразрядно к соответствующим информационным входам счетчика, счетный триггер подключен своим тактовым входом к выходу первого элемента ИЛИ и первому входу четвертого элемента ИЛИ, а выходом соединен с управляющими входами коммутаторов, выходной клеммой усройства и через формирователь импульсов фронта - с первым входом пятого элемента ИЛИ, соединенного в свою очередь вторым входом с входной клеммой устройства, а выходом через одновибратор - с входом установки режима счетчика и, кроме того, через (п+)-ю линию задержки - с первыми входами п схем совпадений второй группы и (п+1)-м входом второго элемента ИЛИ, формирователь сигнала начального сброса своим выходом соединен с входом установки нуля счетного триггера, вторьм входом четвертого элемента ИЛИ и первым входом шестого элемента ИЛИ, второй вход которого соединен с выходом счетчика, а выход - с входами установки нуля первых п триггеров, выход четвертого элемента ИЛИ соединен с входами установки нуля (п+1)- го и (п+2)-го триггеров.

| Важенина З.П., Волкова Н.Н., Чадович И.И | |||

| Методы и схемы временной задержки импульсных сигналов.-М.: Советское радио, 1971, с.190-191 | |||

| Времязадающее устройство | 1980 |

|

SU884112A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-07—Публикация

1987-04-21—Подача