Изобретение относится к измерительной и вычислительной технике. Преобразователь может быть использован в качестве вводного устройства цифровых измерительных или вычислительных устройств.

Известны Преобразователи частота-код, содержащие частотные датчики, генераторы образцовой частоты, линии задержки, схемы «И и «ИЛИ, реверсивный счетчик, связанный с регистром памяти, и включенную между генератором образцовой частоты и шиной прямого счета реверсивного счетчика первую схему «И, управляющий вход которой подсоединен к выходу селектора одиночного периода Сигнала частотного датчика.

Для этих устройств характерен больщой избыток информации, когда контролируемая величина на отдельных интервалах времени значительно больще шага квантования, а также потеря информации, соответствующей выброгам контролируемой величины в интервалах между измерениями.

Цель изобретения - уменьшение избыточности информации при повышении точности преобразования. Достигается она тем, что предлагаемый преобразователь содержит триггер, ключевую схему, формирователь знакопеременных прямоугольных импульсов с фильтDOM нижних частот на выходе, два дискриминатора уровня напряжения. Единичный вход триггера подключен к частотному датчику через ключевую схему с управляющим входом, соединенным с одним из ВЫХОДОБ селектора,

цель пуска которого через первую схему «ИЛИ соединена с выходом дискри мина горов уровней напряжения. Входы последних подключены к выходу фильтра нижних частот, а выход каждого разряда реверсивного

счетчика, кроме младшего разряда, связан с цепью считывания со входом разряда регистра памяти, имеющего на единицу меньщий номер. Выход каждого разряда регистра памяти соединен со входом одноименного разряда

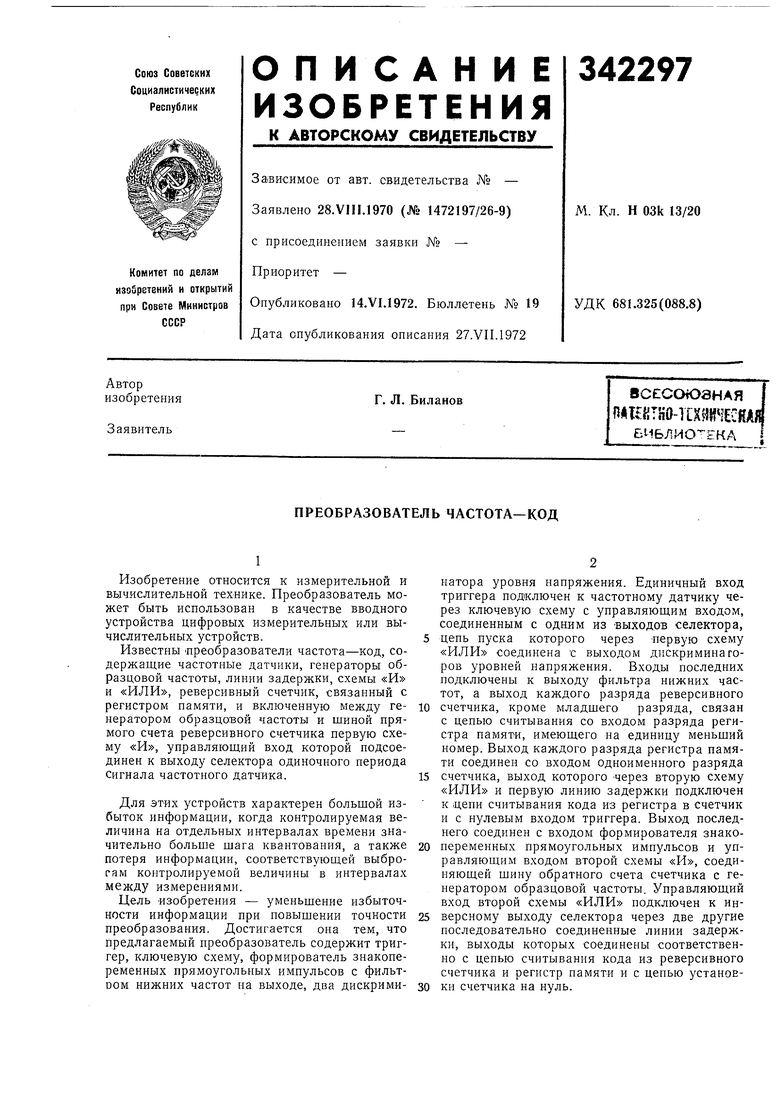

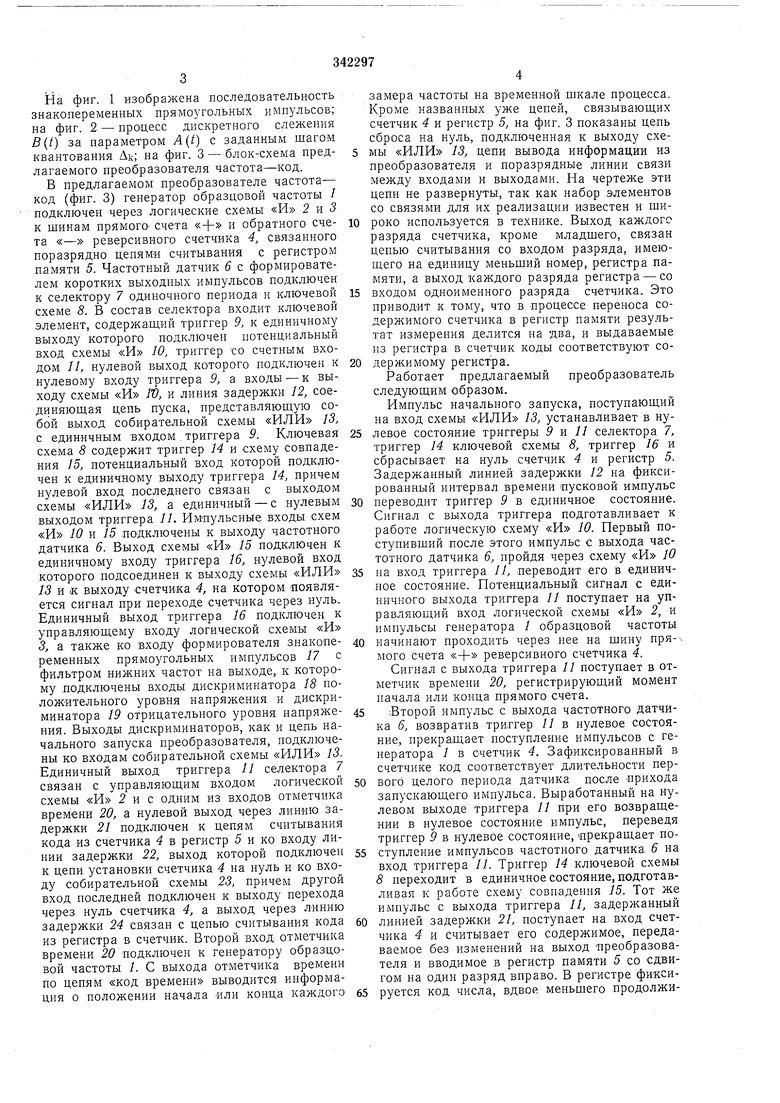

счетчика, выход которого через вторую схему «ИЛИ и первую линию задержки подключен к цени считывания кода из регистра в счетчик и с нулевым входом триггера. Выход последнего соединен с входом формирователя знакопеременных прямоугольных импульсов и управляющим входом второй схемы «И, соединяющей шину обратного счета счетчика с генератором образцовой частоты. Управляющий вход второй схемы «ИЛИ подключен к инверсному выходу селектора через две другие последовательно соединенные линии задержки, выходы которых соединены соответственно с цепью считывания кода из реверсивного счетчика и регистр памяти и с цепью установНа фиг. 1 изображена последовательность знакопеременных прямоугольных импульсов; на фиг. 2 - процесс дискретного слежения B(t) за параметром A(t) с заданным шагом квантования Ak; на фиг. 3 -блок-схема предлагаемого преобразователя частота-код.

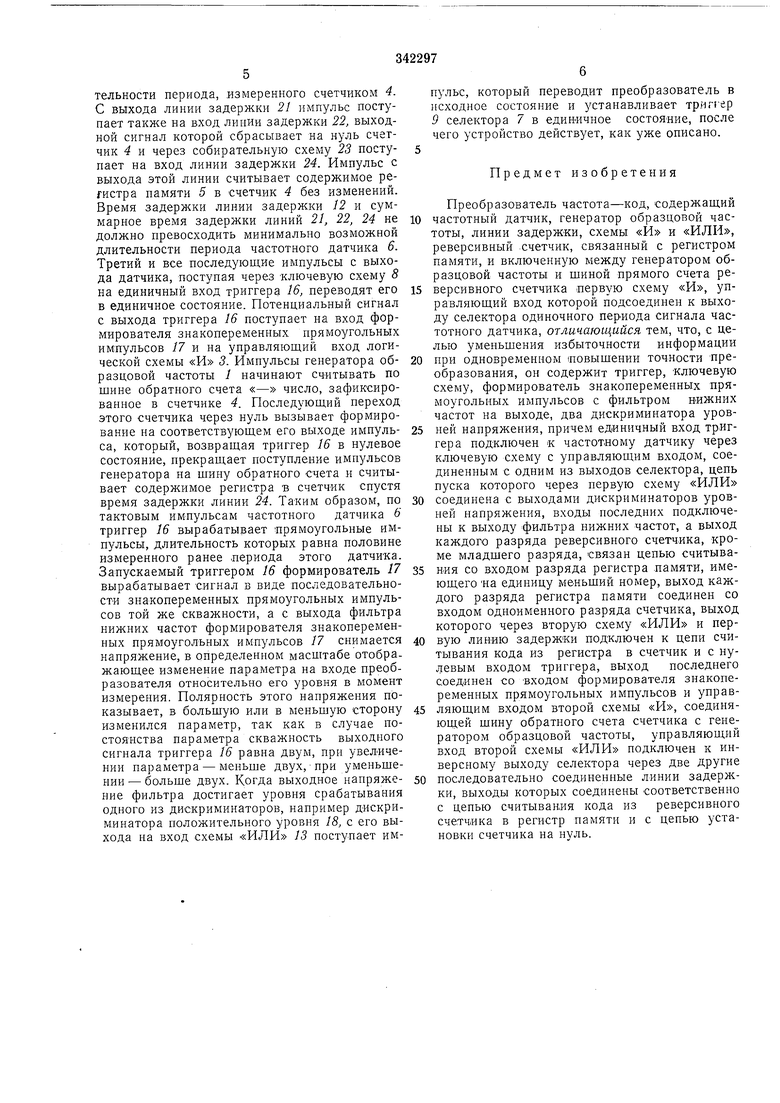

В предлагаемом преобразователе частота- код (фиг. 3) генератор образцовой частоты 1 подключен через логические схемы «И 2 и 5 к шинам прямого- счета «-|- и обратного счета «- реверсивного счетчика 4, связанного поразрядно цепями считывания с регистром памяти 5. Частотный датчик 6 с формирователем коротких выходных импульсов подключен к селектору 7 одиночного периода и ключевой схеме 8. В состав селектора входит ключевой элемент, содержащий триггер 9, к единичному выходу которого подключен потенциальный вход схемы «И 10, триггер to счетным входом 11, нулевой выход которого .подключен к нулевому входу триггера 9, а входы - к выходу схемы «И Ю, и линия задержки 12, соединяющая цепь пуска, представляющую собой выход собирательной схемы «ИЛИ 13, с единичным входом , триггера 9. Ключевая схема 8 содержит триггер 14 и схему совпадения 15, потенциальный вход которой подключен к единичному выходу триггера 14, причем нулевой вход последнего связан с выходом схемы «ИЛИ 13, а единичный - с нулевым выходом триггера 11. Импульсные входы схем «И 10 и 15 .подключены к выходу частотного датчика 6. Выход схемы «И 15 подключен к единичному входу триггера 16, нулевой вход которого подсоединен к выходу схемы «ИЛИ 13 и к выходу счетчика 4, на котором появляется сигнал при переходе счетчика через нуль. Единичный выход триггера 16 подключен к управляющему входу логической схемы «И 3, а также ко входу формирователя знакопеременных прямоугольных импульсов 17 с фильтром нижних частот на выходе, к которому подключены входы дискриминатора /8 положительного уровня напряжения и дискриминатора 19 отрицательного уровня напряжеНИН. Выходы дискриминаторов, как и цепь начального запуска преобразователя, подключены ко входам собирательной схемы «ИЛИ 13. Единичный выход триггера 11 селектора 7 связан с управляющим входом логической схемы «И 2 и с одним из входов отметчика времени 20, а нулевой выход через линию задержки 21 подключен к цепям считывания кода из счетчика 4 в регистр 5 и ко входу линии задержки 22, выход которой подключен к цепи установки счетчика 4 на нуль и ко входу собирательной схемы 23, причем другой вход последней подключен к выходу перехода через нуль счетчика 4, а выход через линию задержки 24 связан с цепью считывания кода из регистра в счетчик. Второй вход отметчика времени 20 подключен к генератору образцовой частоты 1. С выхода отметчика времени по цепям «код времени выводится информация о положении начала или конца каждого

замера частоты на временной шкале процесса. Кроме названных уже цепей, связывающих счетчик 4 и регистр 5, на фиг. 3 показаны цепь сброса иа нуль, подключенная к выходу схемы «ИЛИ 13, цепи вывода информации из преобразователя и поразрядные линии связи между входами и выходами. На чертеже эти цепи не развернуты, так как набор элементов со связя.ми для их реализации известен и широко используется в технике. Выход каждого разряда счетчика, кроме младшего, связан цепью считывания со входом разряда, имеющего на единицу меньший номер, регистра памяти, а выход каждого разряда регистра - со входом одноименного разряда счетчика. Это приводит к тому, что в процессе переноса содержимого счетчика в регистр памяти результат измерения делится на два, и выдаваемые из регистра в счетчик коды соответствуют содержимому регистра.

Работает предлагаемый преобразователь следующим образом.

Импульс начального запуска, поступающий на вход схемы «ИЛИ 13, устанавливает в нулевое состояние триггеры 9 тл. 11 селектора 7, триггер 14 ключевой схемы 8, триггер 16 и сбрасывает на нуль счетчик 4 и регистр 5. Задержанный линией задержки 12 на фиксированный интервал времени пусковой импульс переводит триггер 9 в единичное состояние. Сигнал с выхода триггера подготавливает к работе логическую схему «И 10. Иервый поступивший после этого импульс с выхода частотного датчика 6, пройдя через схему «И W на вход триггера 11, переводит его в единичное состояние. Нотенциальный сигнал с единичного выхода триггера 11 поступает на управляющий вход логической схемы «И 2, и импульсы генератора 1 образцовой частоты начинают проходить через нее на шину пря--. мого счета «4- реверсивного счетчика 4.

Сигнал с выхода триггера 11 поступает в отметчик времени 20, регистрирующий момент начала или конца прямого счета.

Второй импульс с выхода частотного датчика 6, возвратив триггер 11 -в, нулевое состояние, прекращает поступление импульсов с генератора / в счетчик 4. Зафиксированный в счетчике код соответствует длительности первого целого периода датчика после прихода запускающего импульса. Выработанный на нулевом выходе триггера 11 при его возвращении в нулевое состояние импульс, переведя триггер 9 в нулевое состояние, прекращает поступление импульсов частотного датчика. 6 на вход триггера П. Триггер 14 ключевой схемы 8 переходит в единичное состояние, подготавливая к работе схему совпадения 15. Тот же импульс с выхода триггера 11, задержанный линией задержки 21, поступает на вход счетчика 4 и считывает его содержимое, передаваемое без изменений на выход преобразователя и вводимое в регистр памяти 5 со сдвигом на один разряд вправо. В регистре фиксируется код числа, вдвое меньщего продолжительности периода, измеренного счетчиком 4. С выхода линии задержки 2 импульс поступает также на вход липии задержки 22, выходной сигнал которой сбрасывает на нуль счетчик 4 и через собирательную схему 23 поступает на вход линии задержки 24. Импульс с выхода этой линии считывает содержимое регистра памяти 5 в счетчик 4 без изменений. Время задержки линии задержки 12 и суммарное время задержки линий 21, 22, 24 не должно превосходить минимально возможной длительности периода частотного датчика 6. Третий и все последующие импульсы с выхода датчика, поступая через -ключевую схему 8 на единичный вход триггера 16, переводят его в единичное состояние. Потенциальный сигнал с выхода триггера 16 поступает на вход формирователя знакопеременных прямоугольных им:пульсов 17 И На управляющий вход логической схемы «И 3. Импульсы генератора образцовой частоты 1 начинают считывать по шине обратного счета «- число, зафиксированное в счетчике 4. Последующий переход этого счетчика через нуль вызывает формирование на соответствующем его выходе импульса, который, возвращая триггер 16 в нулевое состояние, прекращает поступление импульсов генератора на шину обратного счета и считывает содержимое регистра в счетчик спустя время задержки линии 24. Таким образом, по тактовым импульсам частотного датчика 6 триггер 16 вырабатывает -прямоугольные импульсы, длительность которых равна половине измеренного ранее лериода этого датчика. Запускаемый триггером 16 формирователь 17 вырабатывает сигнал в виде последовательности знакопеременных прямоугольных импульсов той же скважности, а с выхода фильтра нижних частот формирователя знакопеременных прямоугольных импульсов 17 снимается напряжение, в определенном масштабе отображающее изменение параметра на входе преобразователя относительно его уровня в момент измерения. Полярность этого напряжения показывает, в большую или в меньшую сторону изменился параметр, так как в случае постоянства параметра скважность выходного сигнала триггера 16 равна двум, при увеличении параметра - меньше двух, при уменьшении - больше двух. Когда выходное напряжение фильтра достигает уровня срабатывания одного из дискриминаторов, например дискриминатора положительного уровня 18, с его выхода на вход схемы «ИЛИ 13 поступает импульс, который переводит преобразователь в исходное состояние и устанавливает тр.чггер 9 селектора 7 в единичное состояние, после чего устройство действует, как уже описано.

Предмет изобретения

Преобразователь частота-код, содержащий

частотный датчик, генератор образцовой частоты, линии задержки, схемы «И и «ИЛИ, реверсивный счетчик, связанный с регистром памяти, и включенную между генератором образцовой частоты и шиной прямого счета реверсивного счетчика первую схему «И, управляющий вход которой подсоединен к выходу селектора одиночного периода сигнала частотного датчика, отличающийся тем, что, с целью уменьшения избыточности информации

при одновременном повышении точности Преобразования, он содержит триггер, ключевую схему, формирователь знакопеременных прямоугольных импульсов с фильтром нижних частот на выходе, два дискриминатора уровней напряжения, причем единичный вход триггера подключен к частотному датчику через ключевую схему с управляющим входом, соединенным с одним из выходов селектора, цепь пуска которого через первую схему «ИЛИ

соединена с выходами дискриминаторов уровней напряжения, входы последних подключены к выходу фильтра нижних частот, а выход каждого разряда реверсивного счетчика, кроме младшего разряда, связан цепью считывания со входом разряда регистра .памяти, имеющего на единицу меньщий номер, выход каждого разряда регистра памяти соединен со входом одноименного разряда счетчика, выход которого через вторую схему «ИЛИ и первую линию задержки подключен к цепи считывания кода из регистра в счетчик и с нулевым входом триггера, выход последнего соединен со входом формирователя знакопеременных прямоугольных импульсов и управляющим входом второй схемы «И, соединяющей шину обратного счета счетчика с генератором образцовой частоты, управляющий вход второй схемы «ИЛИ подключен к инверсному выходу селектора через две другие

последовательно соединенные линии задерн ки, выходы которых соединены соответственно с цепью считывания кода из реверсивного счетчика в регистр памяти и с цепью установки счетчика на нуль.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Устройство для вычисления скорости изменения параметра | 1984 |

|

SU1275473A1 |

| Устройство для определения вероятностных характеристик фазы случайного сигнала | 1982 |

|

SU1112377A1 |

| Многоканальный программируемый генератор импульсов | 1986 |

|

SU1374413A1 |

| Устройство для предотвращения боксования тепловоза | 1981 |

|

SU994311A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU928635A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Частотный дискриминатор | 1984 |

|

SU1241142A1 |

| Устройство для передачи и приема информации | 1989 |

|

SU1656572A1 |

| Устройство для сбора данных о состоянии массы, перемещаемой технологическими линиями | 1989 |

|

SU1810897A1 |

Даты

1972-01-01—Публикация