(54) СТАРТСТОПНОЕ ПРИЕМНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕГРАФНЫХ СИГНАЛОВ12 | 1972 |

|

SU340106A1 |

| Старт-стопный приемник | 1982 |

|

SU1109931A1 |

| Устройство для приема кодовых комбинаций | 1986 |

|

SU1378079A1 |

| Устройство для приема дискретной информации | 1976 |

|

SU642870A1 |

| Приемное стартстопное устройство | 1985 |

|

SU1325721A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2006 |

|

RU2312465C1 |

| Устройство для настройки стартстопного приемника на скорость передачи | 1976 |

|

SU620026A1 |

| Приемное стартстопное устройство | 1985 |

|

SU1317679A1 |

| Устройство для фазирования электронного телеграфного приемника | 1983 |

|

SU1124437A1 |

| Устройство для передачи дискретной информации | 1975 |

|

SU588654A1 |

Изобретение относится к электросвязи и может использоваться в аппаратуре приема и передачи .

Известно устройство, содержащее первый элемент ИЛИ, счетчик-формирователь, первый выход которого через первый элемент И соединен с одним входом накопителя, вход сброса которого через второй элемент ИЛИ соединен с выходом второго элемента И, триггер блокировки, первый выход которого соединен с одним входом первого трехвходового элемента И, на другой вход которого и на первый вход третьего элемента И подаются опорные импульсы 1.

Однако, известное приемное устройство громоздко и имеет низкую помехоустойчивость.

Цель изобретения - повышение помехоустойчивости и упрощение устройства за счет исключения входного триггера, дифференцирующей цепи, линии задержки, счетчика конца знака, анализирующего счетчика, одного элемента ИЛИ.

Для этого в стартстопное приемное устройство, содержащее первый элемент ИЛИ, счетчик-формирователь, первый выход которого через первый элемент И соединен с одним входом накопителя, вход сброса которого через второй элемент ИЛИ соединен с выходом второго

элемента И, триггер блокировки, первый выход которого соединен с одним входом первого трехвходового элемента И, на другой вход которого и на первый вход третьего элемента И подаются опорные импульсы, введены второй трехвходовой элемент И, четвертый элемент И и инвертор, причем вход инвертора, первый вход второго трехвходового элемента И и другой вход накопителя объединены и являются . входом устройства, другой вход второ1ю трехвходового элемента И соединен с первым выходом триггера блокировки, другой выход которого соединен с другим входом первого элемента И и вторым входом третьего элемента И, выход которого соединен с первым входом первого элемента ИЛИ, другой вход которого соединен с выходом второго трехвходового элемента И, на третий вход которого подаются опорные импульсы, а выход первого элемента ИЛИ через счетчик-формирователь и четвертый элемент И соединен с- одним входом триггера блокировки, другой вход которого соединен с выходом второго элемента И, первый вход которого соединен с первым выходом счетчика-формирователя, а другой вход второго элемента И соединен с первым выходом т|П1ггера блокировки, при этом другой вход четвертого элемента И соединен с выходом н;;К(

пителя, а выход инвертора через первый трехвходовой элемент И соединен с входом сброса счетчика-формирователя и вторым входом второго элемента ИЛИ,

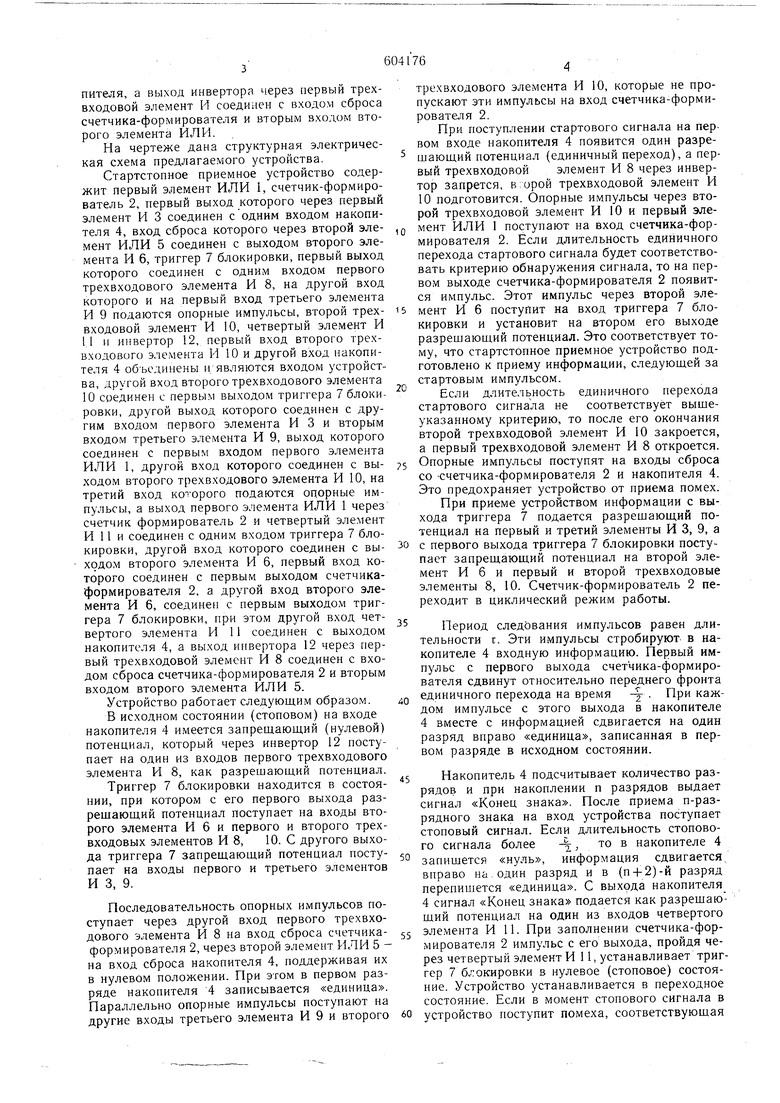

На чертеже дана структурная электрическая схема предлагаемого устройства.

Стартстопное приемное устройство содержит первый элемент ИЛИ 1, счетчик-формирователь 2, первый выход которого через первый элемент И 3 соединен с одним входом накопителя 4, вход сброса которого через второй элемент ИЛИ 5 соединен с выходом второго элемента И 6, триггер 7 блокировки, первый выход которого соединен с одним входом первого трехвходового элемента И 8, на другой вход которого и на первый вход третьего элемента И 9 подаются опорные импульсы, второй трехвходовой элемент И 10, четвертый элемент И 1,1 и инвертор 12, первый вход второго трехвходового элемента И 10 и другой вход накопителя 4 объединены н являются входом устройства, другой вход второго трехвходового элемента 10 соединен с первым выходом триггера 7 блокировки, другой выход которого соединен с другим входом первого элемента И 3 и вторым входом третьего элемента И 9, выход которого соединен с первым входом первого элемента ИЛИ 1, другой вход которого соединен с выходом второго трехвходового элемента И 10, на третий вход которого подаются опорные импульсы, а выход первого элемента ИЛИ 1 через счетчик формирователь 2 и четвертый элемент И 11 и соединен с одним входом триггера 7 блокировки, другой вход которого соединен с выходом второго элемента И 6, первый вход которого соединен с первым выходом счетчикаформирователя 2, а другой вход второго элемента И 6, соединен с первым выходом триггера 7 блокировки, при этом другой вход четвертого элемента И 11 соединен с выходом накопителя 4, а выход инвертора 12 через первый трехвходовой элемент И 8 соединен с входом сброса счетчика-формирователя 2 и вторым входом второго элемента ИЛИ 5.

Устройство работает следующим образом. В исходном состоянии (стоповом) на входе накопителя 4 имеется запрещающий (нулевой) потенциал, который через инвертор 12 поступает на один из входов первого трехвходового элемента И 8, как разрешающий потенциал.

Триггер 7 блокировки находится в состояНИИ, при котором с его первого выхода разрещающий потенциал поступает на входы второго элемента И 6 и первого и второго трехвходовых элементов И 8, 10. С другого выхода триггера 7 запрещающий потенциал поступает на входы первого и третьего элементов И 3, 9.

Последовательность опорных импульсов поступает через другой вход первого трехвходового элемента И 8 на вход сброса счетчикаформирователя 2, через второй элемент ИЛИ 5 на вход сброса накопителя 4, поддерживая их в нулевом положении. При этом в первом разряде накопителя 4 записывается «единица. Параллельно опорные импульсы поступают на другие входы третьего элемента И 9 и второго

трехвходового элемента И 10, которые не пропускают эти импульсы на вход счетчика-формирователя 2.

При поступлении стартового сигнала на первом входе накопителя 4 появится один разрешающий потенциал (единичный переход), а первый трехвходовой элемент И 8 через инвертор запрется, в горой трехвходовой элемент И 10 подготовится. Опорные импульсы через второй трехвходовой элемент И 10 и первый элемент ИЛИ 1 поступают на вход счетчика-формирователя 2. Если длительность единичного перехода стартового сигнала будет соответствовать критерию обнаружения сигнала, то на первом выходе счетчика-формирователя 2 появится импульс. Этот импульс через второй элемент И 6 поступит на вход триггера 7 блокировки и установит на втором его выходе разрещающий потенциал. Это соответствует тому, что Стартстопное приемное устройство подготовлено к приему информации, следующей за стартовым импульсом.

Если длительность единичного перехода стартового сигнала не соответствует выщеуказанному критерию, то после его окончания второй трехвходовой эле.мент И 10 закроется, а первый трехвходовой элемент И 8 откроется. Опорные импульсы поступят на входы сброса со -счетчика-формирователя 2 и накопителя 4. Это предохраняет устройство от приема помех.

При приеме устройством информации с выхода триггера 7 подается разрещающий потенциал на первый и третий элементы И 3, 9, а с первого выхода триггера 7 блокировки поступает запрещающий потенциал на второй элемент И 6 и первый и второй трехвходовые элементы 8, 10. Счетчик-формирователь 2 переходит в циклический режим работы.

Период следования импульсов равен длительности г. Эти импульсы стробируют- в накопителе 4 входную информацию. Первый импульс с первого выхода счетчика-формирователя сдвинут относительно переднего фронта единичного перехода на время - . При каждом импульсе с этого выхода в накопителе 4 вместе с информацией сдвигается на один разряд вправо «единица, записанная в первом разряде в исходном состоянии.

Накопитель 4 подсчитывает количество разрядов и при накоплении п разрядов выдает сигнал «Конец знака. После приема п-разрядного знака на вход устройства поступает стоповый сигнал. Если длительность стопового сигнала более -, то в накопителе 4 запишется «нуль, информация сдвигается вправо на. один разряд и в (п4-2)-й разряд перепишется «единица. С выхода накопителя 4 сигнал «Конец знака подается как разрешающий потенциал на один из входов четвертого элемента И 11. При заполнении счетчика-формирователя 2 импульс с его выхода, пройдя через четвертый элемент И 11, устанавливает триггер 7 б токировки в нулевое (стоповое) состояние. Устройство устанавливается в переходное состояние. Если в момент стопового сигнала в устройство поступит помеха, соответствующая

Авторы

Даты

1978-04-25—Публикация

1976-05-24—Подача