(54) ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ

ДЕЛЕНИЯ

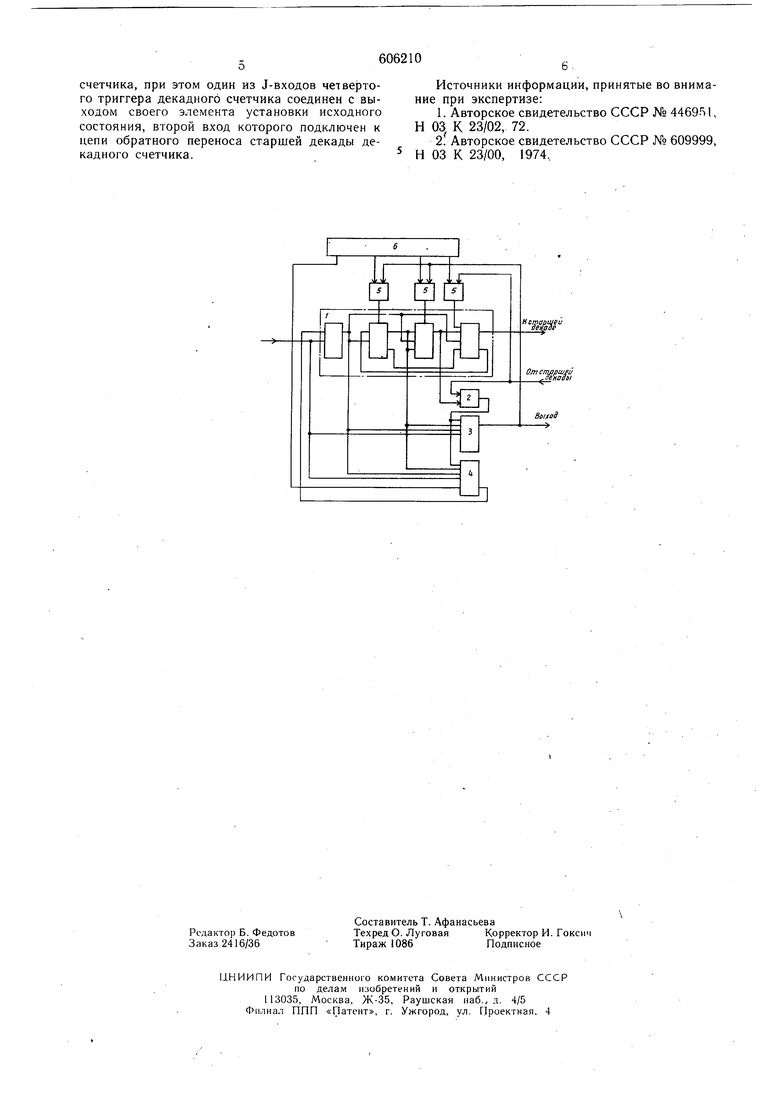

Устройство содержит декадный счетчик 1, элемент И 2, необходимый для расширения J-входов выходного 3 и коммутирующего 4 триг герое; элементы И-НЕ 5 установки исходного состояния, одни входы которых связаны с соответствующими выходами кодирующего блока 6, вторые входы - с выходом триггера 3 и с цепью обратного переноса старщей декады счетчика. Выходы первого и второго элементов И-НЕ 5 подключены соответственно к S-входам второго и третьего триггеров счетчика 1, выход третьего элемента И-НЕ 5 - к J-входу четвертого триггера.

В исходном состоянии триггеры счетчика Г находятся в положении, соответствующем числу п 9 - N, где N - коэффициент деления декады разряда единиц.

Так как четвертый триггер декадного счетчика 1 переключается в единичное состояние не от восьмого входного импульса, а от щесто-. го, десятичные числа (п) 6 и 7 записываются в счетчик в виде двоичных чисел 1110 и 1111.

Триггеры 3 и 4 в исходном состоянии находятся в нулевом положении. Низкий уровень выхода триггера 3 через элемент И-НЕ 5 обеспечивает высокие уровни напряжения на S-выходах второго и третьего триггеров, а инверсный выход триггера 4 - высокий уровень напряжения на J-входе первого триггера.

Низкий уровень цепи обратного переноса обеспечивает высокие уровни напряжения через элемент И-НЕ 5 на J-входе четвертого триггера и через элемент И 2 - на одном из трех связанных логикой И J-входов триггеров 3 и 4.

Счетчик 1 наполняется следующим образом. Каждый входной импульс, поступая на С-вход первого триггера, изменяет состояние счетчика. В каждом десятичном цикле счета щестое (1110) состояние счетчика сопровождается возникновением на выходе четвертого триггеру высокого уровня напряжения, нулевое (00) состояние - возникновением низкого уровня.

Формирующиеся таким образом импульсы переноса имеют длительность 4Твд,..что соответствует скважности 2, 5. Следовательно, требование к быстродействию старшей декады счетчика по сравнению с первой может быть снижено в восемь раз.

Когда старщая декада счетчика заполняется, в цепи обратного переноса возникает высокий уровень напряжения, а счетчик продолжает последний цикл счета. Под воздействием щестого входного импульса последнего цикла счета четвертый триггер в зависимости от кодовой комбинации записываемого числа либо переключается в единичное состояние либо остается в нулевом. При коэффициентах деления О, 1, 2, 3 на выходе старщего разряда блока 6 - низкий уровень напряжения, поэтому высокий уровень на выходе соответствующего элемента И-НЕ 5 не препятствует переключению четвертого триггера в единичное состояние. В остальных случаях на этом выходе блока 6 - высокий уровень напряжения, который совпадает с высоким уровнем напряжения цепи обратного переноса старщей декады, и на выходе элемента И-НЕ 5 образуется низкий уровень напряжения. Поступая на один из J-входов, связанных логикой И, этот низкий уровень препятствует переключению четвертого триггера в единичное состояние. После воздействия седьмого входного импульса последнего цикла счета три первых триггера оказываются в единичном состоянии, в результате чего на всех J-входах триггеров 3 и 4 устанавливаются высокие уровни напряжения. Восьмой входной импульс переключает три первых триггера в нулевое состояние, а триггер 3 - в единичное. Триггер 4 либо тоже переключается в единицу, если коэффициент деления первой декады (разряда единиц) нечетный и на выходе младщего разряда блока 6,

5 а следовательно и на R-входе триггера, высокий уровень напряжения. При четном коэффициенте деления триггер 4 остается в нулевом состоянии.

Девятый входной импульс последнего цикла счета возвращает триггер 3 в нулевое состояние. Короткий высокий уровень напряжения на выходе триггера 3 равен длительности периода входного сигнала и является выходным сигналом делителя. Этот импульс, поступая на входы элементов И-НЕ 5, устанавливает исходное состояние второго и третьего триггеров в соответствии с кодовой комбинацией, поступающей с блока 6 на вторые входы элементов И-НЕ 5.

Девятый же входной импульс устанавливает в исходное состояние первый триггер пер вой декады счетчика 1. Если коэффициент деления этой декады четный, на J-выходе первого триггера - высокий уровень напряжения, и девятый входной импульс устанавливает его в единичное состояние. При нечетном коэффициенте деления на J-входе первого триггера - низкий уровень напряжения, поэтому первый триггер остается в нулевом состоянии, а коммутирующий триггер 4 возвращается в нулевое состояние.

На этом цикл работы делителя завершается.

° Работа схемы в установившемся режиме заключается в повторении эtиx циклов.

Формула изобретения

5Делитель частоты с переменным коэффициентом деления, содержащий декадный счетчик, выходной и коммутирующий триггеры и кодирующий блок, выходы которого соединены с первыми входами элементов установки исходного состояния, отличающийся тем, что, с целью упрощения и повышения быстродействия, J-входы триггеров подключены к единичным выходам трех первых триггеров декадного счетчика и к цепи обратного переноса старщей декады, С-входы объединены и подключены ко

5 входному зажиму, R-вход коммутирующего триггера - к выходу младшего разряда кодирующего блока, нулевой выход - к J-входу первого триггера декадного счетчика, а единичный выход выходного триггера - ко вторым входам эл ементов установки в исходное состоя ние второго и третьего триггеров декадного

счетчика, при этом один из J-входов четвертого триггера декадного счетчика соединен с выходом своего элемента установки исходного состояния, второй вход которого подключен к цепи обратного переноса старшей декады декадного счетчика.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № , Н 03 К 23/02, 72.

2.Авторское свидетельство СССР № 609999, Н 03 К 23/00, 1974..

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэф-фициентом деления | 1974 |

|

SU509999A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| Делитель частоты следования импульсов | 1984 |

|

SU1181134A1 |

| Дискретный фазовращатель для генератора инфранизких частот | 1973 |

|

SU547965A1 |

| Преобразователь частоты в код | 1977 |

|

SU746922A1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| Программируемый делитель частоты | 1975 |

|

SU621099A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

1Отстрршеа

, аеноЗт

Авторы

Даты

1978-05-05—Публикация

1976-03-23—Подача