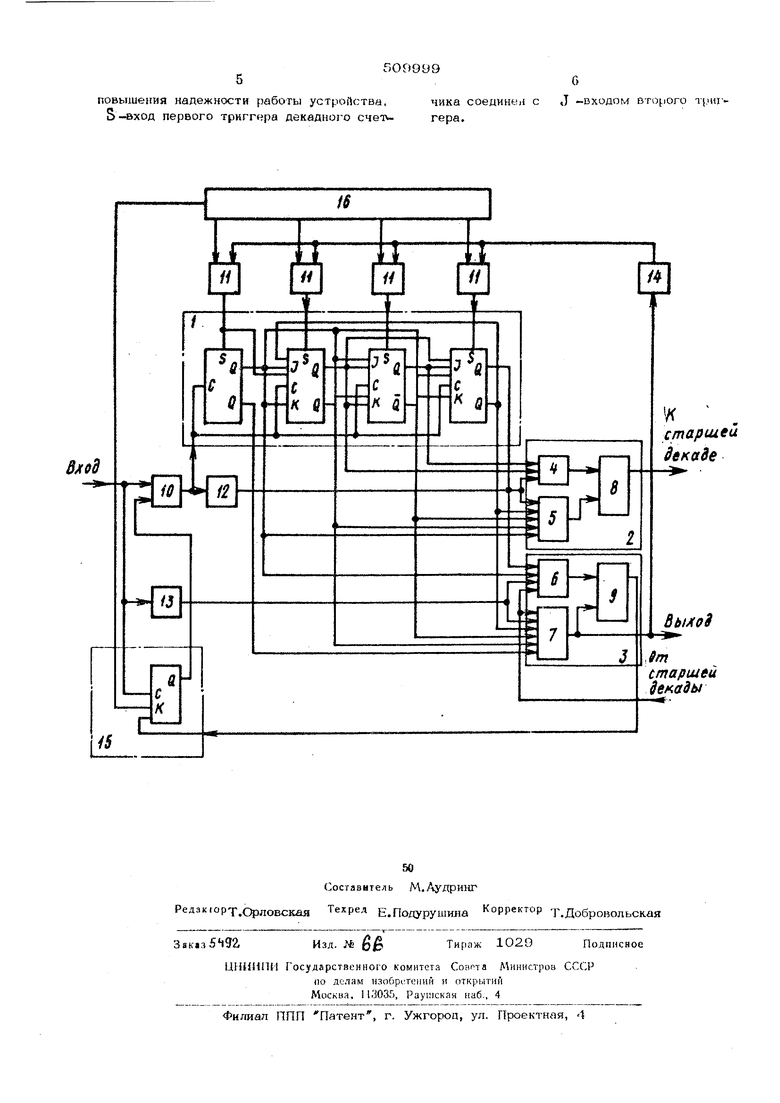

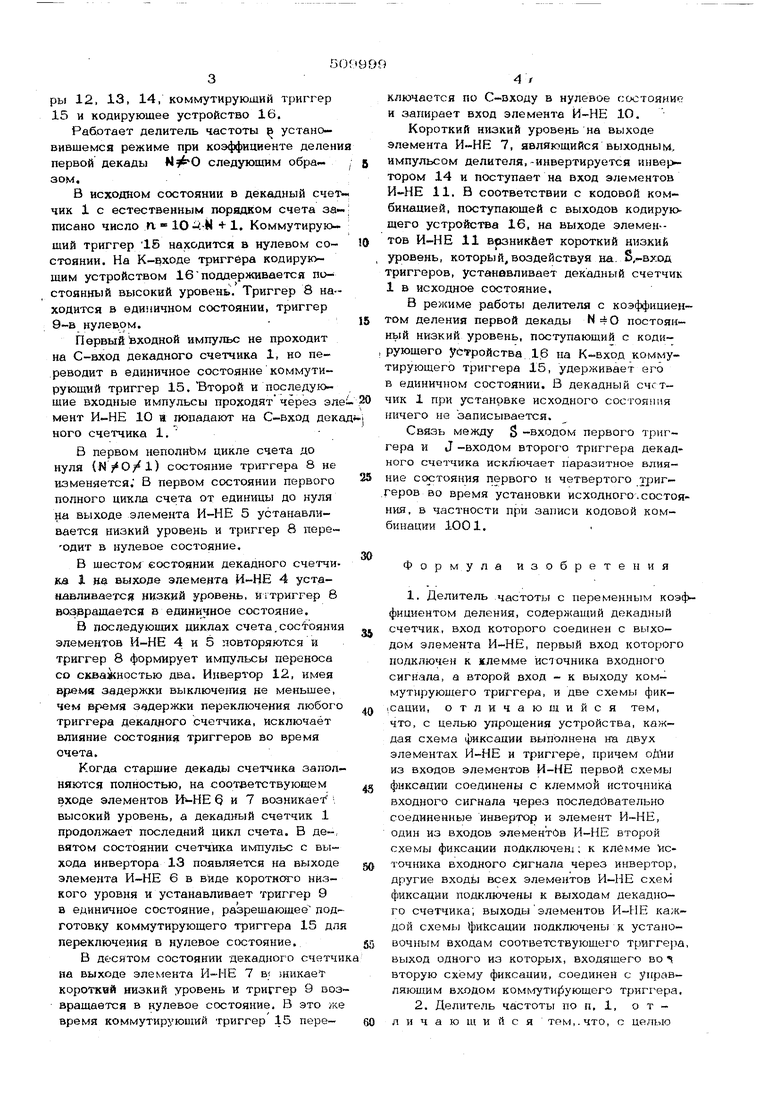

Изобретение относится к. импульсной технике и может быть использовано в раз личных радиотехнических устройствах, в том числе в цифровых синтезаторах часто ты., Известен делитель частоты с nepefvseFi ным коэффициентом деления, содержащий декадный счетчик, вход которого соединен С выходом элемента И-НЕ, один вход ко торого подключен к источника вход ного сигнала, а другой вход к выходу коммутирующего триггера, и две схемы фи сации. Недостаткам известного делителя частоты являются сложность и ненадежность работы вследствие паразитного состояний первого и четвертого триггеров декадного счетчика во время установки исходного состояния. В предложенном делителе частоты указанные недостатки устранены благодаря тому, что каждая схема фиксации выполнена на двух элементах И-НЕ и триггере, причем одни из входов элементов И-НЕ первой схемы фиксации соединены с клемшой 1тстсчиика кходного гигиалп -шраа иоследоБвтельно с(ед1П5э;;н1:а инвертор и snervfefiT И«И, о;;ни ,з ВХОДОБ эяe sнтoв И.НЕ второй cxttMb фиксации иолключени к клемме исгочни1:л вхолкого сигнала через инвертор, друпгя .:гпдь1 нсех элемеитоБ И.НН схем фпксацпп гк лключепы к выходам декялпого сччтчика: Вь1ходы элеiviGHTOD U.Mb Ka;i;ao)i фиксации под- слюченьг к ycTniioBOMiiKftv-f входам соответствующего )д, В1,ход триггера, входящего во вторую фиксации, соеди-ч нон с управляющим входо : коммуттфуюше- го триггера, В-вход пг-рьчого триггера декадного счетчика соелинен с J -входом второго триггера. На чертеже представлена структурная схема предложенного дел -:теля частоты с переменныг- коэфифицнентом деления. Делитель частоты содержит декадный счетчик 1, схемы фиксации 2 и 3, в каждую из KOTopbix соответственно входят элементь И НЕ 4, 5 и 6, 7 и Tpisrrep 8, 9, элементы И.«НЕ 10 и 11, инверто- ры 12, 13, 14, коммутирующий триггер 15 и кодирующее устройство 16. Работает делитель частоты установившемся режиме при коэффициенте делен первой декады следующим обра зом. В исходном состоянии в декадный счет чик 1 с естественным порядком счета за писано число п. « Ю Д-N + 1. Коммутиру1о. щий триггер 15 находится в нулевом состоянии. На К-входе триггера кодирующим устройством 16поддерживается постоянный высокий уровень. Триггер 8 находится в единичном состоянии, триггер 9-в нулевом. Первый входной импульс на проходит на С-вход декадного счетчика 1, но переводит в единичное состояние коммутирующий триггер 15. Второй и последующие входные импульсы проходят через эл мент И-НЕ 1О и попадают на С-вход дек ного счетчика 1, В первом неполнЬм цикле счета до нуля (N ) состояние триггера 8 не изменяется; В первом состоянии первого полного цикла счета от единицы до нуля а выходе элемента И-НЕ 5 устанавливается низкий уровень и триггер 8 пере одит в нулевое состояние. В шестом .еостоянии декадного счетчи jga i на выходе элемента И-НЕ 4 устанавливается низкий уровень, Hi триггер В возвращается в единичное состояние. В последующих циклах счета,состояни элементов И-НЕ 4 и 5 повторяются н триггер 8 формирует импульсы переноса со скважностью два. Инвертор 12, имея время задержки выключения не меньшее, чем время задержки переключения любого триггера декадного счетчика, исключает влияние состояния триггеров во время счета. Когда старшие декады счетчика запол няются полностью, на соотеетствуюшем входе элементов Q и 7 возникает 1 высокий уровень, а декадный счетчик 1 продолжает последний цикл счета. В де-, вятом состоянии счетчика импульс с выхода инвертора 13 появляется на выходе элемента И-НЕ 6 в виде короткого низкого уровня и устанавливает триггер 9 в единичное состояние, разрешающее под готовку коммутирующего триггера 15 дл переключения в нулевое ссютояние. В десятом состоянии декадного счетч на выходе элемента И-НЕ 7 в вникает короткий низкий уровень и триггер 9 воз вращается в нулевое состояние. В это ж время коммутирующий триггер 15 пере- ключается по С-входу в нулевое состояние и запирает вход элемента И-НЕ 1О. Короткий низкий уровень на выходе элемента И-НЕ 7, являющийся выходным, импульсом делителя,-инвертируется инве} тором 14 и поступает на вход элементов И-НЕ 11, В соответствии с кодовой комбинацией, поступающей с выходов кодирук щего устройства 16, на выходе элеман-тов И-НЕ 11 возникает короткий низкий уровень, который, воздействуя на. S,BXOA триггеров, устанавливает декадный счетчик 1 в исходное состояние. В реясиме работы делителя с коэффициентом деления первой декады N ±О постоянный низкий уровень, поступающий с кодирующего устройства 16 па К-вход коммутирующего трунгера 15, удерживает его в единичном состоянии. В декадный счетчик 1 при установке исходного состояния ничего не записывается. Связь между S -входом первого триггера и J -входом второгю триггера декадного счетчика исключает паразитное влияние состояния первого и четвертого тригеров во время установки исходного.состояния, в частности при записи кодовой комбинации 1001. Формула изобретения 1. Делитель .частоты с переменным коэффициентом деления, содержащий декадный счетчик, вход которого соединен с выходом элемента И-НЕ, первый вход которого подключен к клемме йсаочника входного сигнала, а второй вход - к выходу коммутирующего триггера, и две схемы фик- (Сации, отличающийся тем, что, с целью упрощения устройства, каждая схема фиксации выполнена на двух элементах И-НЕ и триггере, причем одНи из входов элементов И-НЕ первой схемы фиксации соединены с клеммой источника входного сигнала чер.ез последовательно соединенные инвертор и элемент , один из входов элементов И-НЕ второй схемы фиксации поДключеш; к клемме источника входного сигнала через инвертор, другие входы всех элементов И-НЕ схем фиксации подключены к выходам декадного счетчика; выходыэлементов И-НЕ каждой cxeMbj фиксации подключены к установочным входам соответствующего триггера, выход одного из которых, входящего во Ч. вторую схему фиксации, соединен с управляющим входом кoм fyтиJ5yющeгo триггера. 2. Делитель частоты по п, 1, отличающийся том,, что, с целью 5С)

повышения надежности работы устройства,чика coeuHneji с J -входом второго

5-вход первого триггера декадного счет-гера.

509909

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU606210A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1979 |

|

SU783996A1 |

| Делитель частоты следования импульсов | 1984 |

|

SU1181134A1 |

| Устройство для приема и передачи информации | 1983 |

|

SU1152014A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1980 |

|

SU900459A2 |

| Делитель частоты с дробным переменным коэффициентом деления | 1974 |

|

SU506130A1 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ИЗМЕНЯЕМЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1996 |

|

RU2134485C1 |

| Делитель частоты с изменяемым коэффициентом деления | 1983 |

|

SU1102044A1 |

Авторы

Даты

1976-04-05—Публикация

1974-08-27—Подача