Изобретение относится к устройствам импульсной техники и предназначено для использования в радиотехнической аппаратуре различного назначения, в частности в синтезаторах частот.

Известны программируемые делители частоты, или делители частоты .с переменным коэффициентом деления (ДПКД), предназначенные для использования в синтезаторах частот и других радиотехнических устройствах.

Из известных программируемых делителей наиболее близким по технической сущности к предлагаемому является делитель частоты с переменным коэффициентом де- ления, содержащий синхронный упра1аляе- мый декадный счетчик и блок автономной установки егхэ исходного состояния (Ij.

Блок автономной установки включает Д-триггер формирования импульсов установки и Д-триггбр запоминания разрешения, который с поступлением на его тактовый вход импульса установки от старшего каскада формирует и запоминает сигнал (Л.чюикния установки. Поскольку R

вход Д- риггера формирования импульсов установки соединен с тактовым входом каскада, то этот Д-триггер будет каждые полпериода сбрасываться в нулевое состояние, а с лед овательно длительность импульса установки не может быть больше длительности входных тактовых импульсов Выходные импульсы каждого каскада по этой причине так же близки по длительности к входным импульсам.

Оцнако в этом устройстве подготовка блока автономной установки в каскадах осуществляется перепадом напряжения на тактовом входе Д-триггера запоминания. Достаточно случайного всплеска в этой цепи, чтобы произошла ложная установка каскада или сбой в работе делителя.

Цель изобретения - повышение надежности в работе делителя.

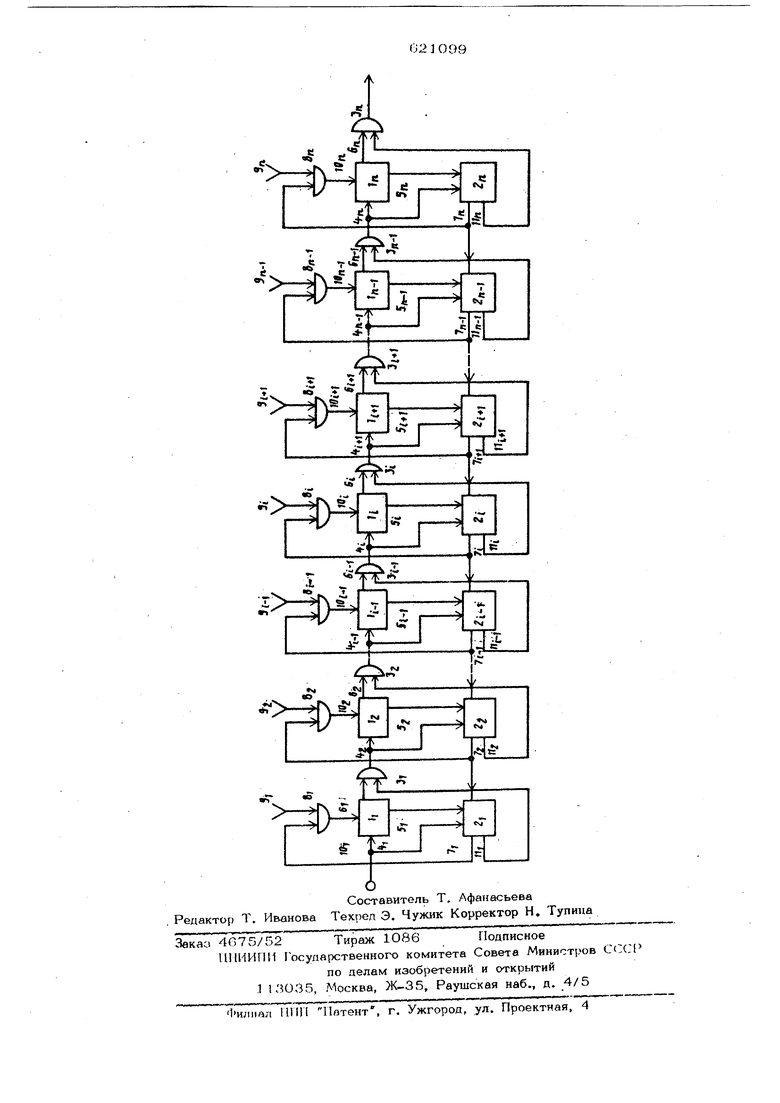

Для этого в программируемый делител частоты, содержащий rt каскадов, кажды из которых состоит из управляемого делителя, тактовый вход которого соединен с первым входом, блока автономной установки, первый выход - со вторым входом блока автономной установки, третий вход которого подключай к прямому Выходу блока автономной установки следую щего каскада и через эз емент совпадения, на второй вход которого подан управляющий сигнал - к ycTaHOBOjiHOMy вхо ду управляемого делителя, сцецующего каскада, в каждый каскад введен дополнительный элемент совпадения, первый вход которого подключен ко второму вых ду управляемого делителя частоты, второй вход - к инверсному выходу блока автономной установки. выход - к тактовому входу управляемого делителя час ты следующего каскада. На чертеже представлена структурная электрическая схема программируемого делителя частоты. Программируемый делитель частоты содержит И одинаковых каскадов, каждый из состоит из управляемого делителяij-г Ifj (например, декадного ти па), ; блока автономной установки исходного состояния управляемого делителя 1 И элемент совпадения I „ Входом каскада является такт вый вход 4j-4|Y управляемого делителя 1 i , а выходом - выход элемента совпаВыход 5|-5ff управляемог дения 3| д делителя 1 , представляет выход схёмь сквозного переноса кажйого Ш-го входного импульса управляемого делител для декадного управляемого делителя, например, Ht 1О). Выход 6« - 6 и управляемого делителя 1| есть выход триггера, формирующего фронт переноса с Ш -ым импульсом на входе. На этом выходе Деист вуют щирокие импульсы, например для декадного управляемого делителя, работающего в коде 1-2-4-8, длительность импульсов на этом выходе равна 211 ( для кольцевого делителя, работающего в. коде Джонсона, 5Тд(). Тактовый вход 4 соединен с одвходов блока автономной установ- ним из ки 2; , в то время как другие два его входа соединены с выходом 5 J и выходом блока автономной установки 2 j j еледующего каскада. Выход. , ц блока автономной установки 2 J через элементы совпауправляемые информадения 8j -8 У J - 9 к . соедит ционными входами к - с няется с установочными входами управляемого делителя 1 J. Инверсный выход 1 i j П бло на автономной установки 2 | соединен с одним из входов элемента совпадения 3 i , другой вход которого соединен с выходом 6{ управляемого делителя. . БТОК автономной установки 2 : содержит Д-триггер , 1 -вход которого соединен с тактовым входом делителя 1 , , информационный вход (Д-вход) соединен с выходом блока 2«| j следующего каскад р, а тактовый вход Д-триггера соединен с выходом 5 J , управляемого делителя 11 . Выход Д-триггера Q есть блока автономустановочный выход выход - инной установки 2 ) версный выход 11 j . Устройство работает следующим образом. Пусть требуется обеспечить коэффициент деления W. Для этого в делитель, максимальная, ёКисость ; которого равна rtt , необходимо записать число 2. крторое численно равно 2 . Тогда; с поступлением на вход делителя .W импульсов происходит заполнение делителя, и цикл деления завершается. Пусть Neoij Hf +Oi2Hi +,.. ...+ot„rtI -,, . где aj ,1,2,..., m-1 , тогда (itt-0ii)w(w-l-o(...(ж-lтa„)ln J т.е. в первый каскад записывается число, являющееся дополнением до Ш , в остальные - числа, являющиеся дополнением до № 1. , Наприк ер, для случая декадных делителей, когда rtt 10, при необходимости получить и 253 требуется три каскада деления. Максимальная емкость делителя равна , а Z lOOO-253s747, т.е. в первый каскад необходимо предварительно записать 7, во второй - 4, в третий - 7. Динамика работы делителя рассматривается на примере двухкаскадного декадного делителя для случая, когда N в младшем разряде содержит 1, логика работы декады 1-2-4-8, тактирук щим фронтом для триггеров декад является задний фронт тактового импульса, а для Д-триггеров передний, что соответствует практике. Цикл начинается c{.W -2)-го импульса. Его поступлению предшествует следующее состояние делителя: сигналы на выходах 7|«(1и , так как на Т -входе Дтриггера действует нулевой сигнал, сигнал на выходе 6 j равен сигналу на выходе 5. О , а поэтому сигнал аа входе ,на выходах , И, сигнал на выходе 6 1, поскольку делитель второго каскада находится в состоянии 9 {lo6l), следовательно, на входе 4- де лителя действует 1. , Как следует из рассмотренного соатояния, второй каскад готов к записи и кодного состояния, так как на выходе 7 всегда действует , а на выходе 5, 1 появляется с ближайшим тактоным импульсом на входе второго хаскада. Первый каскад ,к установке не готов, так как сигнал на выходе 7 -Х). С поступлением ( -2)-го тактового импульса на вход делителя на выходе б| появляется if которая передается элементом совпадения 31 , на вход 4л. . На Ы-входе Д-триггера блока 2 уста навливается , что дает возможность с поступлением на его тактовый вход им пульса перевести сигнал с выхода 7yi в состояние 1, а сигнал с выхода 11 в состояние О, Через время задержки в схеме сквозного переноса на выходе Sj появляется единичный перепад, который и осуществляет переброс Д-триг- гера в состояние Q 1,, т.е. начинается формирование импульса установки исходного состояния второго каскада, и одновременно появляется разрешение на формирование импульса установки первог каскада. Кроме того, переброс сигнала с выхода lljT в О .переводит сигнал -на .входе в О т.е. формирует конечный перепад на выходе делителл. Поскольку в управляемом делителе 1 2 импульсом установки записывается требуемое исходное состояние (например, 1010), то сигналы на выходах 6,j и 5 переходят в О. Таким образом, установка управляемого делителя 1 2 произошла, rio импульс установки продолжается, пока сигнал на входе 4 л г и тем самым удерживаег в готовности блок 21 . . С приходом переднего фронта М импульса на -1 -входе Д-триггера блока I автономной установки появляется 1 , , и разрешает перевод Д-триггера в состояние Q 1, Q О. На выходе 7 формируется импульс установки первого каскада, который через элемент совпадения 8i записывает исходное состояни в ут1равляемый делитель 1. . Как было условлено вначале, рассматривается наиболее неблагоприятный случай, т.е. когда в младшем разряде N содержится единица, поэтому в управляемом делител 1 I должно быть записано число 9 (iOOl). Поскольку перед записью исходного состоя{гая управляемый делитель 1 I был в состоянии 9, то оно подтв ждается импульсом установки, т.е. сигна а выходе 6 i остается равным 1 . ереход сигнала на выходе llj в О риводит к переходу сигнала на входе в О. Этим перепадом оканчивается оследний в цикле деления ; тактовый мпульс на входе второго каскада, сигнал на выходе 7 переводится в О и снимает разрешение формирования импульса установки первого каскада. С окончанием N -го тактового импульса на входе первого каскада наТ -входе Д-триггера блока 2 автономной установки появляется О, обрывает импульс установки, т.е. сигнал на выходе 7,0, а сигнал на выходе Ц| 1. В результате сигнал на входе 42 равен , начинается очередной, первый в новом цикле деления тактовый импульс на входе второго каскада. С появлением на входе делителя пер вого импульса нового цикла, поскольку упг равляемый делитель 1 остался в состоянии Э, на выходе 5 снова появляется импульс, но он не приводит к формированию импульса установки, так как разрешение на установку было снято с приходом предыдущего N -го импульса. Кроме того, первый импульс цикла устанавливает управляемый делитель 1. в нулевое состояние, т.е. сигнал на входе 6j переходит в О и тем самым через элемент совпадения 3 заканчивает первый тактовый импульс на входе второго каскада, осуществив перенос единицы в старший разряд. Поскольк на выходе 11 . до следуюшбй установки, т.е. до окончания цикла деления, остается , то элемент совпадения 3 1 будет повторять на своем выходе импульсы, поступающие с выхода равные по длительности STg (для выбранной логики декад); при трехкаскадном делителе на входе третьего каскада они составили бы 2О Т и т.д. Длительность импульсов установки второй декады равна 1,5 Т- , на входе третьего каскада она бы составила ISTuj и т.д. Таким образом, длительность импульсов на тактовых и уст)ановочных входах каждой последующей декады возрастает, что снижает требования к их быстродействию и позволяет сделать их экономичными и миниатюрными. В рассмотренном случае минимальный временной интервал между двумя тактирующими фронтами на входе управляемого делителя 1 составляет 1,5 Т бднако из-за возникающей в блоке 2 задержки импульса установки первый тактирующий фронт оказывае1х;я накрыт этим импульсом, поэтому делитель 1на него не реагирует, и следовательно, минимальный временной интервал можно считать равным 3 Tj j т.е. длительност импульсов на тактовых и установочных вхидах каждого следуканего каскада расширяется, а действие пар импульсов на и входах устраняется за счет накрытия одного из тактирующих фронтов импульсо установки исходного состояния. Это суще ственно снижает требования к быстродей ствию каждого следующего каскада и позволяет выбрать для их построения более маломощные и миниатюрные элемент Наибольшим требуемым быстродействием должен обладать только первый каскад. Выигрыш по энергопотребленшо уу , который может быть получен в предлагаемой схеме по сравнению с прототипом, составляет / 1 о к. число каскадов делителя; i коэффициент расширения так товых и тульсов на выходах последующих декад {к l),j -f - номер каскада. Как видно из приведенного выще анализа работы делителя, сигналом разрешения установки каждого каскада является единичный потенциал на информацион ном входе Д- григгера его блока 2 j , а формирование импульса установки проис ходит, если при этом на тактирующий вход Д-триггера поступает HNmynbc с выхода 5 j делителя 1 Совпадение м мента появления помехи на информационном входе с моментом прихода тактирующего фронта имеет значительно меньшую вероятность, чем поя.-лекие помехи на рвзрушаюшем входе в произвольный момент времени. Поэтому блок автономной установки, а следовательно, и вся схема программируемого делителя, обладает более высокой помехоустойчивостью по сравнению с прототипом. Формула изобретения Программируемый делитель частоты, содержащий Г( каскадов, каждый из которых состоит из управляемого делителя, тактовый вход которого соединен с первым вхоом блока автономной установки, первый выход - со Вторым входом блока автономной установки, третий вход которого подключен к прямому выходу блока автономной установки следующего каскада и через элемент совпадения, на втсрой вход которого подан управляющий сигнал гк установочному входу управляемо делителя следующего каскада, отличаю щ и и с я тем, что, с целью повышения надежности в работе делителя, в каждый каскад введен дополнительный элемент совпадения, первый вхоД которого подключен ко второму выходу управляемого делителя частоты, второй вход - к инверсному выходу; блока автономной установки, а выход - к тактовому входу управляемого делителя частоты следующего каскада. Источники информации, принятые вг внимание при экспертизе: 1. Патент Франции № 2176253 кл. Н 03 23/ОО, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый делитель частоты | 1977 |

|

SU696611A2 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1140248A1 |

| Программируемый делитель частоты | 1979 |

|

SU799145A2 |

| Программируемый делитель частоты | 1980 |

|

SU871340A2 |

| Цифровой измеритель частоты | 1980 |

|

SU938187A1 |

| Управляемый делитель частоты | 1975 |

|

SU563728A1 |

| Триггерное устройство | 1971 |

|

SU437225A1 |

| Устройство для акустического каротажа | 1971 |

|

SU443349A1 |

| Способ вывода информации с фазоимпульсным представлением чисел и устройство для его осуществления | 1977 |

|

SU690432A1 |

| Делитель частоты с переменным коэффициентом деления | 1986 |

|

SU1328937A1 |

Авторы

Даты

1978-08-25—Публикация

1975-12-29—Подача