I .

Изобретение относится к области гибридной вычислительной техники, а именно к функциональным преобразователям кода в проводимости.Известен функциональный преобразо- ватель кода в проводимость, содержащий проводимости, операционные усилители, цифровые управляемые проводимости и логические схемы JlJ .

В этом преобразователе при преобразовании последовательного кода в проводимость невозможна реализация немонотонных функциональных зависимосте так как в них проводимости йзвешены в соответствии с кодом.

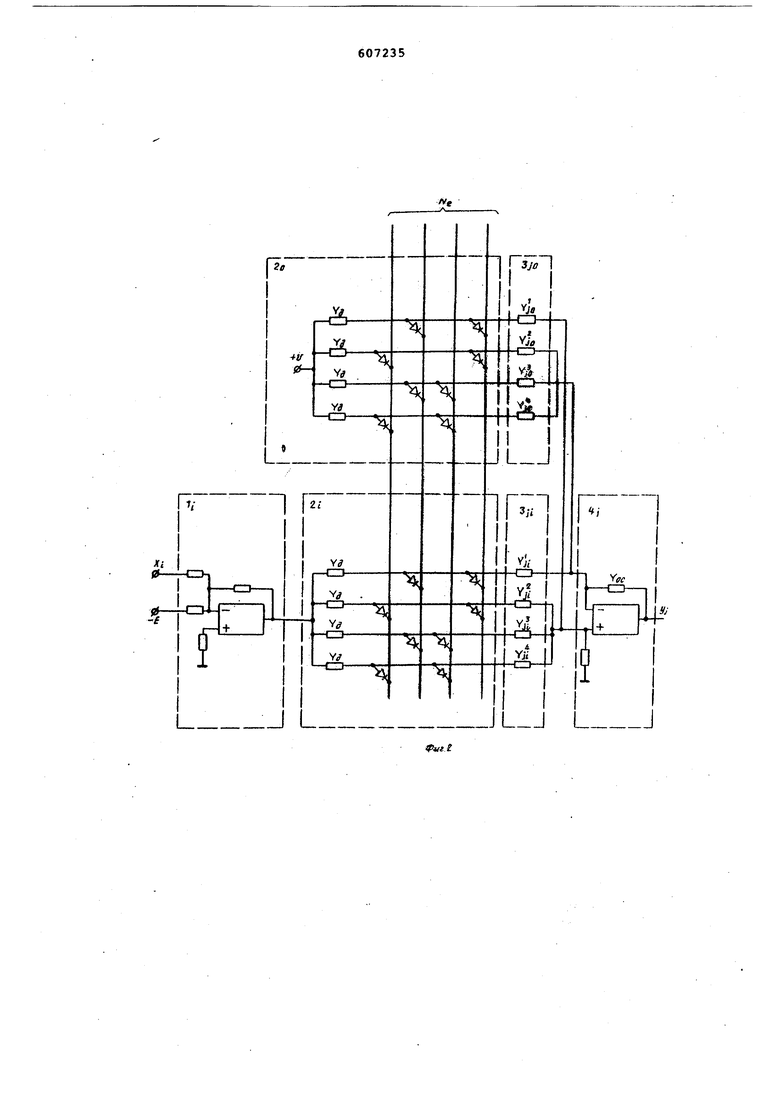

Нгшболее близким техническим решением к изобретению является функциональный декодирующий преобразователь, который, как и данный преобразователь содержит щ входных операционных усилителей, одни из входов которых подключены к источнику напряжения смещения, а другие являются соответствующими аналоговыми входами преобразователя, и и выходных операционных усили телей, входы каждого из которых подсоединены к выходам И1 рабочие резистивных матриц j .

Однако в зтом преобразователе при последовательном коде также невозможна реализация немонотонных зависимостгей (нащэимер, еЫк, где О ). кроме того, при модуляции кодом знакопеременных сигналов в таком преобразователе требуются двусто ронние транзисторные ключи, что приводит к удвоению общего числа транзисторов. Поэтому использование известного устройства в качестве многоканального преобразователя кода в недиагональную функциональную матрицу проводимостей ведет к сложной схемной реализации, вследствие чего значительно снижается надежность.

Целью данного изобретения являетсярасширение области применения.

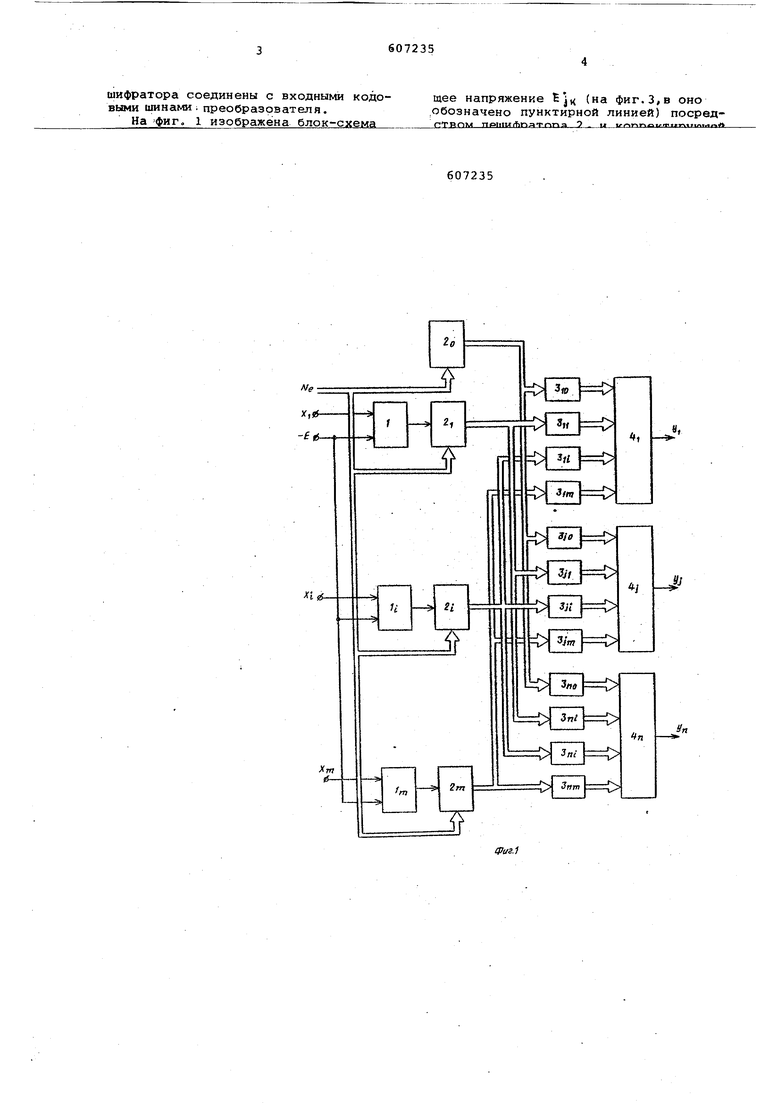

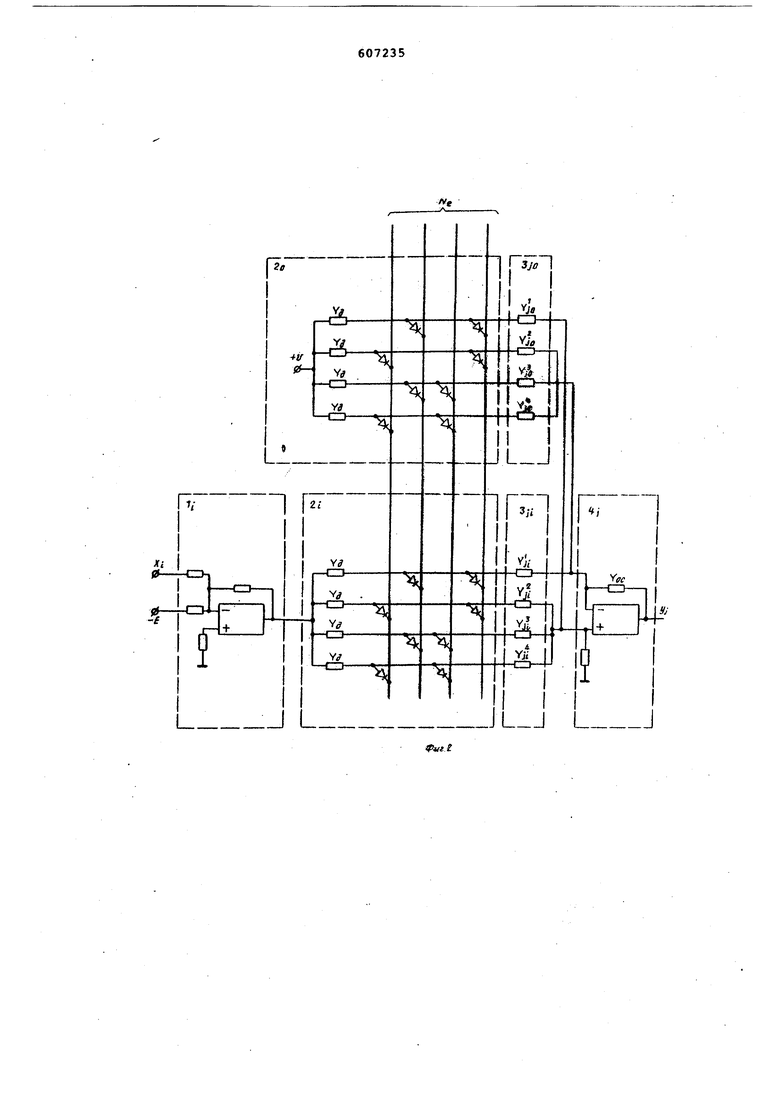

Это достигается тем, что предлагаемый преобразователь содержит W дешифраторов, информационные входы которых подключены к выходам соответствующих входных операционных усилителей, и М корректирующих резистивных матриц, входы которых подключены к выходам дополнительного дешифратора, а выходы подсоединены к входам соответствующих выходных операционных усилителей, входы рабочих резистнвных матриц подключены к выходам соответствующих дешифраторов, управляющие входы которых и управляющий вход дополнительного дешифратора соединены с входными кодовыми шинами: преобразователя.

На фиг. 1 изображена блок-схема

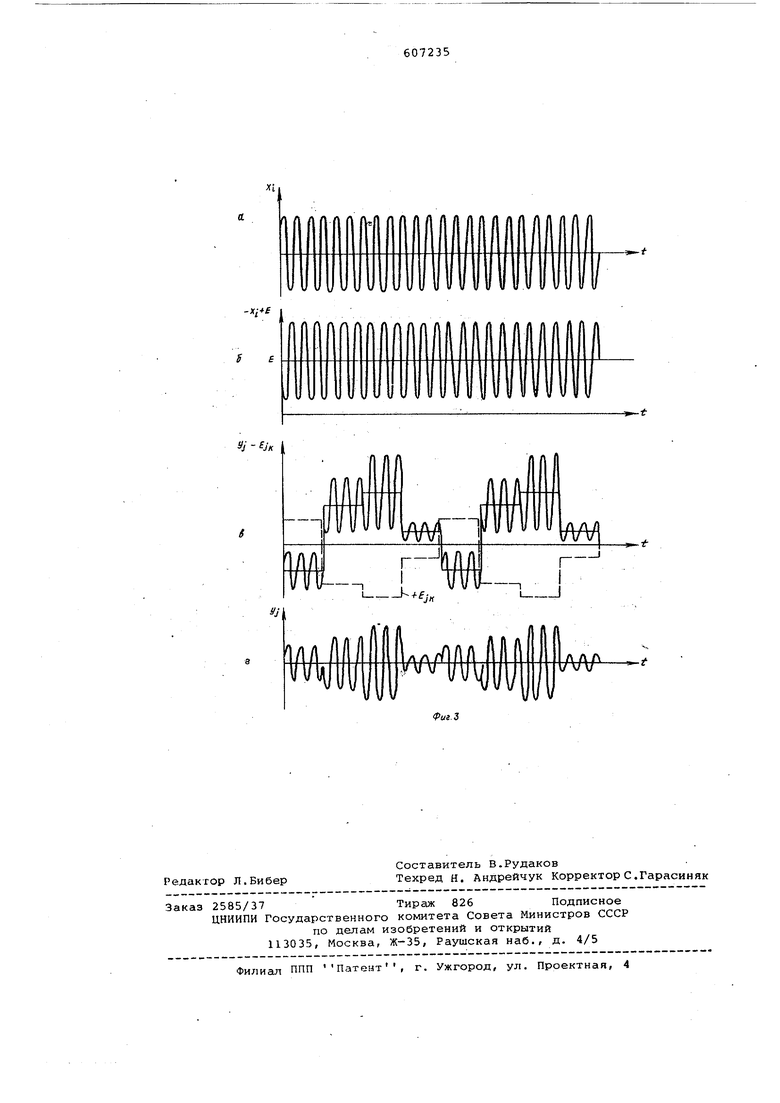

щее напряжение (на фиг.3,в оно ,обозначено пунктирной линией) посредПТИПМ ПР|1|мД1Пятгм-1а о „ ,л

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДАВЛЕНИЯ И ОЦЕНКИ РЕГУЛИРОВОЧНЫХ ПАРАМЕТРОВ | 1999 |

|

RU2167401C2 |

| ЭЛЕКТРИЧЕСКИЙ ИМИТАТОР СТАЦИОНАРНОГО ПЛАЗМЕННОГО ДВИГАТЕЛЯ | 2024 |

|

RU2830092C1 |

| Экспоненциальный декодирующий преобразователь | 1984 |

|

SU1160448A1 |

| Функциональный преобразователь | 1990 |

|

SU1772808A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1374431A1 |

| Преобразователь двоичного кода в двухполярное напряжение | 1981 |

|

SU980274A1 |

| Преобразователь кода в сопротивление | 1986 |

|

SU1381712A1 |

| Преобразователь угловых перемещений в код | 1982 |

|

SU1035627A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОДОВОЙ ОТРИЦАТЕЛЬНОЙ ОБРАТНОЙ СВЯЗЬЮ | 1994 |

|

RU2093956C1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

А/е

607235

Jj

Ип

с

-e

yj

yj - h

Авторы

Даты

1978-05-15—Публикация

1976-04-21—Подача