кого регулирования зона нечувствительности и гистерезис приводят к автоколебаниям, понижению чувствительности и становятся непреодолимым препятствием для повышения точности системы.

Цель изобретения - устранение зоны иечувствительности и гистерезиса регулировочной характеристики, т.е. повышение ее линейности, при реверсироваинн выходного напряжения.

Для этого в трехфазный статический преобразователь постоянного напряжения в ггеременное введены связанные между собой триггерный фазорасщепитель, два управляющих вывода, двухтактные транзисторные инверторы по числу фаз с предварительными усилителями и блоки упр авлення последними, один из которых нереверсируемый, а два других, принадлежащих реверсируемым фазам, состоят каждый из десяти элементов И, четырех элементов «Запрет и двух элементов ИЛИ.

Одноименные выходи первого и второго, второго н третьего, первого и третьего триггеров фазорасщепателя попарно подключены ко входам cooraeTCTBeKfio первого и второго, третьего и четвертого, njiToro п шестого элементов И, выходы первого н второго элеме 1тсв И соединены со вторыми входами соответственно первого н второго элел ентов «Запрет и с

одним из входов седьмого и восьмого ЗЛСМС тов и, выходы которых подключены к первым выходам упомянутых элементов «Запрет и ко входам соответственно второго н первого эле.ментоа ИЛИ, а вторые входы элементов И подсоединены к одному из уПраВЛЯ О ЦКХ ВЫ ЗОДОВ,

выходы пятого и шестого элементов И совдииеиы со вторыми входами соответстве1жо третьего и четвертого элементов «Запрет и с одним .из входов девятого и десятого элементов, выходы которых подключены к первым входам указанных элементов «Запрет и ко входам соответственно второго и первого элементов ИЛИ, вторые входы элементов И соединены с другим управляющим выводом, а выходы первого, третьего и второго, четвертого элементов «Запрет присоединены ко входам соответствепно первого и второго элементов ИЛИ, ко входам которых кроме того подсоединены выходы соответственно третьего и четвертого элементов И, а выходы элементов ИЛИ подключены ко входам предварительных усилителей.

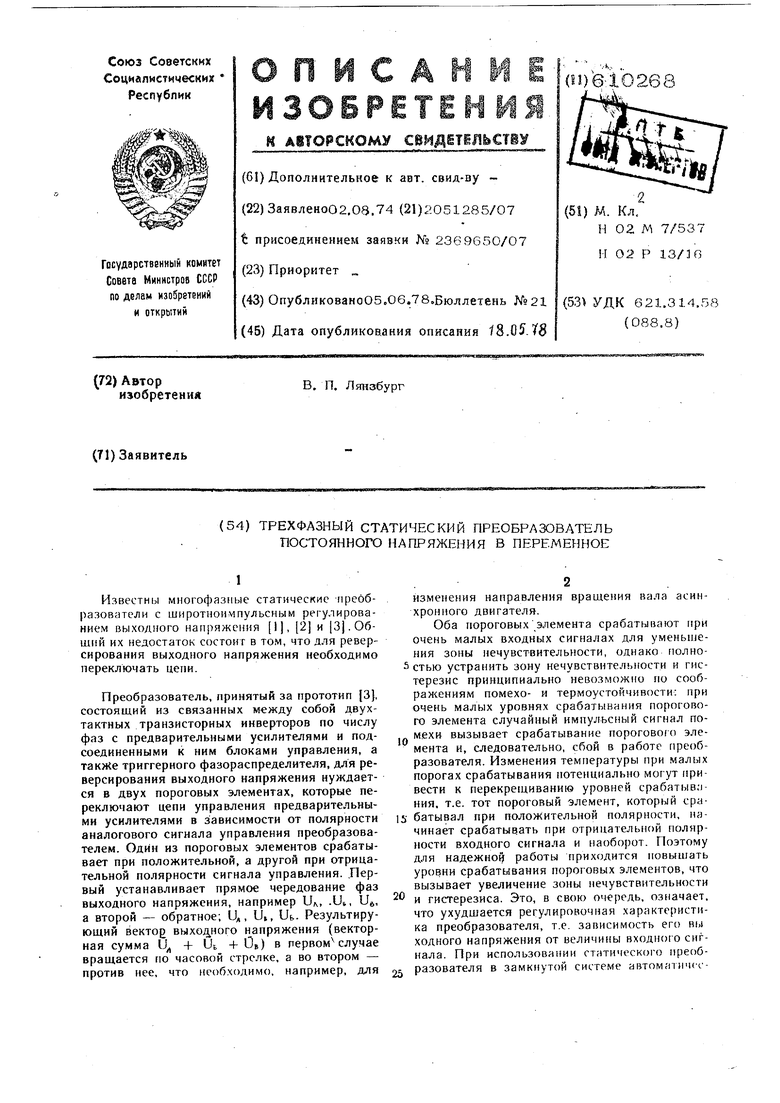

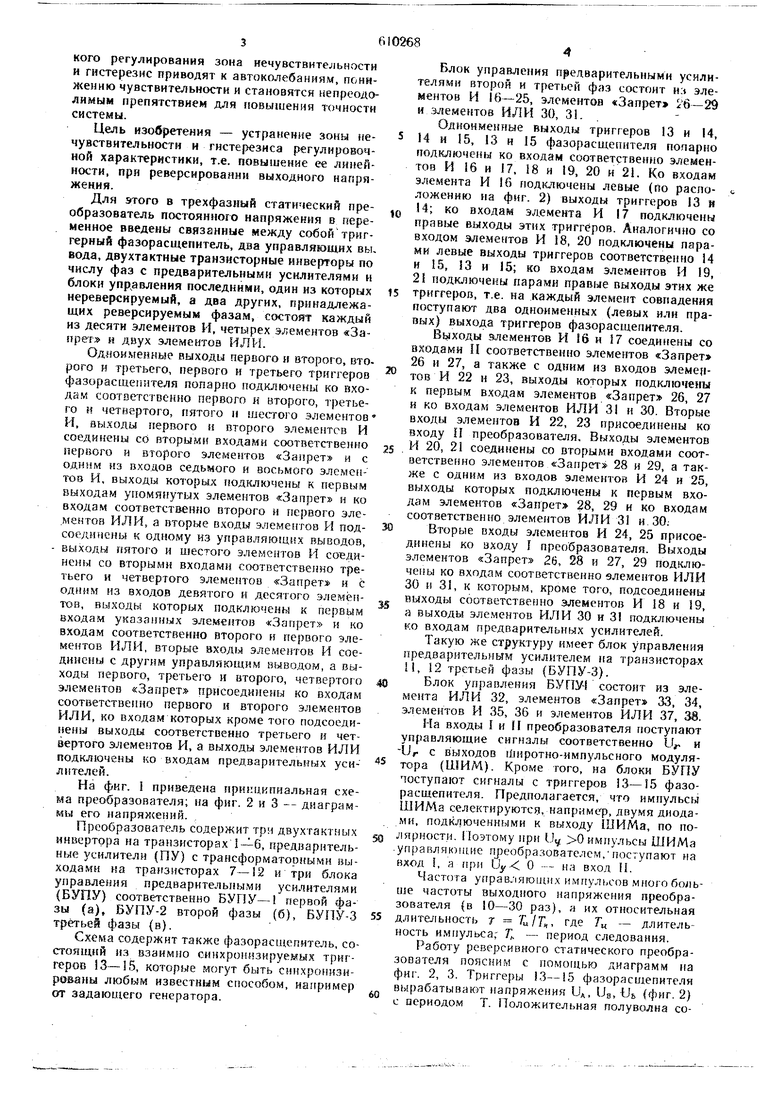

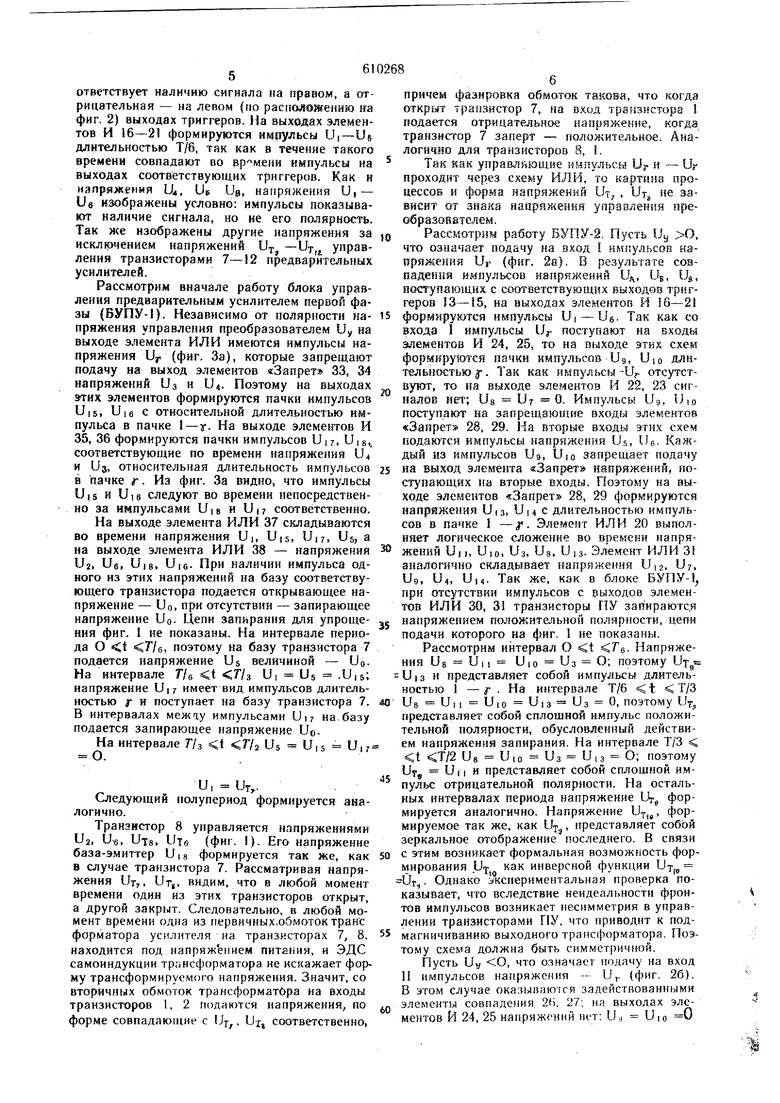

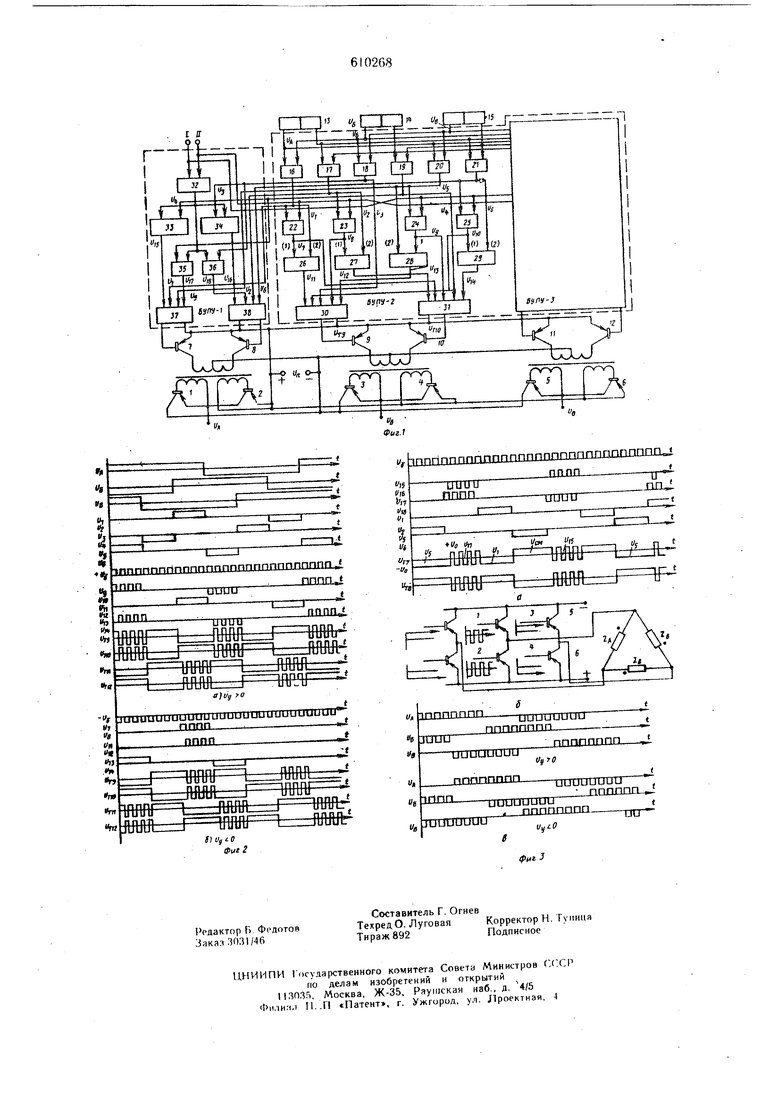

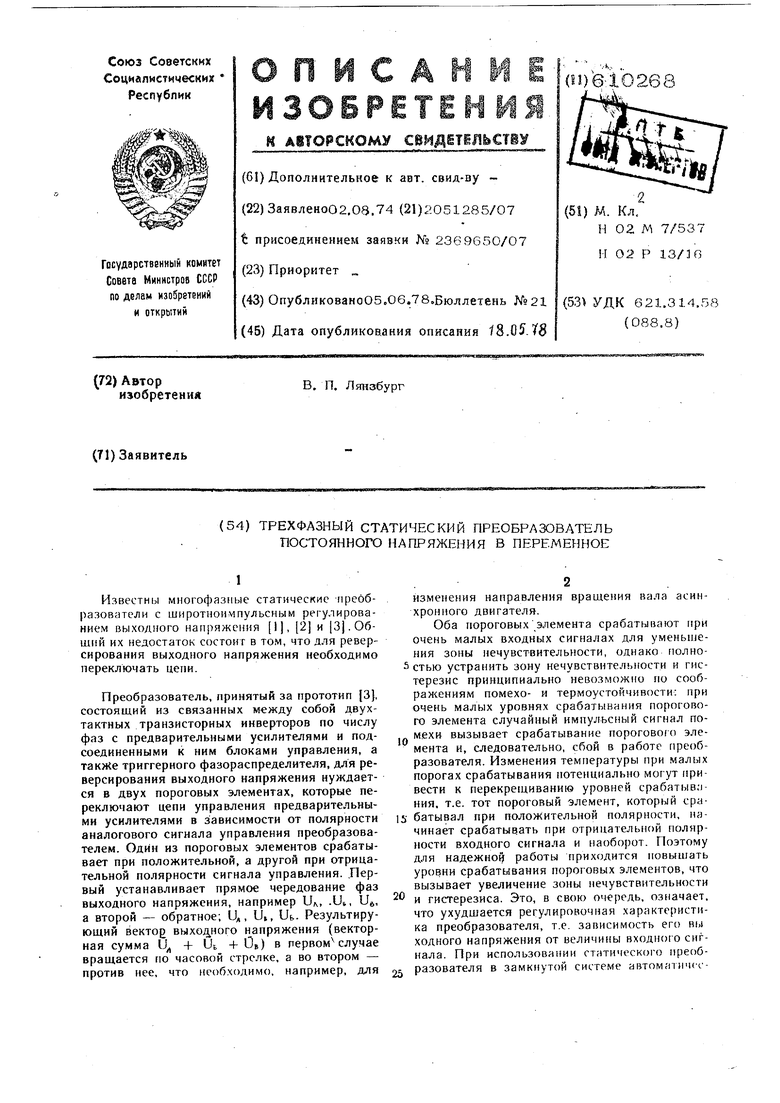

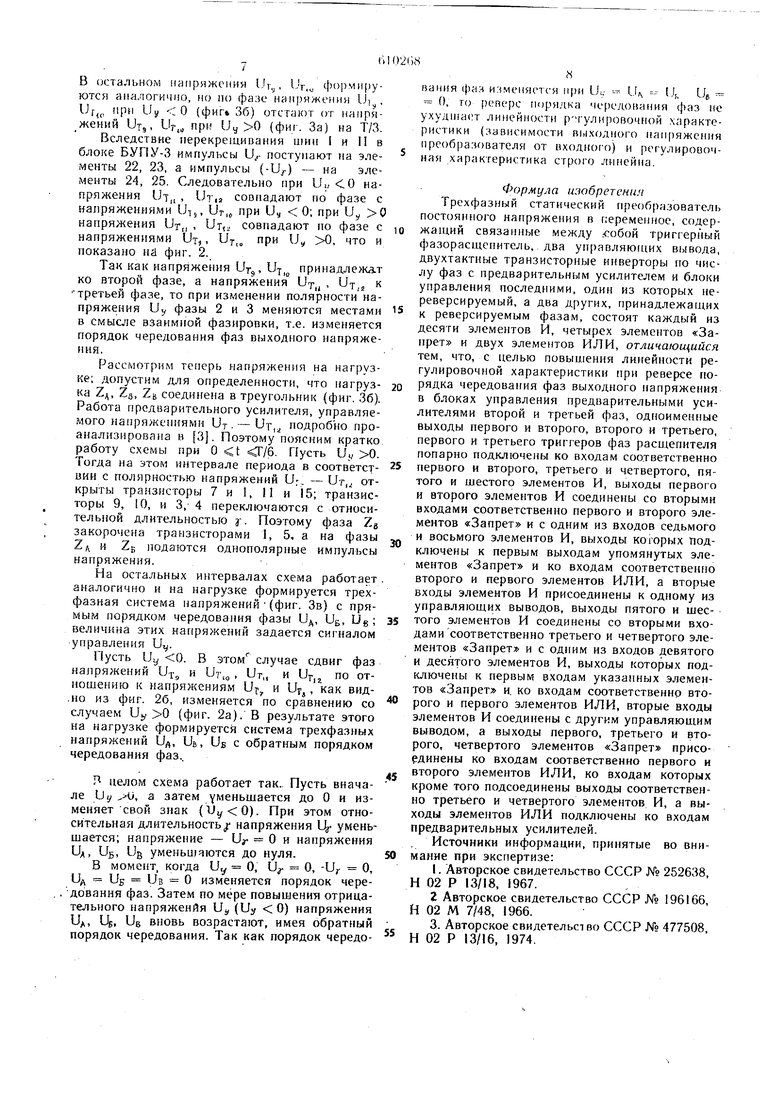

На фиг. приведена принципиальная схема преобразователя; на фиг. 2 и 3 - диаграммы его напряжений.

Преобразователь содержит три двухтактных инвертора на транзисторах 1-6, предварительные усилители (ПУ) с трансформаторными выходами на транзисторах 7-12 и три блока управления предварительными усилителями (БУПУ) соответственно БУПУ-I первой фазы (а), БУПУ-2 второй фазы (б), БУПУ-3 третьей фазы (в).

Схема содержит также фазорасщепитель, состоящий из взаимно синхронизируемых триггеров 3-15, которые могут быть синхронизированы любым известным способом, иаггример от задающего генератора.

Блок управления предварительными усилителями второй и третьей фаз состоит и: элементов И 16-25, элементов «Запрет 26-29 и элементов ИЛИ 30, 3. .

Одноименные выходы триггеров 13 и 14, 14 и 15, 13 и 15 фазорасщепнтеля попарно подключены ко входам соответственно элементов И 16 и 17, 18 и 19, 20 и 21. Ко входам элемента И 16 подключены левые (по расположению на фиг. 2) выходы триггеров 13 и 14; ко входам эдемента И 17 подключены правые выходы этих триггеров. Аналогично со входом элементов И 18, 20 подключены парами левые выходы триггеров соответствепно 14 и 15, 13 и 5; ко входам элементов И 19, 21 подключены парами правые выходы этих же 5 триггеров, т.е. на каждый элемент совпадения поступают два одноименных (левых или правых) выхода триггеров фазорасщепителя.

Выходы злементов И 16 и 17 соединены со входами М соответственно эле ентов «Запрет 26 и 27, а также с одним из входов элемеятов И 22 н 23, выходы которых подключены к первым входам элементов «Запрет 26, 27 и ко входам элементов ИЛИ 31 и 30. Вторые входы элементов И 22, 23 присоединены ко входу и преобразователя. Выходы элементов И 20, 21 соединены со вторыми входами соотBCTCTBeFiHO элементов «Запрет 28 и 29, а также с одним из входов элементов И 24 и 25, выходы которых подключены к первым входам элементов «Запрет 28, 29 н ко входам соответственно элементов ИЛИ 3 и. 30;

Вторые входы элементов И 24, 25 присоединепы ко входу { преобразователя. Выходы элементов «Запрет 26, 28 и 27, 29 подключены ко входам соответственно элементов ИЛИ 30 и 31, к которым, кроме того, подсоединены выходы соответственно элементов И 18 и 19, а выходы элементов ИЛИ 30 и 31 подключены ко входам предварительных усилителей.

Такую же структуру имеет блок управления гфедварительинм усилителем ira транзисторах 1, 2 третьей фазы (БУПУ-З).

Блок управления БУПУ- состоит из элеме {та ИЛИ 32, элементов «Запрет 33, 34, элементов И 35, 36 и элементов ИЛИ 37, 38.

На входы I и И преобразователя поступают управляющие сигналы соответственно U,- и -Ur с выходов ниротно-импульсного модулятора (ШИМ). Кроме того, на блоки БУПУ поступают сигналы с триггеров 13-15 фазорасщепителя. Предполагается, что импульсы ШИМа селектируются, например, двумя диодами, подключенными к выходу ШИМа, по полярности. ГIoэтo fy при Uy 0 импульсы ШИМа .управляющие преобразователем,поступают на вход I, а при Uy О --- на вход il.

Частота управляющих импульсов много больше частоты выходного напряжения преобразователя (в 10-30 раз), а их относительная длительность г , где Тц - длительность импульса, Т - период следования.

Работу реверсивного статического преобразователя поясним с помощью диаграмм на фиг. 2, 3. Триггеры 3-15 фазорасщепителя вь рабатывают напряжения UA, Ug, (фиг. 2) с периодом Т. Положительная полуволна соответствует наличию сигнала на правом, а отрицательная - на левом (по расположений} ira фиг. 2) выходах триггеров. На выходах элементов И 16-21 формируются надпульсы U,-Ue длительностью Т/6, так как в течение такого времени совпадают во времени импульсы на выходах соответствующих триггеров. Как и напряжения Ц,, UB Ug, напряжения U,- Ua изображены условно: импульсы показывают наличие сигнала, но не его полярность. Так же изображены другие напряжения за исключением напряжений U. -UT, управления транзисторами 7-12 предварительных усилителей. Рассмотрим вначале работу блока управления предварительным усилителем первой фазы {БУПУ-1). Независимо от полярности напряжения управления преобразователем Uy на выходе элемента ИЛИ имеются импульсы напряжения Uy (фиг. За), которые запрещают подачу на выход элементов «Запрет 33, 34 напряжений Ua и U4. Поэтому на выходах этих элементов формируются пачки импульсов и 15, Ui6 с относительной длительностью импульса в пачке 1-у. На выходе элементов И 35, 36 формируются пачки импульсов Ui/, Ui8, соответствующие по времени напряжения U4 и Ug, относительная длительность импульсов в пачке г. Из фиг. За видно, что импульсы Ui5 и Ui6 следуют во времени непосредственно за импульсами Uis и Ui соответственно. На выходе элемента ИЛИ 37 складываются во времени напряжения Uj, Uis, Ui, Us, a на выходе элемента ИЛИ 38 - напряжения U2, Ue, U|8, Ui6. При наличии импульса однего из этих напряжений на базу соответствующего транзистора подается открывающее напряжение - Uo, при отсутствии - запирающее напряжение UQ. Цепи запирания для упрощения фиг. 1 не показаны. На интервале периода О t 7/б, поэтому на базу транзистора 7 подается напряжение Us величиной -- Uo. На интервале Tie t Г/з U, Us .U,5; напряжение Ui7 имеет вид импульсов длительностью г и поступает на базу транзистора 7. В интервалах межау импульсами Usy на.базу подается запирающее напряжение Uo. На интервале Г/з t 772 Us Uis U,7 U, Uv Следующий полупериод формируется аналогично. Транзистор 8 управляется напряжениями Uj, U-s, Uie (фнг. I). Его напряжение база-эмиттер U,8 формируется так же, как в случае транзистора 7. Рассматривая напряжения UT, , UT,, видим, что в любой момент времени один из этих транзисторов открыт, а другой закрыт. Следовательно, в любой момент времени одна из первичных.обмоток транс форматора усилителя на транзисторах 7, 8, находится под напряжеиием питания, и ЭДС самоиндукции трансформатора не искажает форму трансформируемого напряжения. Значит, со вторичных обмоток трансформатора на входы транзисторов 1, 2 подаются нaпpяжeния по форме совпадающие с U,, Ui, соответственно, причем фазнровка обмоток такова, что когда открыт транзистор 7, на вход транзистора 1 подается отрицательное напряжение, когда транзистор 7 заперт - положительное. Аналогично для транзисторов 8, 1. Так SBK управляющие импульсы U и - Ur проходнт через схему ИЛИ, то картина процессов и (|юриа напряжений UT , Utg не зависит от знака напряжения упрззлення преобразователем. Рассмотрим работу БУПУ-2, Пусть Uy О, что оз5 ачает подачу на вход i импульсов наоряження Uy (фиг. 2а). В результате совпадения импульсов напряжений Од, Llg, Ug, поступающих с соответствующих выходов триггеров 3-15, на выходах элементов И }6--21 формируются (шпульеы U| -Ug. Так как со входа 1 импульсы U поступают на входы элементов И 24, 25, то на выходе этих схем формируются пачкн импульсов Ug, Uio длительностью 3. Так как нп пульсы-Uj- отсутствуют, то на выходе элеглентов И 22, 23 сигналов нет; Us - и/ 0. Импульсы Us, Uio поступают на запрещающие входы элементов «Запрет 28, 29. На вторые входы этих схем гюдаются импульсы напряжения Us, Ug. Каждый из импульсов Ug, UJQ запрещзет подачу на выход элемента «Запрет напряжений, поступающих на вторые входы. Поэтому на выходе элементов «Запрет 28, 29 формируются напряжения Uss, UM с длительностью импульсов в пачке I -у. Элемент ИЛИ 20 выполняет логическое сложение во времени напряжений Un, UIQ, Uj, Us, U|3. Элемент ИЛИ 31 аналогично складывает напряжения U|2. U, Ug, Ui, и 14- Так же, как в блоке БУПУ-1, при отсутствии импульсов с рыходов элементов ИЛИ 30, 31 транзисторы ПУ запираются напряжением положительной полярности, цепи подачи которого на фнг. 1 не показаны. Рассмотрим интервал О t 7б. Напряжения Ug U| 1 Uio Us О; поэтому Uf Ui3 и представляет собой импульсы длительностью 1 -f. На интервале Т/6 t Т/3 Ue Un Uio Uis Us 0, поэтому UT представляет собой сплошной импульс положительной полйрности, обусловленный действием напряжения запирания. На интервале Т/3 t Т/2 Ug Uio Ua Ui3 О; поэтому y.j. Un и представляет собой сплошной импульс отрицательной полярности. На остальных интервалах периода напряжение УГ формируется аналогично. Напряжение U., формируемое так же, как U.,, 1тредставляет собой зеркальное отображение последнего. В связи с этим возникает формальная юзможность формирования U как инверсной функции UT Однако экспериментальная проверка поназывает, что вследствие неидеальности фронч в импульсов возникает несимметрия в управлении транзисторами ПУ, что приводит к подгяагничиванию выходного трансформатора. Поэтому схема должна быть симметричной. Пусть Uy О, что означает подачу на вход II импульсов напряжс.чия - U (фиг. 26). В этом случае оказываются задействованными элементы совпадения 2Н. 27; на выходах элементов И 24, 25 напряж(м)нй шт: Uj Uio 0

остальном напряжения , IJr. ф()рми)утсл аналогично, но по фазе нанряженнн Ui,.,,

Ur(, при Uy 0 (фиг 36) отстакуг от напряжений UT,, UT., при Uy 0 (фиг. За) на Т/3.

Вследствие перекрещивания шин I и И в блоке БУПУ-3 импульсы поступают на эле- менты 22, 23, а импульсы () - на элементы 24, 25. Следовательно при U 0 напряжения UT,, , Uria совпадают по фазе с напряжениями Utj, Ur,,, при U., 0; при Uy 0 напряжения Ur,, , UT,. совпадают по фазе с ,о напряжениями От,, UT,O Р -; что показано на фиг. 2.

Так как напряжения Ur,, Uj, принадлежат ко второй фазе, а напряжения UT-. , UT, к Третьей фазе, то при изменении полярности напряжения Uy фазы 2 и 3 меняются местами 15 в смысле взаимной фазиропки, т.е. изменяется порядок чередования фаз выходного напряжения.

Рассмотрим теперь напряжения на нагрузке; допустим для определенности, что нагруз- 20 ка Z, Zg, ZB соединена в треугольник (фиг. 36). Работа предварительного усилителя, управляемого напряжепиямн UT. - UT,,, подробно проанализирована в 3. Поэтому поясним кратко работу схемы при О t Г/6. Пусть {.h, 0. Тогда на этом интервале периода в соответст- 25 ции с полярностью напряжений Ur.. - Ur, открыты транзисторы 7 и 1, II и 15; транзисторы 9, 10, и 3, 4 переключаются с относительной длительностью Поэтому фаза Zg закорочена транзисторами 1, 5., а на фазы у. Zд и Zj подаются однополярные импульсы напряжения.

На остальных интервалах схема работает. аналогично и на нагрузке формируется трехфазная система напряжений (фиг. Зв) с прямым порядком чередования фазы U, UB, Ug ; 35 1еличина этих напряжений задается сигналом управления U.

Пусть Uy 0. Б этом случае сдвиг фаз напряжений U-i-,, и Ui , UT,, и UT по отношению к напряжениям Uf, и Ur, как видио из фиг. 26, изменяется по сравнению со случаем Uy 0 (фиг. 2а). В результате этого на нагрузке формируется система трехфазных напряжений Од, UB, UH с обратным порядком чередования фаз..

Г1 целом схема работает так. Пусть значале и у 0, а затем уменьшается до О и изменяет свой знак (l)). При этом относительная длительность/ напряжения Цг- уменьшается; напряжение - Uj- О и напряжения ид, Ug, UB уменьшаются до нуля.50

В момент, когда U - О, О, -U,- О, UA UK UB О изменяется порядок чередования фаз. Затем по мере повышения отрицательного напряжения U (Uy 0) напряжения Уд, 1, UB вновь возрастают, имея обратный . порядок чередования. Так как порядок чередования фа.ч иг меняется при Uc -- U/x -- U,, U - 0, TO репере порядка чередования фаз не ухудниип- линейности р гулировочной характеристики (зависимости выходного напряжения преобразователя от входного) и регулировочная характеристика строго линейна.

Формула изобретена.

Трехфазный статический Г1реоб лзователь постоянного напряжения в переменное, содержащий связанные между .-собой триггерный фазорасщенитель, два управляющих вывода, двухтактные транзисторные инверторы по числу фаз с предварительным усилителем и блоки управления последними, один из которых нереверсируемый, а два других, принадлежащих к реверсируемым фазам, состоят каждый из десяти элементов И, четырех элементов «Запрет и двух элементов ИЛИ, отличающийся тем, что, с целью повышения линейности регулировочной характеристики при реверсе порядка чередования фаз выходного напряжения в блоках управления предварительными усилителями второй и третьей фаз, одноименные выходы первого и второго, второго и третьего, первого и третьего триггеров фаз расщепителя попарно подключены ко входам соответственно первого и второго, третьего и четвертого, пятого и шестого элементов И, выходы первого и второго элементов И соединены со вторыми входами соответственно первого и второго элементов «Запрет и с одним из входов седьмого и восьмого элементов И, выходы когорых подключены к первым выходам упомянутых элементов «Запрет и ко входам соответственно второго и первого элементов ИЛИ, а вторые входы элементов И присоединены к одному из управляющих выводов, выходы пятого и шестого элементов И соединены со вторыми входами соответственно третьего и четвертого элементов «Запрет и с одним из входов девятого и десятого элементов И, выходы которых под слючены к первым входам указанных элементов «Запрет и. ко входам соответственно второго и первого элементов ИЛИ, вторые входы элементов И соединены с другим управляющим выводом, а выходы первого, третьего и второго, четвертого элементов «Запрет присординены ко входам соответственно первого и второго элементов ИЛИ, ко входам которых кроме того подсоединены выходы соответственно третьего и четвертого элементов И, а выходы элементов ИЛИ подключены ко входам предварительных усилителей.

Источники информации, принятые во внимание при экспертизе:

I. Авторское свидетельство СССР № 252638, Н 02 Р 13/18, 1967.

2 Авторское свидетельство СССР № 196166, Н 02 М 7/48, 1966.

3. Авторское свидетельство СССР № 477508, Н 02 Р 13/16, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вентильный двигатель | 1975 |

|

SU692013A1 |

| Устройство для температурной защиты электродвигателя | 1981 |

|

SU970543A1 |

| Преобразователь постоянного напряжения в трехфазное квазисинусоидальное | 1984 |

|

SU1166245A1 |

| Преобразователь трехфазного переменного напряжения в переменное для систем бесперебойного электропитания | 1987 |

|

SU1495907A1 |

| Телемеханическая система | 1984 |

|

SU1251147A1 |

| Способ преобразования напряжения в код и устройство для осуществления | 1983 |

|

SU1181143A1 |

| Широтно-импульсный преобразователь | 1986 |

|

SU1413715A1 |

| Устройство для измерения симметричных составляющих напряжений трехфазной сети | 1978 |

|

SU765760A1 |

| Устройство для управления электромагнитным вибровозбудителем питателя | 1984 |

|

SU1177235A1 |

| Устройство для формирования сигнала угла поворота вала | 1980 |

|

SU905969A1 |

Авторы

Даты

1978-06-05—Публикация

1974-08-02—Подача