Изобретение относится к области автоматики и вычислительной .техники и мо-г жех быть использовано для решения экономичбских, транспортных и других за|дач, моделируемых на сетях,.

Известны аналоговые модели, содержащие соединенные согласно топологии сети модели ветвей, а также подключенные к начальному и конечному узлам ис- точник тока и индикатор Ij.

Однако эти устройства не позволяют получить критический путь в виде документа.

Наиболее близкой по техническому решению является аналоговая модель транспортной сети, содержащая соединенные между собой согласно топологии сети ветви, каждая из которых состоит из последовательно включенных газоразрядных приборов, источник тока и индикатор, соедиленныё параллельно и подключенные к начальному и конечному узлам соединения ветрей, а также блок кодирования, выход которого соедине со входом блока регистрации .

Целью изобретения является расширение функциональных возможностей аналогск вой модели.

Для достижения этой цели в аналоговую модель дополнительно введены по количеству ветвей блоки определения состояния ветви, соединенные между собой информационными входами согласно Tont логии сети, причем управляющий вход каждого из блоков определения состояния ветви подключен к соответствующей ветви, а выход связан с соответствующим входом блока кодирования, причем блок опредепения состояния вегви содержит входной трансформатор, дифференцируещий усилитель, элемент памяти, элемент И, элемент задержки и две пары диодов, причем первичная обмотка входного трансформатора является управляющим входом блока определения состояния ветви, а вторичная обмотка входного трансформатора подключена ко входу дифференцирующего усилителя, выход которого через элемент памяти соединен с первым входом элемента И, ко второму входу которого подключен

катоды первой парыдиодов| аноды кото| ых соответстеенво соедвнеиы с иыформа ционвымв входами блока определения сос1тояшш ветви, а выход ааемевта И соед нен с еьгходом блока шфеделеввя состо% ВИЯ еетвг, а БЬ1ход оаемек а. И соединен |С шйходоы баока опредепенвя состояния ввтв0 и со входом аяекюнта задержки, Jшxoд которого подюшчен к анодам вто f№& оары дврдов, катотл которых соот ветственвв соединены с анодами первой .вары диодов.

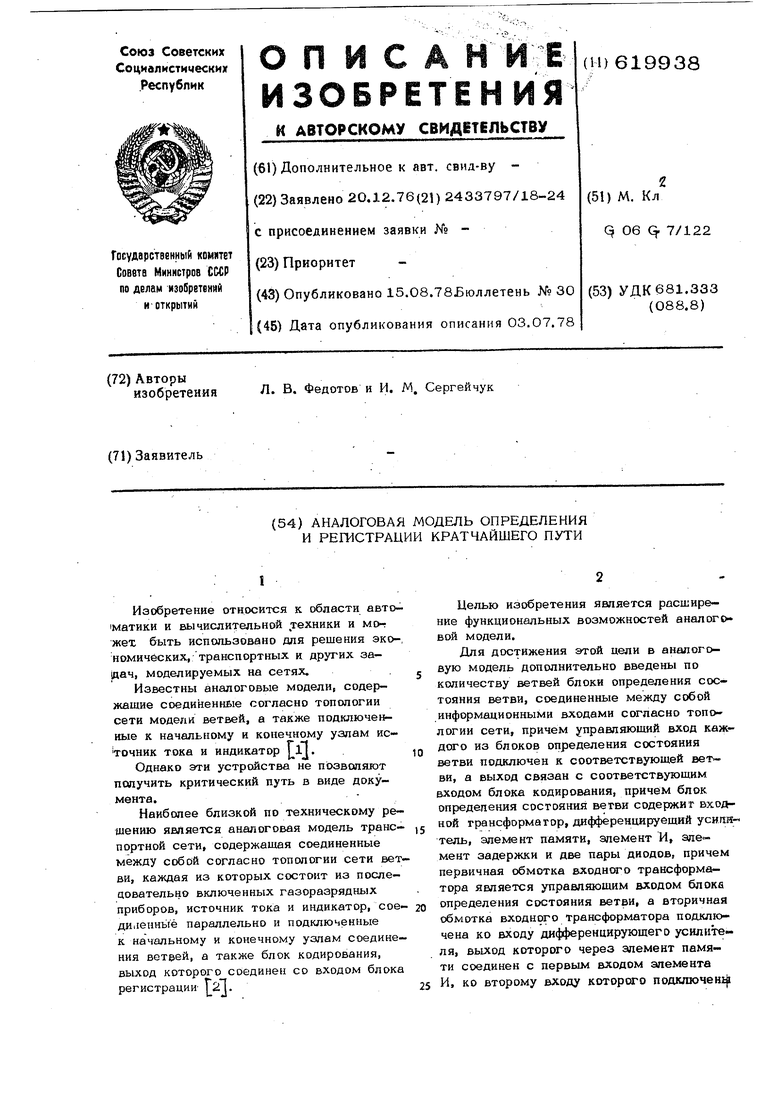

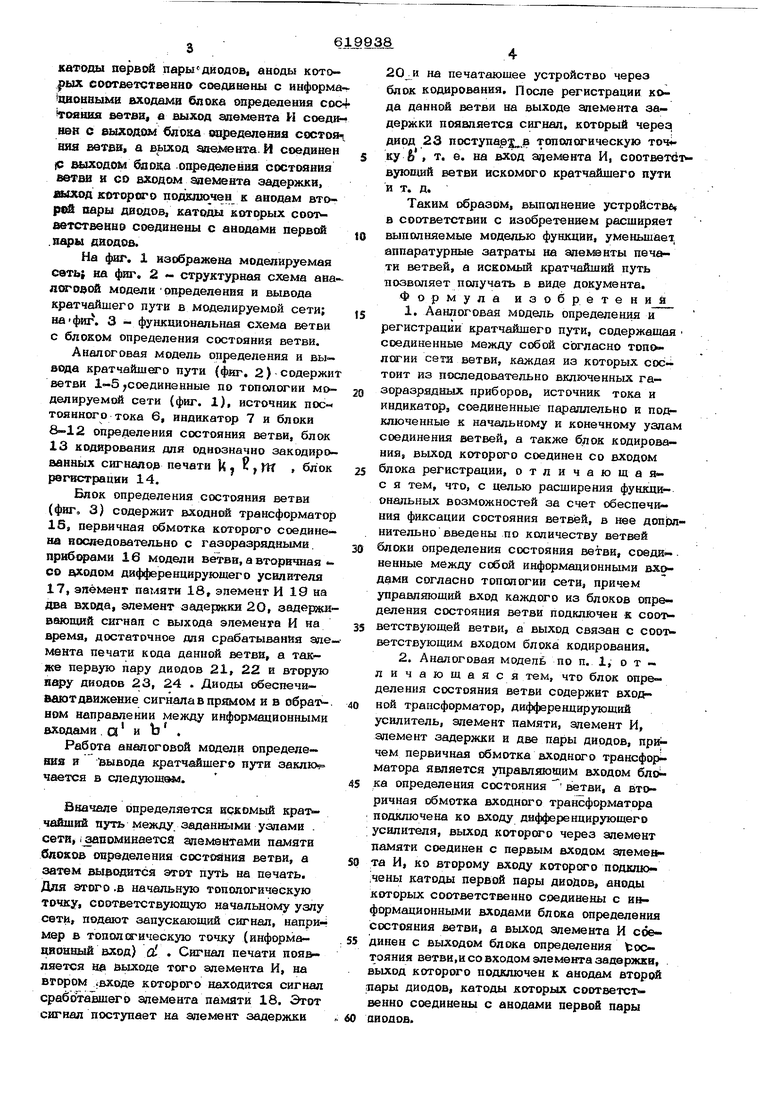

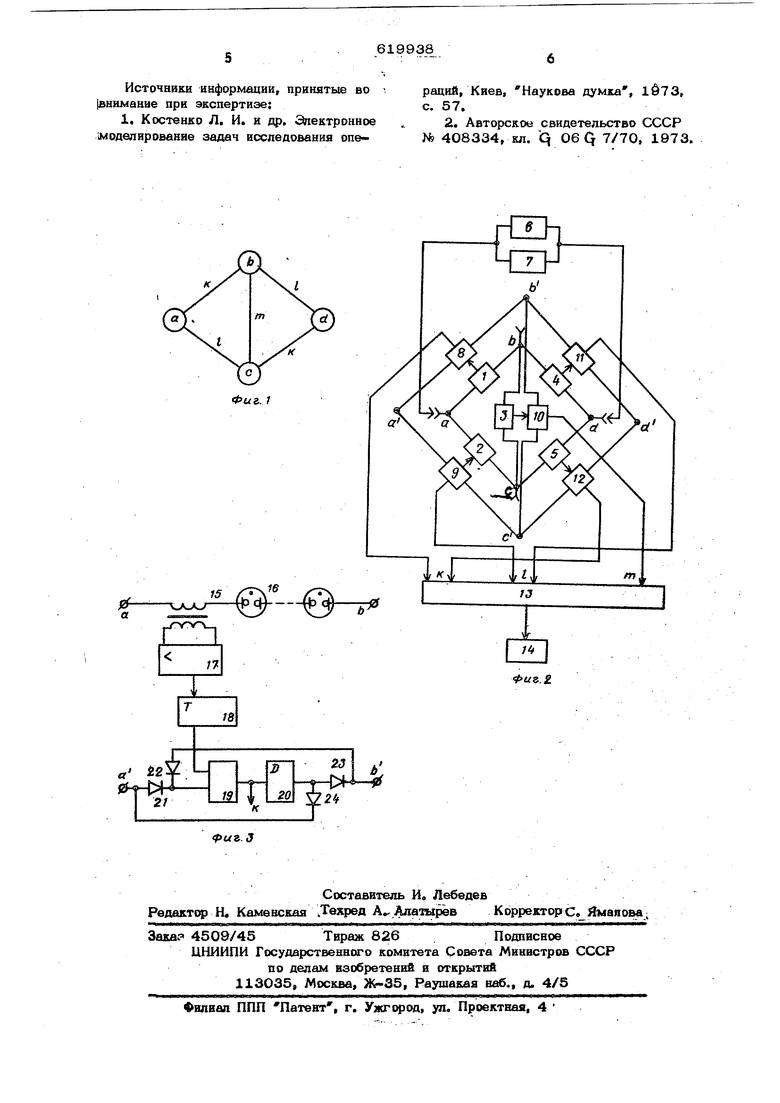

На фиг. 1 изображена моделируемая сеть; на фга. 2 - структурная схема анаnfs OQG& модели определения и вывода кратчайшего пути в моделируемой сети; нафиг. 3 - функциональная схема ветви с блоком определения состояния ветви.

Аналоговая модель определения и вывода кратчайшего пути (фиг, 2) содержи ветви 1-5,соединенные по топологии моделируемой сети {фиг. 1), источник пос« тоянного тока 6, индикатор 7 и блоки 8-12 определения состояния ветви, блок 13 кодирования для однозначно закодированных сигналов печати 14 j , Ж , блок регистрации 14.

Блок определения состояния ветви (фиг, 3) содержит входной трансформатор 15, первичная обмотка которого соединена восяедовательно с газоразрядными, приборами 16 модели ветви, а вторичнаясо дходом дифференцирующего усилителя 17, эяемент памяти 18, эпемент И 19 на даа входа, элемент задержки 2О, задерживающий сигнал с выхода эяеменга И на время, достаточное для срабатывания зие мента печати кода данной ветви, а также первую пару диодов 21, 22 и вторую яару диодов 23, 24 . Диоды обеспечивают движение сигнала в прямом и в обратном направлении между информационными входами . а и b .

Работа аншюговой модели определенна и вывода кратчайшего иути заклю. чается в следующем.

Вначале определяется ис комый кратчайший путь между, заданными узпами . сети, .запоминается анемеитами памяти блоков определения состоания ветви, а затем выводится этот путь на печать. Для этого .в начальную топологическую точку, соответствующую начальному узлу сети, подают запускающий сигнал, напри-мер в тополегическую точку (информационный вход) (31 . Сигнал печати появляется не выходе того элемента И, на вгором ;вхойе которого находится сигнал сработавшего эдемента памяти 18. Этот сигнал поступает на элемент задержки

20 и на печатающее устройство через блок кодирования. После регистрации кода данной ветви на выходе элемента задержки появляется сигнал, который через, диод 23 nocTynajej-. топологическую ку 6 т. е. на вход элемента И, соответЬтвующий ветви искомого кратчайшего пути

и т. д.

Таким образом, выполнение устройстве, в соответствии с изобретением расширяет

0 выполняемые моделью функции, уменьшает аппаратурные затраты на элементы печати ветвей, а искомый кратчайший путь позволяет получать в виде документа. Формула изобретен и я

51. Аанлоговая модель определения и

регистрации кратчайшего пути, содержащая соединенные между собой согласно топологии сети ветви, каждая из которых состоит из псюледовательно включенных гаQ зоразрядных приборов, источник тока и индикатор, соединенные параллельно и подключенные к начальному и конечному узлам соединения ветвей, а также блок кодирования, выход которого соединен со входом

25 блока регистрации, отличающаяс я тем, что, с целью расширения функциональных возможностей за счет обеспеч№ния фиксации состояния ветвей, в нее доп)элнительно введены по количеству ветвей

0 блоки определения состояния ветви, соеди- ненные между собой информационными входами согласно топологии сети, причем управляющий вход каждого из блоков определения состояния ветви подключен к ветствующей ветви, а выход связан с COO-Dветствующим входом блока кодирования.

2. Аналоговая модель по п. 1, отличающаяся тем, что блок определения состояния ветви содержит вхо№0 ной трансформатор, дифференцирующий усилитель, элемент памяти, элемент И, элемент задержки и две пары диодов, при чем первичная обмотка входного трансформатора является управляющим входом бло

5 ка определения состояния ветви, а вт1 ричная обмотка входного трансформатора подключена ко входу дифференцирующего усилителя, выход которого через элемент памяти соединен с первым входом апемеы50 та И, ко второму входу которсно подклю,чеиы катоды первой пары диодов, аноды которых соответственно соединены с информационными входами блока определения состояния ветви, а выход элемента И сбе55 динен с выходом блока определения Достояния ветви, и со входом эле мента задержки, выход которого подключен к анодам второй пары диодов, катоды которых соответственно соединены с анодами первой пары

0 аиодов.

Источники информации, принятые во г внимание при экспертизе:

1. Костеыко Л. И. и др. Зпектронное моделирование задач исследования опе

раций, Киев, Наукова думка , , с. 57,

2. Авторское свидетельство СССР № 408334, кл. q 06 Q 7/70, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения сетевых задач | 1988 |

|

SU1564643A1 |

| Устройство для исследования параметров графов | 1986 |

|

SU1427379A1 |

| Устройство для определения кратчайшего пути на графе | 1983 |

|

SU1134944A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для определения экстремальных путей сетевых графов | 1987 |

|

SU1432548A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

|

SU1509925A2 |

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для определения экстремальных путей в графах | 1977 |

|

SU640314A1 |

Авторы

Даты

1978-08-15—Публикация

1977-12-20—Подача