1

Изобретение относится к автоматике и вычислительной технике и может найти применение при построении цифровых систем повышенной наделшости, например электронных цифровых вычислительных машин.

Известно устройство 1 для мажоритарного выбора дискретных сигналов, содержащее три элемента ИЛИ, соединенные с элементами И, выходами связанными соответственно с вторыми входами элементов ИЛИ последующего . канала, первые входы которых подключены к источникам входных сигналов.

Иедостаток устройства 1 состоит в том, что в нем входные сигналы должны поступать одновременно (синхронно).

Наиболее близким по технической сущности к изобретению является устройство 2 для мажоритарного выбора сигналов, содержащее элементы И, выходы которых соединены с соответствующими входами элемента , а первые входы - с источниками входных сигналов.

Однако такое устройство неработоспособно при асинхронной подаче сигналов на его входы.

Цель изобретения - расщирение области применения устройства, в частности обеспечение работоспособности устройства

при асинхронном поступлении сигналов от источников.

Поставленная цель достигается тем, что в устройство введены триггеры и элемент задержки, вход которого связан с выходом элемента ИЛИ-НЕ, а выход - с первыми входами триггеров, выходы которых подключены к вторым входам соответствующих элементов И. Вторые входы второго и третьего триггеров соединены с первым источником входных сигналов, первого и шестого триггеров - с вторым источником входных сигналов, четвертогоИ пятого триггеров-с третьим источником входных сигналов.

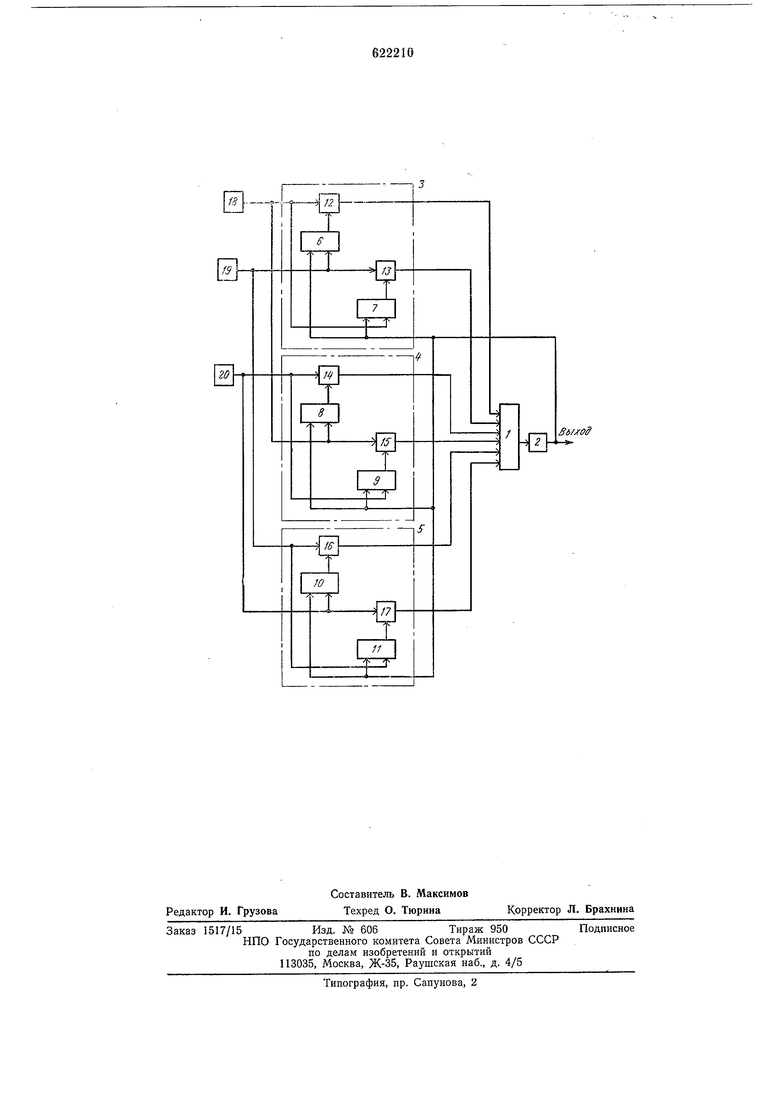

На чертеже приведена структурная схема устройства для мажоритарного выбора сигналов.

Она содержит элемент ИЛИ-НЕ 1, элемент 2 задержки, входные блоки 3-5, в состав которых входят триггеры 6-11 и элементы И 12-17; сигналы на устройство поступают от источников 18-20 входных сигналов.

Устройство для мажоритарного выбора сигналов работает следующим образом.

Сигнал от одного из источников (например, 18), пришедший ранее сигналов от двух других источников (19 и 20), устанавливает триггеры 7 и 8 в входных блоках 3 и 4 в рабочее состояние, при котором элементы-И 13 и 14 открыты. Поступивший затем сигнал от другого 1}сточника (нанример, 19) нроходит через открытый элемент И 13 на соответствующий вход элемента ИЛИ-НЕ 1. С выхода этого элемента сигнал через элемент 2 задержки подается на выход устройства и в цепь установки триггеров 6-И в исходное положение.

При появлении третьего сигнала от источника 20 работа устройства определяется выбранными соотношениями между длительностью входного сигнала т и временем задержки в элементе 2. Выбор времени задержки 4 проводится исходя из допустимого изменения длительности выходного сигнала и исключения появления ложного (повторного) выходного сигнала.

Если элемент 2 задержки отсутствует, то сигнал, проходящий через тот элемент И (12-17), который открыт, и элемент ИЛИ-НЕ 1, начинает поступать в цепь установки триггеров 6-11, практически одновременно с появлением его на входе элемента И (за вычетом задержки на прохождение через один элемент И 12-17 и элемент ИЛИ-НЕ 1). В результате триггеры 6--11 устанавливаются в исходное состояние до окончания прохождения всего сигнала через соответствующий элемент И (12- 17), и происходит искажение - «скол - длительности сигнала.

При времени задержки /з, меньшем длительности входного сигнала т, выходной сигнал мажоритарного органа имеет длительность на величину т-4- При ;2т длительность выходного сигнала TI может оказаться в пределах в случае, если третий входной сигнал запаздывает относительно второго от О до т. При и задержке третьего входного сигнала относительно второго на величину, большую т, возможно появление на выходе мажоритарного органа ложного импульса, т. е. оптимальная величина .

Работоспособность устройства для мажоритарного выбора сигналов обеспечивается при любой величине рассинхронизадии двух любых каналов трехканальной резервированной системы и при запаздывании третьего входного сигнала относительно второго, не превышающем длительности входного сигнала т.

В составе трехканальной резервированной системы устройство осуществляет синхронизацию в пределах одного периода (цикла) сигналов, поступающих асинхронно на его вход. Поэтому вероятность значительной рассинхронизации всех трех каналов, при которой третий входной сигнал данного периода (цикла) будет воспринят как первый входной сигнал следующего цикла, весьма мала и для практических целей может не учитываться.

Технико-экономический эффект от использования изобретения заключается в упрощении резервированной системы в целом, так как исключается необходимость введения сложных синхронизирующих устройств.

Формула изобретения

Устройство для мажоритарного выбора сигналов, содержащее элементы И, выходы которых соединены с соответствующими входами элемента ИЛИ-НЕ, а первые входы с источниками входных сигналов, о т личающееся тем, что, с целью расширения области применения, оно содержит триггеры и элемент задержки, вход которого соединен с выходом элемента ИЛИ-НЕ, а выход -с первыми входами триггеров, выходы которых соединены с вторыми входами соответствующих элементов И, вторые входы второго и третьего триггеров соединены с первым источником входных сигналов, первого и щестого триггеров - с вторым источником входных сигналов, четвертого и пятого триггеров - с третьим источником входных сигналов.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 263670, кл. Н ОЗК 5/13, 1970.

2.Доманицкий С. М. Построение надежных логических устройств. М., «Энергия, 1971, с. 163, рис. 5-10.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбораАСиНХРОННыХ СигНАлОВ | 1979 |

|

SU834703A1 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Трехканальное резервированноеуСТРОйСТВО для СиНХРОНизАции СигНАлОВ | 1979 |

|

SU822187A1 |

| Трехканальный резервированный распределитель импульсов | 1980 |

|

SU930318A2 |

| Мажоритарное устройство | 1983 |

|

SU1119196A1 |

| Резервированное трехканальное программно-временное устройство | 1978 |

|

SU741494A2 |

| Трехканальное устройство для синхронизации асинхронных импульсных сигналов | 1990 |

|

SU1785088A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1420661A1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

Авторы

Даты

1978-08-30—Публикация

1977-01-03—Подача