1

Изобретение относится к вычислительной технике и может использоваться при построении резервированных делителей частоты.

Известно резервированное программно-временное устройство, содержащее резервированные задающие генераторы , выходы которых соединены с входами делителей частоты, выход каждого делителя частоты соединен с входами узла Сброс, включающего мажоритарный элемент, несинхронные генераторы и формирователь импульса Сброс, выход узла Сброс, соединен с входом Сброс делителя частоты. Устройство обеспечивает .синхронную работу делителей частоты при первом включении и/или при наличии на входе трех каналов делителей частоты импульсов, длительность ко;торых имеет случайный характер (оди.номная помеха, кратковременный от.каз в цепи генератора)С1 .

Недостатком устройства является : :ограниченное быстродействие делителя частоты, которое определяется быстродействием последовательно включен-г ных элементов делителя частоты, несинхронного генератора, мажоритарного элемента и узла, формирующего импульс Сброс.

Наиболее близким к предлагаемому

10 по технической сущности является резервированное многоканальное устройство для формирования тактовых импульсов, содержащее в каж/цом канале генератор, соединенный через вый элемент И-НЕ со счетным входом делителя частоты и дешифратором, выход каждого разряда делителя частоты через последовательно включенные дешифратор, триггер памяти и мажоритар20ный элемент соединен с первым входом формирователя импульса Сброс, включающего два D-триггера и элемент ЗИ-НЕ, второй вход соединен с гене3 100

ратором частоты. Первый и второй выходы формирователя импульса Сброс соединены соответственно с входом Сброс делителя частоты и входом R-триггера памяти, входом дешифратора, а третий и четвертый выходы через второй элемент И-НЕ соединены с входом первого элемента И-НЕ 2.

Недостатком устройства является, то что для исключения гоночных ситуаций (одновременное присутствие задних фронтов на счетном и обнуляющем входах триггеров делителя частоты) введены два элемента 2И-НЕ с соответствующими связями, запрещающие импульсы на счетном входе на время действия обнуляющего импульса. При такой логике функционирования даже

.при отсутствии рассинхронизации делитель частоты за цикл синхронизации переключается по двум разным цепочкам: первая - через первый элемент 2И-НЕ по счетному входу триггеров делителей частоты; вторая - через фо мирователь импульсов обнуления (элемент ЗИ-НЕ) по обнуляющему входу три геров делителя частоты. Таким образом, наличие элементов, последовател но включенных в цепи генератор-делитель и наличие двух цепочек прохождения импульсов на переключение делителя снижают быстродействие, а также усложняют устройство. Для учета всех тактов, необходимых для разнесения во времени процессов в контуре синхронизации, дешифратор срабатывает за два такта до обнуляющего такта что усложняет устройство из-за включения дополнительного дешифратора и не позволяет применять дешифраторы единичного состояния, которые используются в цепи сквозного переноса в некоторых типах делителей частоты.

Цель изобретения - повышение быстродействия и упрощение устройства, в частности за счет исключения из цепи генератор - (2И-НЕ/ЗИ-НЕ) - де.литель частоты первого элемента 2ИНЕ, элемента ЗИ-НЕ с соответствующим связями, а также связи формирователя импульса Сброс с дешифратором.

Поставленная цель достигается тем что в устройство для синхронизации резервированного делителя частоты, содержащее трехкаиальный генератор, выходы которого подключены соответственно к входам трех каналов обработки частоты, каждый из которых содержит делитель частоты, счетный вхо

)4

которого соединен с соответствующим входом дешифратора, мажоритарный элемент, D-триггер, D-вход, инверсный выход и С-вход которого соединены с

входами элемента ЗИ-НЕ, выход которого соединен с входом Сброс делителя частоты, в каждый канал обработки введены JK-триггер и инвертор, вход которого соединен с соответствующим выходом трехканального генератора и счетным входом делителя частоты, а выход - с С-входом Dтриггера, выход элемента ЗИ-НЕ соединен с обнуляющим входом JK-триггера,

5 С-вход которого соединен с выходом дешифратора, а прямой выход соединен с одним из входов мажоритарного элемента каждого канала, выход мажоритарного элемента соединен с О-вхо0 дом D-триггера, прямой выход каждого разряда делителя частоты соединен с соответствующим входом дешифратора.

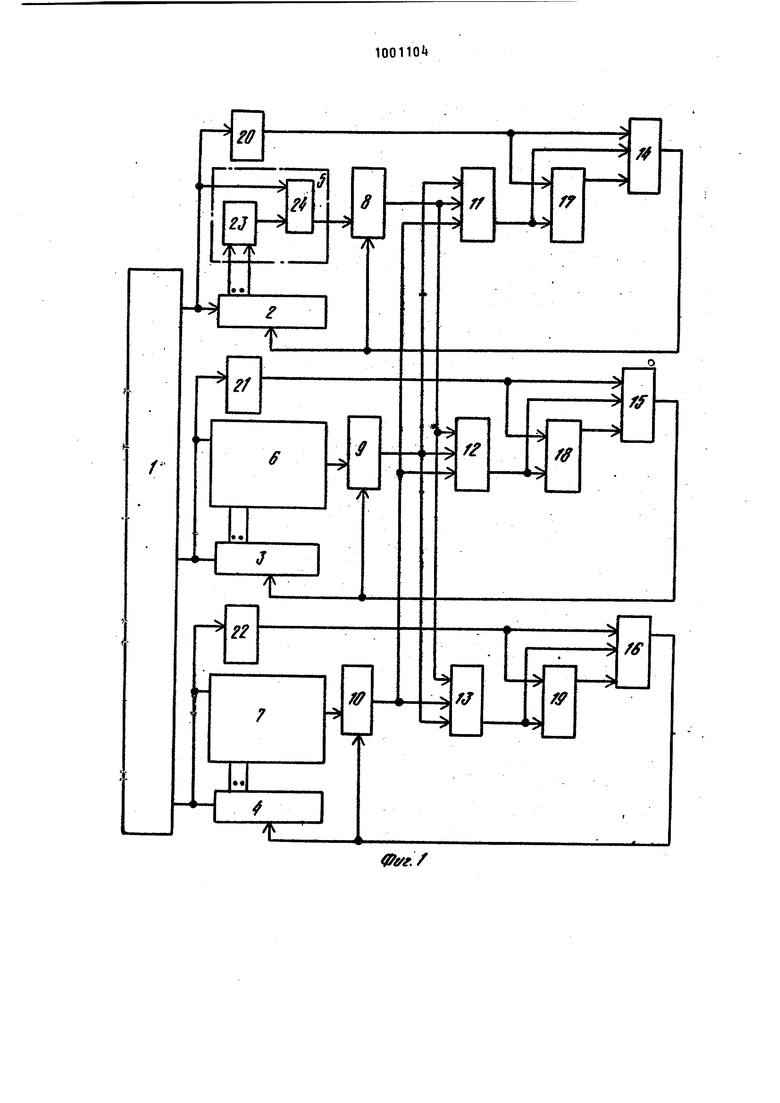

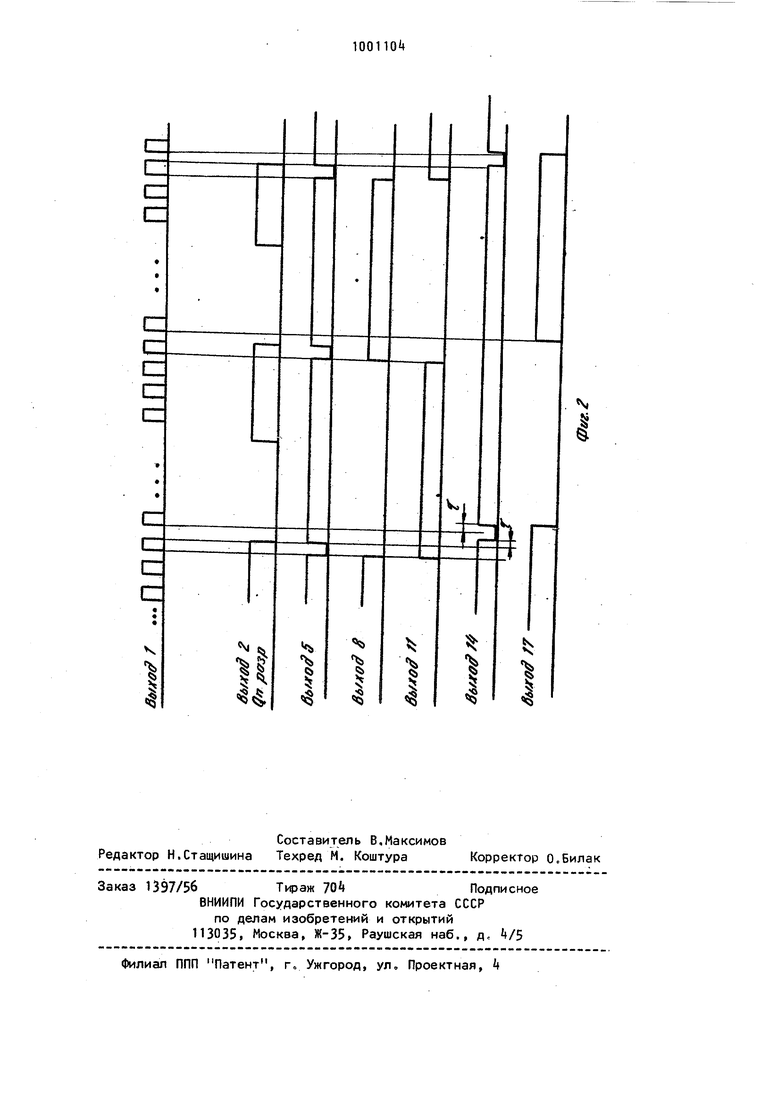

На фиго 1 приведена функциональ5 ная схема устройства для синхронизации резервированного делителя частоты; на фиго 2 - приведены временные диаграммы, поясняющие работу устройства.

Устройство на фиг с 1 содержит трехканальный генератор 1, делители 2частоты, дешифраторы 5-7, JK-триггеры 8-10, мажоритарные элементы 1113, элементы ЗИ-НЕ Й-1б„ D-триггеры 17-19, инверторы 20-22, дешифратор 23 единичного состояния, элемент 2И-НЕ 24. Выход генератора 1 соединен со счетным входом одноименного делителя 2(3,) частоты, прямые выходы триггеров которого и соответствующий выход генератора 1 соединены с входами дешифратора 5(6, 7) выход которого соединен со счетным входом JK-триггера 8(9, 10) прямой выход которого соединен с соответствующим входом каждого мажоритарного элемента 11(12, 13), выход которого соединен с первым входом элемента ЗИ-НЕ IfdS, 16) и с D-входом О-триггера

17(18, 19), инверсный выход которого соединен с вторым входом элемента ЗИ-НЕ 14(15, 16), выход которого соединен с входами Сброс триггеров делителя. 2(3, 4) частоты и входом

обнуления JK-триггеров 8(9, Ю). Счетный вход делителя частоты 2(3,) соединен с входом инвертора 20(21,22), выход которого соединен с третьим входом элемента ЗИ-НЕ (15, 16) м со счетным входом D-триггера 17(18, На фиг. 2 приняты следующие обозначения: выход 1 - выход генератора 1, выход 2 Ц„роэй,пРмой выход по следнего разряда делителя 2 частоты и т. Т- время, задержки фронтов импульса Cfipoc (выход И) относительно фронтов импульса генератора Устройстйо работает следующим образом, С трехканального генератора 1 частоты частота f (фиг. 2)гюступает в три канала обработки частоты на тр делителя частоты 2-, Работа трех каналов обработки частоты идентична поэтому рассмотрим работу первого канала. В момент, когда по заднему .фронту некоторого импульса частоты генератора 1 все триггеры делителя 2 частоты (на фиг. 2 указано состояние последнего разряда Q) устанавливаются в единичное состояние, срабатывает стробируем |й частотой генератора дешифратор 5 единично|Го состояния. На выходе дешифратора 5 единичного состояния появляется импульс логического нуля, по переднему фронту которого срабатывает JK-триггер 8, в результате чего на его выходе появляется потенциал логического нуля, который сохраняется до появления следующего импульса с выхода дешифратора 5 При появлении потенциала логического нуля на выходе JK-триггера 8 хотя бы в двух каналах обработки частоты, с выхода мажоритарного элемента 11 сигнал логической .единицы поступает на информационный вход D-триггера 17 и вход элемента ЗИ-НЕ Т. При этом на инверсном выходе D-триггера 17 сохраняется еще потенциал логической . Таким образом, два входа элеме та ЗИ-НЕ k подготовлены по времени на половину периода частоты генерато ра 1 раньше момента формирования импульса по шине Сброс, в результате чего компенсируется время срабатывания элементов 5. 8 и 11„ Положительный сигнал с выхода инвертора 20 про ходит через элемент ЗИ-НЕ 1 и с его выхода поступает на входы Сброс триггеров делителя 2 частоты и JKтриггера 8, по заднему фронту устана ливая на инверсном выходе D-триггера 17 потенциал логического нуля, что .обеспечивает прохождение через элемент ЗИ-НЕ только одного импульса обнуления. При синхронной работе импульс по шине Сброс подтверждает нулевое состояние делителя 2 частоты и JK-триггера 8, При асинхронной работе делителей частоты все их разряды обнуляются и синхронность восстанавливается„ При появлении фронта логического 1нуля на выходе мажоритарного элемента 11 импульс обнуления не формируется и через такт равный периоду импульсов с выхода 5 на инверсном выходе D-триггера 17 устанавливается потенциал логической единицы. Затем на выходе мажоритарного элемента 11 появляется положительный потенциал и цикл работы повторяется (снова формируется импульс обнуления по шине Сброс). Как видно из фиг. 1 и фиг, 2 длительность импульса с выхода элемента ЗИ-НЕ определяется длительностью логического нуля на выходе генератора 1 частоты за вычетом разности времени срабатывания и отпускания инвертора 20 и элемента ЗИ-НЕ 1 и не зависит от времени срабатывания остальных элементов канала обработки частоты, причем задержка фронтов этого импульса относительно фронтов частоты генератора 1 определяется только временем срабатывания инвертора 20 и элемента ЗИ-НЕ Й„ Поскольку эта задержка соизмерима с временем задержки срабатывания триггера в делителе частоты, контур синхронизации в предлагаемом устройстве не оказывает ограничений на максимальную частоту обработки, определяемую элементной базой, используемой в делителе, в то время как в известных устройствах tl и 2 1 задержка формирования импульса Сброс в канале обработки частоты определяете суммарным временем срабатывания элементов делителя частоты и элементов контура синхронизации, что накладывает ограничения на быстродействие устройства. В прототипе С2-3 при отсутствии рассинхронизации делитель частоты станавливается в нулевое положение (при запрете по счетному входу) через контур синхронизации, в предлагаемом устройстве - по счетному входу затем подтверждается импульсом, поступившим из контура синхронизации. Такая логика работы, обеспечиваемая введением деши(} атора единичного состояния, JK-триггера, инвертора с 71.0 соответствующими связями, позволяет исключить элементы 2И-НЕ, ЗИ-НЕ из цепи генератор - {2И-НЕ/ЗИ-НЕ) - делитель частоты в результате чего повышается быстродействие устройства. Исключение первого и второго 2И-НЕ элементов с соответствующими связями, связи формирователя с дешифратором, использование одного и того же дешифратора единицы для контура синх ронизации и, например, для цепи скво ного переноса определенного типа делителей частоты позволяет упроститьустройство. Таким образом, применение предлаг емого устройства позволяет повысить быстродействие делителя частоты и упростить устройство. Формула изобретения Устройство для синхронизации резервированного делителя частоты, содержащее трехканальный генератор, вы ходы которого подключены соответственно к входам трех каналов обработки частоты, каждый из которых содержит делитель частоты, счетный вход которого соединен с соответствующим вхрдом дешифратора, мажоритарный 1+8 элемент, 0-триггер, D-вход, инверсный выход и С-вход которого соединены с входами элемента ЗИ-НЕ, выход которого соединен с входом Сброс делителя частоты, отличающееся тем, что, с целью повышения быстродействия и упрощения устройства, в каждый канал обработки частоты введены JK-триггер иинвертор, вход которого соединен с соответствующим выходом трехканального генераторами счетным входом делителя частоты, а выход - с С-входом D-триггера, выход элемента ЗИ-НЕ соединен с обнуляющим входом JK-триггера. С-вход которого соединен с выходом дешифратора, а прямой выход соединен с одним из входов мажоритарного элемента каждого канала, выход мажоритарного элемента соединен с D-входом D-триггера, прямой выход каждого разряда делителя частоты соединен с соответствующим вхбДом дешифратора. Истомники информации, принятые во внимание при экспертизе 1« Авторское свидетельство СССР№ 385261, кл. G 06 F 11/00, 1970. 2, Авторское свидетельство СССР 767764, кл. G Об F 11/00, 1978. .(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Многоканальный резервированный генератор | 1989 |

|

SU1699028A1 |

| Резервированный генератор импульсов | 1982 |

|

SU1102066A2 |

| Трехканальный резервированный синхронизатор | 1984 |

|

SU1190558A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Фазируемый формирователь импульсов | 1988 |

|

SU1578849A1 |

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| Резервированный генератор синхроимпульсов | 1981 |

|

SU1008931A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU961155A1 |

Авторы

Даты

1983-02-28—Публикация

1981-01-12—Подача