(54) УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА АСИНХРОННЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для мажоритарного выбора асинхронных сигналов | 1982 |

|

SU1048478A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1982 |

|

SU1056489A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1986 |

|

SU1374229A1 |

| Селектор импульсных сигналов | 1980 |

|

SU875610A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Селектор импульсных сигналов | 1979 |

|

SU822336A1 |

| Устройство для обнаружения потери и восстановления импульса | 1990 |

|

SU1780160A1 |

| Регистр сдвига | 1976 |

|

SU643976A1 |

Изобретение относится к вычислительной технике и может найти применение при построении цифровых вычислительных машин повышенной надежности. Известно устройство для мажоритирования сигналов трехканальных систем, содержаш.ее три элемента -И, выходы которых через первый элемент ИЛИ-НЕ соединен с входом второго элемента ИЛИ-НЕ 1J. Недостатком устройства является его неработоспособность при асинхронном поступлении входных сигналов с каналов резервированного устройства. Наиболее близким по технической сущности, к предлагаемому является устройство для мажоритарного выбора сигналов, содержаш,ее шесть RS-триггеров, единичные установочные входы которых соединены с соответствуюш,ими шинами входных сигналов, пороговый элемент, входы которого соединены с соответствуюш,ими единичными выходами шести RS-триггеров и с шинами входных сигналов, элемент задержки, вход которого подключен к выходу порогового элемента, а выход соединен с выходной шиной устройства и с нулевыми установочными входами шести RS-триггеров 2. Недостатком этого устройства является конструктивная сложность. Цель изобретения - упрощение и повышение надежности устройства. Поставленная цель достигается тем, что устройство для мажоритарного выбора асинхронных сигналов, содержащее три элемента И, первые входы первого и второго элементов И соединены с единичными выходами соответственно первого и второго RS-триггеров, и элемент задержки, выход которого соединен с нулевыми входами первого, второго и третьего RS-триггеров, выходы первого, второго и третьего элементов И подключены к соответствующим входам первого элемента ИЛИ, содержит четвертый элемент И и второй элемент ИЛИ, входы которого соединены с единичными входами первого, второго и третьего RS-триггеров и со входами устройства, а выход - с первым входом четвертого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к выходу устройства и ко входу элемента задержки, единичные выходы первого и второго RS-триггеров соединены соответственно с первым и вторым входами третьего

элемента И, а единичный выход третьего RS-триггера подключен ко вторым входам первого и второго элементов И.

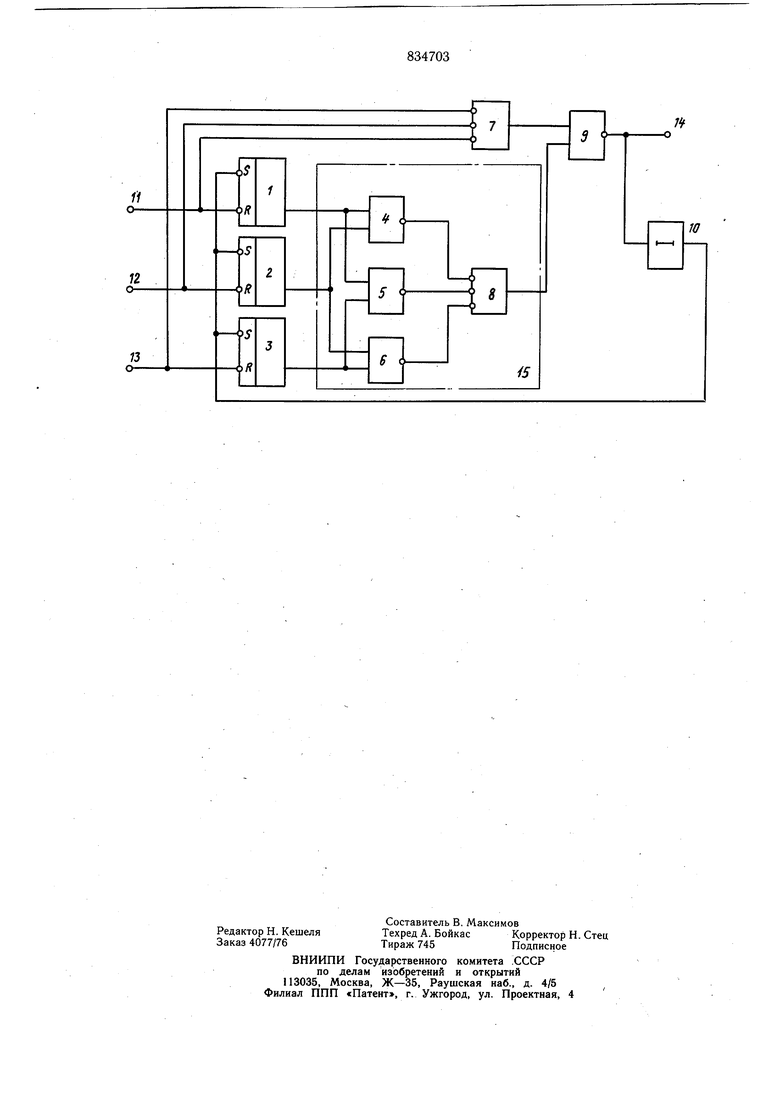

На чертеже представлена схема устройства.

Устройство содержит первый 1, третий 2 и второй 3 RS-триггеры, первый 4, третий 5 и второй 6 элементы И, второй 7 и первый 8 элементы ИЛИ, четвертый элемент 9 И, элемент 10 задержки, входы- 11 -13 и выход 14 устройства и мажоритарный блок 15.

Устройство работает следующим образом.

По шинам импульсных сигналов на входы 11 -13 поступают асинхронные импульсные сигналы. Пусть на вход 11 поступает первый импульсный сигнал. Он устанавливает RS-Триггер 1 в единичное состояние и разрешающий потенциал с единичного выхода Н5-триггера 1 поступает на первые входы элементов 4, 5 И. Этот импульс через элемент 7 ИЛИ поступает на первый вход элемента 9 И, ко второму входу которого приложен запирающий потенциал с выхода элемента 8 ИЛИ, в результате чего импульсный сигнал на выход 14 через элемент 9 И не проходит. Через время раесинхронизации на вход 12 поступает второй импульс и устанавливает RS-триггер 2 в единичное состояние, с единичного выхода которого сигнал поступает на входы элементов 4, 6 И соответственно. При этом на выходе элемента 4 И появляется сигнал, который поступает на вход элемента 8 ИЛИ, с выхода которого разрешающий потендиал поступает на вход элемента 9 И, на вход элемента 9 И приходит импульсный сигнал, поступающий с входа через элемент 7 ИЛИ. В этом случае импульсный сигнал появится на выходе 14 и на выходе элемента 10 задержки.

Через время задержки, равное требуемой длительности выходного импульса с выхода 14, импульсный сигнал с выхода элемента 10 поступает на нулевые установочные входы RS-триггеров 1-3 и устанавливает их в исходное состояние. Длительность выходного импульса элемента 10 выбирается из условия обеспечения сброса RS-триггеров с учетом максимального времени рассиихронизации входных сигналов.

Работоспособность устройства для мажорита.рного выбора асинхронных сигналов сохраняется при поступлении импульсных сигналов на входы 11 -13 в любой последовательности.

Таким образом, введение в устройство одного элемента ИЛИ и соответствующих связей позволяет отказаться от трех RSтриггеров, двух элементов И и десяти щин связей по сравнению с известным, что устраивает конструкцию устройства и соответственно повыщает его надежность, снижает стоимость изготовления.

Формула изобретения

Устройство для мажоритарного выбора асинхронных сигналов, содержащее три элемента И, первые входы первого и второго элементов И соединены с единичными выходами соответственно первого и второго RSтриггеров, и элемент задержки, выход которого соединен с нулевыми входами первого, второго и третьего RS-трйггеров, выходы первого, второго и третьего элементов И подключены к соответстующи,м входам первого элемента ИЛИ, отличающееся тем, что,

5 с целью упрощения и повышения надежности устройства, оно содержит четвертый элемент И и второй элемент ИЛИ, входы которого соединены с единичными входами первого, второго и третьего RS-триггеров и со входами устройства, а выход - с первым входом четвертого элемента И, второй вход которого подключен к выходу первого элемента ИЛИ, а выход - к выходу устройства и ко входу элемента задержки, единичные выходы первого и второго RS-триггеров соединены соответственно с первым

и вторым входами третьего элемента И, а единичный выход третьего RS-триггера под.ключен ко вторым входам первого и второго элементов И.

Источники информации,

0 принятые во внимание при экспертизе

,1. Доманицкий С. М. Построение надежных логических устройств. М., «Энергия, 1971, с. 163, рис. 5-10.

Авторы

Даты

1981-05-30—Публикация

1979-07-05—Подача