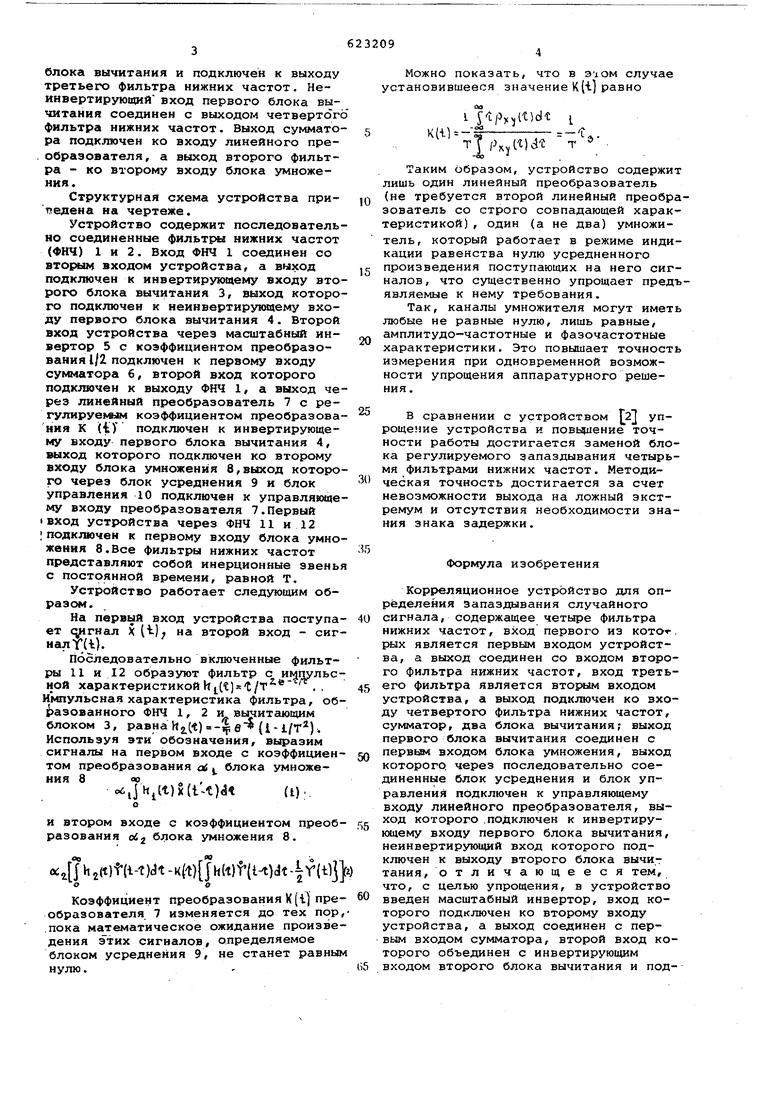

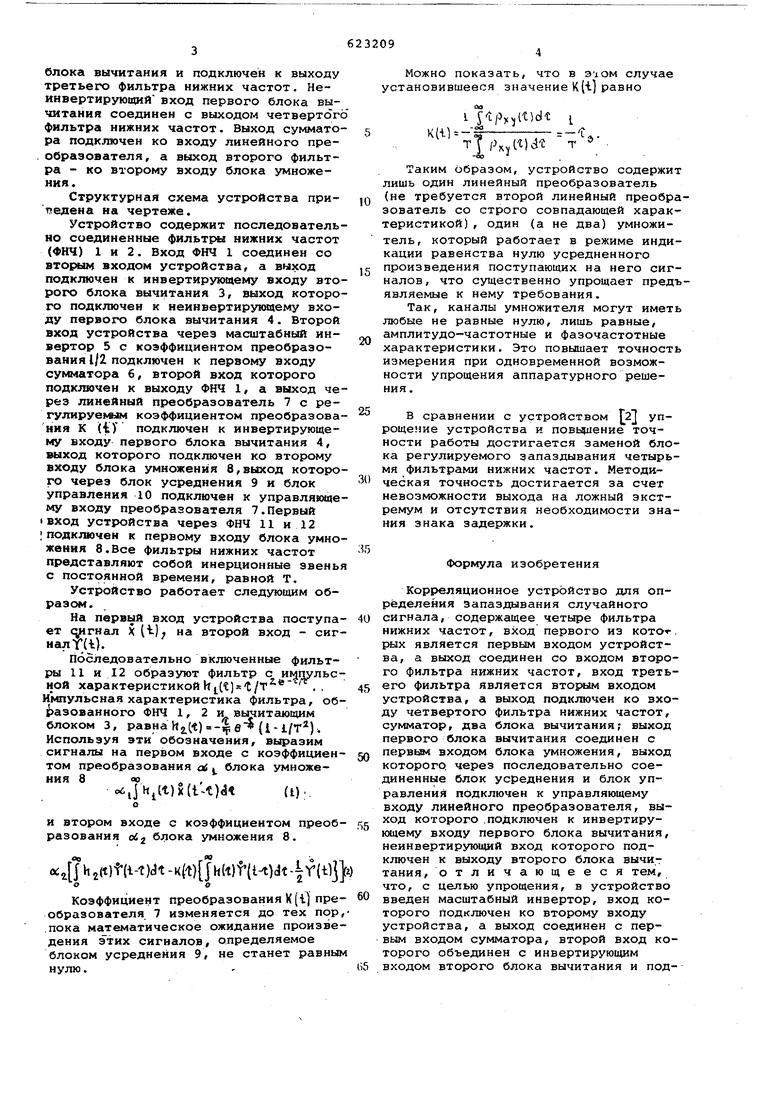

блока вычитания и подключен к выходу третьего фильтра нижних частот, Неинвертирующий вход первого блока вычитания соединен с выходом четвертого фильтра нижних частот. Выход сумматора подключен ко входу линейного пре. обраэователя, а выход второго фильтра - ко второму входу блока умножения. Структурная схема устройства приведена на чертеже. Устройство содержит последовательно соединенные фильтры нижних частот (ФНЧ) 1 и 2. Вход ФНЧ 1 соединен со втос«1м входом устройства, а выход подключен к инвертирующему входу второго блока вычитания 3, выход которого подключен к неинвертирунвдему входу первого блока вычитания 4. Второй вход устройства через масштабный инвертор 5 с коэффициентом преобразования 1/2 подключен к первому входу сумматора 6, второй вход которого подключен к выходу ФНЧ 1, а выход че рез линейный преобразователь 7 с регулируека коэффициентом преобразовакия К (ty подключен к инвертирующему входу первого блока вычитания 4, выход которого подключен ко второму входу блока умножения 8,выход которо го через блок усреднения 9 и блок управления 10 подключен к управляюида му входу преобразователя 7.Первый вход устройства через ФНЧ И и 12 IпoдкJвoчeн к первому входу блока умно жения 8.Все фильтры нижних частот представляют собой инерционные звенья с постоянной времени, равной Т, Устройство работает следующим образом. На первый вход устройства поступает сигнал X (t) на второй вход - сигналГи). Последовательно включенные фильтры 11 и 12 образуют фильтр с И1«1пульсной характеристикой ) . . Импульсная характеристика фильтра, образованного ФНЧ If 2 ч ВЫЧИТсЦОЩИМ блоком 3, PaBHah2 t)«-|ie(i-i/T). Используя эти обозначения, выразим сигналы на первом входе с коэффициентом преобразования об блока умножения 8 се „ , o6jh(t)x(l-t) (t).. и втором входе с коэффициентом преоб разования ofj блока умножения 8. (t)(-f)-x(t)llh(t)f{M)dt-|r(t)) оо Коэффициент преобразования К (t| пре образователя 7 изменяется до тех пор .пока математическое ожидание произве дения этих сигналов, определяемое блоком усреднения 9, не станет равным нулю. Можно показать, что в эчом случае установившееся значение K(i равно I 1p( I K{ib--fr-t тТ )At т Таким образом, устройство содержит лишь один линейный преобразователь (не требуется второй линейный преобразователь со строго совпадающей характеристикой) , один (а не два) умножитель, который работает в режиме индикации равенства нулю усредненного произведения поступающих на него сигналов , что существенно упрощает предъявляемые к нему требования. Так, каналы умножителя могут иметь любые не равные нулю, лишь равные, амплитудо-частотные и фазочастотные характеристики. Это повышает точность измерения при одновременной возможности упрощения аппаратурного решения. в сравнении с устройством 2 упрощение устройства и повьциение точности работы достигается заменой блока регулируемого запаздывания четырьмя фильтрами нижних частот. Методическая точность достигается за счет невозможности выхода на ложный экстремум и отсутствия необходимости знания знака задержки. Формула изобретения Корреляционное устройство для определения запаздывания случайного сигнала, содержащее четыре фильтра нижних частот, вход первого из котот. рых является первым входом устройства, а выход соединен со входом второго фильтра нижних частот, вход третьего фильтра является вторым входом устройства, а выход подключен ко входу четвертого фильтра нижних частот, сумматор, два блока вычитания; выход первого блока вычитания соединен с первьдл входом блока умножения, выход которого, через последовательно соединенные блок усреднения и блок управления подключен к управляницему ВХОДУ линейного преобразователя, выход которого .подключен к инвертирующему входу первого блока вычитания, неинвертирующий вход которого подключен к выходу второго блока вычитания, отличающееся тем, что, с целью упрощения, в устройство введен масштабный инвертор, вход которого Подключен ко второму входу устройства, а выход соединен с первым входом сумматора, второй вход которого объединен с инвертирующим входом второго блока вычитания и подключей к выходу третьего фильтра нижних частот, неинвертирующий вход первого блока вычитания соединен с выходом четвертого фильтра нижних частот; выход сумматора подключен ко входу линейного преобразователя, а выход второго фильтра - ко второму входу блока умножения.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР

226959, М., кл q 06 F 15/34,1969.

2.Заявка 2156108/24, М. , кл. G 06 G 7/19, 1975, по которой принято решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Корреляционное устройство для определения запаздывания случайного сигнала | 1982 |

|

SU1062727A1 |

| Устройство для определения запаздывания случайного сигнала | 1977 |

|

SU732860A1 |

| Устройство для оценки интервала корреляции нецентрированного случайного процесса | 1976 |

|

SU641463A1 |

| Устройство для определения запаздывания случайного сигнала | 1976 |

|

SU608174A1 |

| Устройство для определения -ых моментов импульсной переходной функции | 1979 |

|

SU858018A1 |

| Устройство для измерения мощности многофазной сети | 1984 |

|

SU1239617A1 |

| Устройство для контроля деградации МДП-структур | 1990 |

|

SU1783454A1 |

| Устройство для измерения запаздывания случайного сигнала | 1980 |

|

SU917170A1 |

| Многоканальный ортогональныйфильТР для СТАТиСТичЕСКОй идЕНТифи-КАции | 1979 |

|

SU832566A1 |

| Корреляционное устройство для определения запаздывания случайного сигнала | 1985 |

|

SU1290365A1 |

г

fil

Авторы

Даты

1978-09-05—Публикация

1977-03-01—Подача