1

Изобретение относится к технике связи и мож(т использоваться в дискретных системах управления и контроля радиоэлектронными объектами.

Известно устройство синхронизации,содержащее инвертор,носледовательно включенные блок Г111тан1 я и блок считывания, на унравляющий вход которого поданы тактовые импульсы, а выход блока считывания подключен ко входу «блокировка блока памяти 1 .

Однако это уст|,эй-ство имеет невысокую помехоустойчивость.

Цель изобрете 1ия - повышение помехоустойчивости устройства.

Для этого в устройство синхронизации, содержащее инвертор последовательно вклю-, ченные блок памяти и блок считывания,на управляющий вход которого поданы тактовые импульсы, а выход блока считывания подключен ко входу «блокировка блока па.мяти, к дополнительным сигнальным входам блока памяти и блока считывания подключен выход инвертора, а первый сигнальный вход блока считывания соединен с соответствующим входом блока памяти.

Блок памяти выполнен в виде элемента ИЛИ, ко входам которого подключены

выходы первого и второго элементов И, к первым входам подключен выход инвертора, а выход элемента ИЛИ подключен ко второму входу первого элемента И, причем первым и дополнительным сигнал-ьными входами блока памяти являются второй и третий вход второго элемента И, )дом «блокировка - вход инвертора.

Приче.м блок считывания выполнен на элементе ИЛИ, ко входам ко-торого подключены выходы первого и второго элементов И, а выход элемента ИЛИ подключен к первому входу первого элемента И, ко второму в.ходу которого подключен выход второго элемента ИЛИ, причем первым и дополнительным сигнальным входами блока считывания являются первый и второй

входы второго элемента ИЛИ. управляющим входом - третий вход второго элемента ИЛИ и первый вход второго элемента И, а входом «блокировка - второй вход последнего.

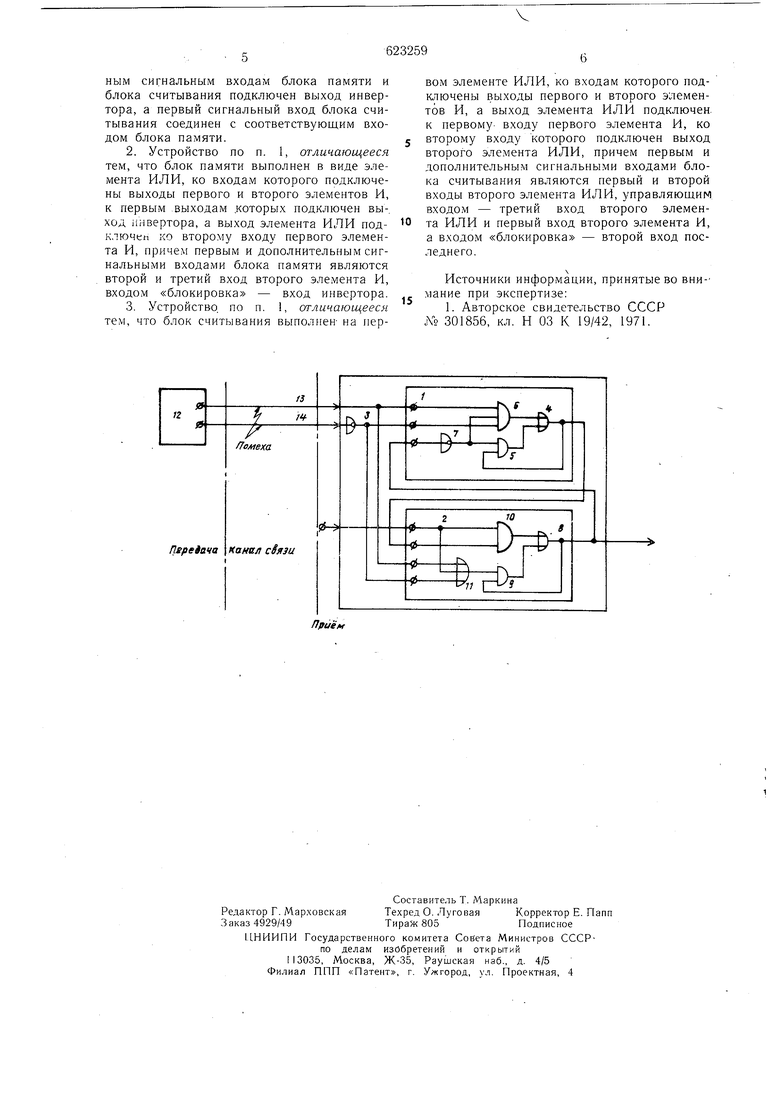

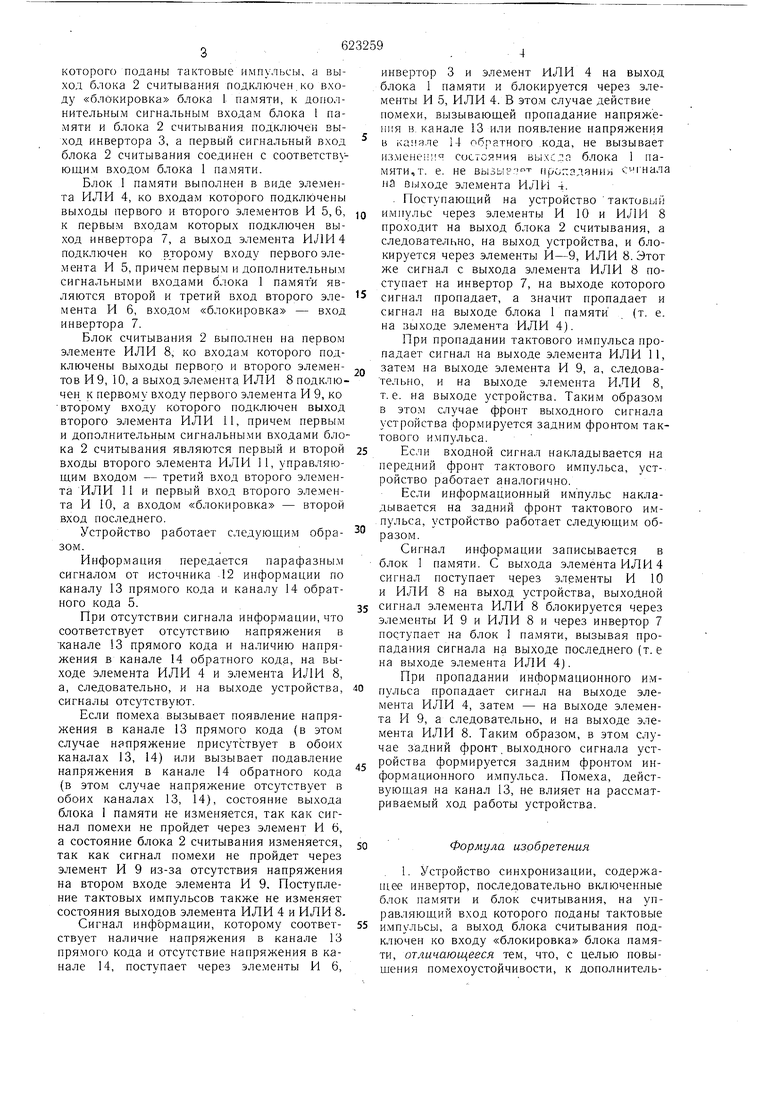

На чертеже изображена структурная

электрическая схема предложенного устройства.

Устройство синхронизации содержит пос. ледовательно включенный блок 1 памяти

и блок 2 считывания, на управляющий вход которого поданы тактовые импульсы, а выход блока 2 считывания подключен,ко входу «блокировка блока 1 памяти, к дополнительным сигнальным входам блока 1 памяти и блока 2 считывания подключен выход инвертора 3, а первый сигнальный вход блока 2 считывания соединен с соответствующим входом блока 1 памяти. Блок 1 памяти выполнен в виде элемента ИЛИ 4, ко входам которого подключены выходы первого и второго элементов И 5,6, к первым входам которых подключен выход инвертора 7, а выход элемента ИЛИ 4 подключен ко второму входу первого элемента И 5, причем первым и дополнительным сигнальными входами блока 1 памяти являются второй и третий вход второго элемента И 6, входом «блокировка - вход инвертора 7. Блок считывания 2 выполнен на первом элементе ИЛИ 8, ко входам которого подключены выходы первого и второго элементов И 9, 10, а выход элемента. ИЛИ 8 подключен к первому входу первого элемента И 9, ко второму входу которого подг лючен выход второго элемента ИЛИ 11, причем первым и дополнительным сигнальны.ми входами блока 2 считывания являются первый и второй входы второго элемента ИЛИ 11, управляющим входо.м - третий вход второго элемента ИЛИ 11 и первый вход второго эле.мента И 10, а входом «блокировка - второй вход последнего. Устройство работает следующим образом. Информация передается парафазны.м сигналом от источника 12 информации по каналу 13 прямого кода и каналу 14 обратного кода 5. При отсутствии сигнала информации, что соответствует отсутствию напряжения в канале 13 прямого кода и наличию напряжения в канале 14 обратного кода, на выходе элемента ИЛИ 4 и элемента ИЛИ 8, а, следовательно, и на выходе устройства, сигналы отсутствуют. Если помеха вызывает появление напряжения в канале 13 прямого кода (в этом случае напряжение присутствует в обоих каналах 13, 14) или вызывает подавление напряжения в канале 14 обратного кода (в это.м случае напряжение отсутствует в обоих каналах 13, 14), состояние выхода блока 1 памяти не изменяется, так как сигнал помехи не пройдет через элемент И 6, а состояние блока 2 считывания изменяется, так как сигнал помехи не пройдет через элемент И 9 из-за отсутствия напряжения на втором входе элемента И 9, Поступление тактовых импульсов также не изменяет состояния выходов элемента ИЛИ 4 и ИЛИ 8. Сигнал информации, которому соответствует наличие напряжения в канале 13 прямого кода и отсутствие напряжения в канале 14, поступает через элементы И 6, инвертор 3 и элемент ИЛИ 4 на выход блока 1 памяти и блокируется через элементы И 5, ИЛИ 4. В этом случае действие помехи, вызывающей пропадание напряжения в, канале 13 или появление напряжения в канале 14 обратного кода, не вызывает изменения состояния выхс,:. блока 1 памяти, т. е. не вьвыр, пропадания 4 гнала на выходе элемента ИЛИ 4. . Иоступающий на устройство тактовый имнульс через элементы И 10 и ИЛИ 8 проходит на выход блока 2 считывания, а следовательно, на выход устройства, и блокируется через элементы И-9, ИЛИ 8. Этот же сигнал с выхода элемента ИЛИ 8 поступает на инвертор 7, на выходе которого сигнал пропадает, а значит пропадает и сигнал на выходе блока 1 памяти (т. е. на зыходе элемента ИЛИ 4). При пропадании тактового импульса пропадает сигнал на выходе элемента ИЛИ 11, затем на выходе элемента И 9, а, следовательно, и на выходе элемента ИЛИ 8, т.е. на выходе устройства. Таким образо.м в это.м случае фронт выходного сигнала устройства формируется задним фронтом тактового импульса. Если входной сигнал накладывается на передний фронт тактового импульса, устройство работает аналогично. Если информационный импульс накладывается на задний фронт тактового импульса, устройство работает следующи.м образом. Сигнал информации записывается в блок 1 памяти. С выхода элемента ИЛИ 4 сигнал поступает через элементы И 10 и ИЛИ 8 на выход устройства, выхо.дной сигнал элемента ИЛИ 8 блокируется через эле.менты И 9 и ИЛИ 8 и через инвертор 7 поступает на блок 1 памяти, вызывая пропадания сигнала на выходе последнего (т. е на выходе эле.мента ИЛИ 4). При пропадании информационного импульса пропадает сигнал на выходе элемента ИЛИ 4, затем - на выходе эле.мента И 9, а следовательно, и на выходе элемента ИЛИ 8. Таким образом, в это.м случае задний фронт . выходного сигнала устройства формируется задним фронтом информационного импульса. Помеха, действующая на канал 13, не влияет на рассматриваемый ход работы устройства. Формула изобретения . Устройство синхронизации, содержаniee инвертор, последовательно вютюченные блок памяти и блок считывания, на управляющий вход которого поданы тактовые импульсы, а выход блока считывания подключен ко входу «блокировка блока памяти, отличающееся тем, что, с целью повыщения помехоустойчивости, к дополнительным сигнальным входам блока памяти и блока считывания подключен выход инвертора, а первый сигнальный вход блока считывания соединен с соответствующим входом блока памяти.

2.Устройство по п. 1, отличающееся тем, что блок памяти выполнен в виде элемента ИЛИ, ко входам которого подключены выходы первого и второго элементов И, к первым .выходам которых подключен вы-, ход iiHBepTOpa, а выход элемента ИЛИ подключен о второму входу первого элемента И, причем первым и дополнительным сигнальными входами блока памяти являются второй и третий вход второго элемента И, входом «блокировка - вход инвертора.

3.Устройство, по п. 1, отличающееся тем, что блок считывания выполнен- на первом элементе ИЛИ, ко входам которого подключены выходы первого и второго элементов И, а выход элемента ИЛИ подключен, к первому- входу первого элемента И, ко

второму входу которого подключен выход второго элемента ИЛИ, причем первым и дополнительным сигнальными входами блока считывания являются первый и второй входы второго элемента ИЛИ, управляющим входом - третий вход второго элемента ИЛИ и первый вход второго элемента И, а входом «блокировка - второй вход последнего.

Источники информации, принятые во внимание при экспертизе:

1. Авторское свидетельство СССР 301856, кл. Н 03 К 19/42, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема дискретной информации | 1974 |

|

SU504228A1 |

| Устройство для обнаружения поврежденного участка телеграфного тракта | 1981 |

|

SU1042194A2 |

| Способ обнаружения границ слов и устройство для его осуществления | 1978 |

|

SU1040512A1 |

| Устройство синхронизации | 1975 |

|

SU559420A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА РАДИОСТАНЦИЙ | 1995 |

|

RU2097908C1 |

| Устройство для оценки каналов и выбора оптимальных частот связи | 1981 |

|

SU1012448A1 |

| ПРИЕМНИК-ДЕШИФРАТОР КОДОВ КОДОВОЙ ЭЛЕКТРОННОЙ БЛОКИРОВКИ | 2018 |

|

RU2693811C1 |

| УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ДВОИЧНОЙ СИСТЕМЫ КОРОТКОВОЛНОВОЙ РАДИОСВЯЗИ с ЧАСТОТНО- ВРЕМЕННЫМ КОДИРОВАНИЕМ | 1973 |

|

SU389632A1 |

nefleiava

Авторы

Даты

1978-09-05—Публикация

1975-10-01—Подача