Изобретение относится к технике передачи дискретной информации, радиотехнике и может использоваться в радиостанциях и на приемных центрах при анализе резервных каналов связи.

Известно устройство автоматического поиска каналов радиосвязи, содержащее приемник, фильтр верхних частот, компаратор, счетчик, регистр, блок сравнения, блок формирования времени анализа, коммутатор порогов сравнения, инвертор, элемент "И" (см. авторское свидетельство СССР №362497, кл. Н04В 3/36).

Недостатком устройства является относительно большое время поиска канала связи.

Известно устройство автоматического выбора оптимального канала радиосвязи, содержащее блок оценки качества канала радиосвязи, приемник, хронизатор, регистр номера канала радиосвязи, блок оценки мощности нестанционных помех, блок определения отношения мощностей станционных и нестанционных помех, регистр оценки качества канала радиосвязи и блок сравнения (см. авторское свидетельство СССР №780800, кл. Н04В 1/10).

Недостатком устройства является относительно большое время процесса выбора канала связи, поскольку для выбора оптимального канала связи из числа заданных необходимо осуществить последовательный контроль всех резервных каналов.

Наиболее близким по технической сущности к заявляемому изобретению (прототип) является устройство автоматического поиска каналов радиосвязи, содержащее последовательно соединенные коммутатор частот, приемник, преобразователь сигналов, дешифратор, первый блок элементов "И" и блок триггеров, выходы которого подключены к второй группе входов первого блока элементов "И", элемент "ИЛИ", входы которого подключены к соответствующим выходам первого блока элементов "И", а также последовательно соединенные регистр сдвига, синхронизирующий вход которого вместе с синхронизирующим входом дешифратора подключены к управляющему выходу преобразователя сигналов, второй блок элементов "И", шифратор и блок памяти, причем управляющие входы второго блока элементов "И" и блок памяти подключены к выходу элемента "ИЛИ".

Недостатками устройства являются относительно большое время поиска канала связи, поскольку для выбора оптимального канала связи из числа заданных необходимо осуществить последовательный контроль всех резервных каналов, а также недостаточная достоверность выбора оптимального канала связи, обусловленные тем, что в прототипе предварительный контроль с учетом различных уровней помех в резервных каналах отсутствует.

Технический результат - повышение быстродействия выбора оптимального канала связи путем двухэтапного контроля резервных каналов.

Поставленная цель достигается тем, что известное устройство автоматического поиска каналов радиосвязи содержит приемник, информационный вход которого является входом устройства. Выход приемника подключен к входу преобразователя сигналов, информационные N выходы которого подключены к соответствующим информационным N входам дешифратора. Информационные N выходы дешифратора подключены к соответствующим инверсным N входам первого блока элементов "И", N выходов которого подключены к соответствующим входам N-входового элемента "ИЛИ" и N входам сброса блока триггеров. N выходов блока триггеров подключены к информационным N входам первого блока элементов "И". Управляющий выход преобразователя сигналов подключен к управляющему входу дешифратора и управляющему входу регистра сдвига. N выходов регистра сдвига подключены к соответствующим N входам второго блока элементов "И". N выходов второго блока элементов "И" подключены к соответствующим N входам первого шифратора. N выходов первого шифратора подключены к соответствующим N входам первого блока памяти. N выходов первого блока памяти являются выходами устройства. Гетеродинный вход приемника подключен к выходу коммутатора частот. Дополнительно введены блок элементов "ИЛИ", N выходов которого подключены к соответствующим N входам коммутатора частот. Первая и вторая группы информационных входов, по N входов каждая, блока элементов "ИЛИ" подключены соответственно к N выходам блока считывания и N информационным выходам блока управления. Установочный выход блока управления подключен соответственно к установочному входу блока триггеров и установочному входу регистра сдвига. Третий управляющий выход блока управления подключен к управляющему входу блока считывания. Второй управляющий выход блока управления подключен к управляющему входу второго блока памяти. Первый управляющий выход блока управления подключен к управляющему входу блока опроса. Выход приемника подключен к входу компаратора, суммирующий и вычитающий выходы которого подключены соответственно к суммирующим и вычитающим входам каждого из N реверсивных регистров. Четвертый управляющий выход блока управления подключен к установочным входам N реверсивных регистров. N синхронизирующих выходов блока управления подключены к синхронизирующим входам соответствующих N реверсивных регистров, N выходы каждого из которых подключены к соответствующей группе из N входов блока опроса. N информационных выходов блока опроса подключены к соответствующим N информационным входам второго шифратора. Разрешающий вход второго шифратора подключен к разрешающему выходу блока опроса. N выходов второго шифратора подключены к соответствующим N входам второго блока памяти, N выходов которого подключены к информационным N входам блока считывания.

Блок управления состоит из кнопки «Пуск», первый контакт которой подключен к источнику напряжения питания блока, а второй подключен к входу дифференцирующей цепи, выход которой является четвертым управляющим выходом блока, сигнальному входу первого генератора тактовых импульсов и S входу RS-триггера. R вход RS-триггера является установочным выходом блока. Он подключен к первому входу второго счетчика и выходу схемы сравнения. Выход регистра подключен к сигнальному входу схемы сравнения. К первому входу схемы сравнения подключен выход первого электронного ключа, являющийся вторым управляющим выходом блока. Первый вход первого электронного ключа подключен к выходу второго счетчика и первому входу второго электронного ключа. Выход второго электронного ключа является третьим управляющим выходом блока. Второй вход второго электронного ключа подключен к входу второго генератора тактовых импульсов и инверсному выходу RS-триггера. Прямой выход RS-триггера подключен к второму входу первого электронного ключа. Второй вход второго счетчика подключен к выходу элемента "ИЛИ", второй и первый входы которого подключены к выходам соответственно второго генератора тактовых импульсов и второго умножителя частоты импульсов. Выход второго умножителя частоты импульсов является первым управляющим выходом блока. Вход второго умножителя частоты импульсов подключен к выходу N-входового элемента "И" и вторым входам первого генератора тактовых импульсов и первого счетчика. Первый вход первого счетчика подключен к выходу первого генератора тактовых импульсов и входу элемента задержки. Выход элемента задержки подключен к входу первого умножителя частоты импульсов, выход которого подключен к управляющему входу каждого из группы N элементов "И". N выходов первого счетчика являются информационными N выходами блока и подключены к соответствующим N входам N-входового элемента "И" и к N входам каждого из группы N элементов "И". Реверсивные и прямые входы блока N-входового элемента "И" соединены соответственно с реверсивными и прямыми входами каждого из группы N элементов "И". Выходы группы N элементов "И" являются синхронизирующими N выходами блока.

Блок опроса состоит из N блоков элементов "ИЛИ-НЕ", N элементов "ИЛИ", N RS-триггеров, элемента "ИЛИ-НЕ", второго счетчика, инвертора и первого счетчика. Счетный вход первого счетчика является входом блока, а сигнальный подключен к соответствующему входу второго счетчика и R входам каждого из N RS-триггеров. n-й инверсный выход первого счетчика, где n=1, 2, …, N, подключен к первому входу n-го элемента "ИЛИ-НЕ". Первый инверсный выход первого счетчика подключен к входу инвертора, выход инвертора подключен к первому входу второго счетчика, n-й инверсный выход которого подключен к n-му входу каждого из N элементов "ИЛИ-НЕ". Третья группа из N входов n-го элемента "ИЛИ-НЕ" является n-ой группой из информационных N входов блока. N выходов n-го элемента "ИЛИ-НЕ" подключены к соответствующим N входам n-го элемента "ИЛИ". Выход n-го элемента "ИЛИ" подключен к n-му входу элемента "ИЛИ-НЕ" и к S входу n-го RS-триггера, а также является n-м выходом из N выходов блока. Выход n-го RS-триггера подключен к четвертому входу n-го элемента "ИЛИ-НЕ".

Коммутатор частот состоит из N электронных ключей, выходы которых объединены и являются выходом коммутатора частот. Первый и второй входы n-го электронного ключа, где n=1, 2, …, N, подключены к n-м выходам соответственно формирователя сетки частот и дешифратора. N входов дешифратора являются N входами коммутатора частот. Вход формирователя сетки частот подключен к выходу автогенератора.

Благодаря новой совокупности существующих процессов в заявляемом устройстве обеспечивается двухэтапный поиск и выбор оптимального радиоканала, что позволяет уменьшить время поиска оптимальных каналов, а также увеличивает достоверность выбора радиоканала.

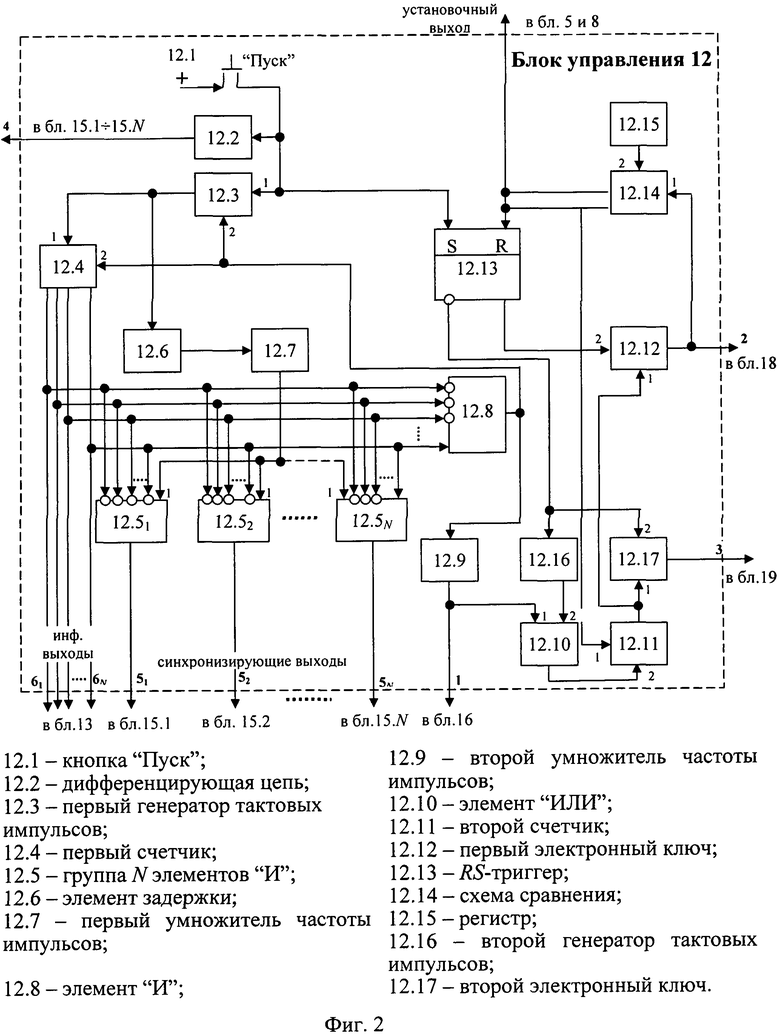

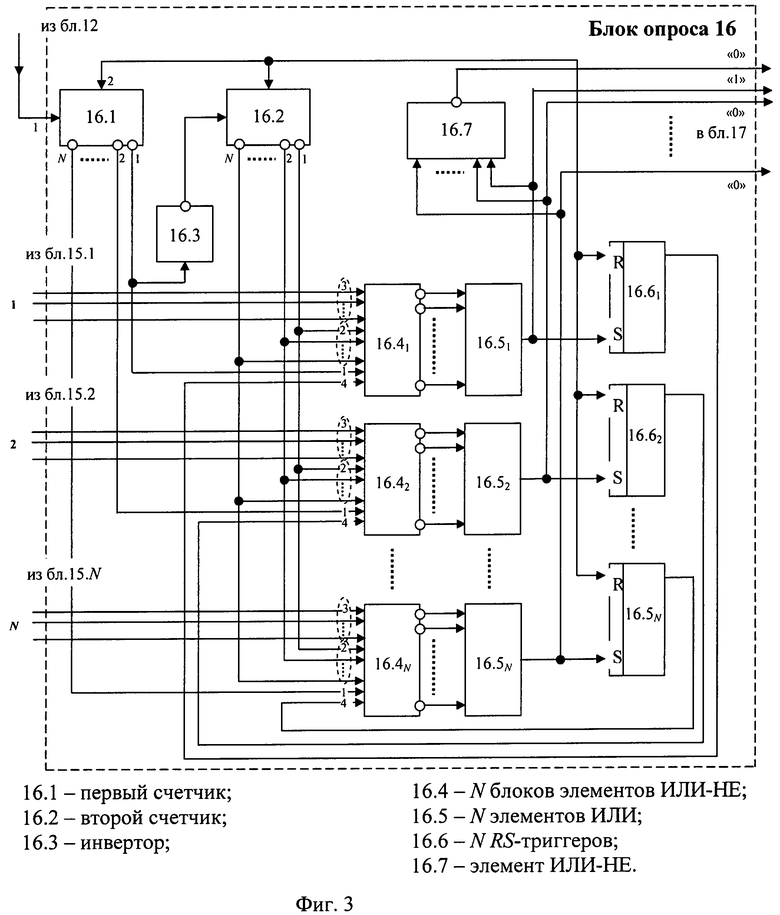

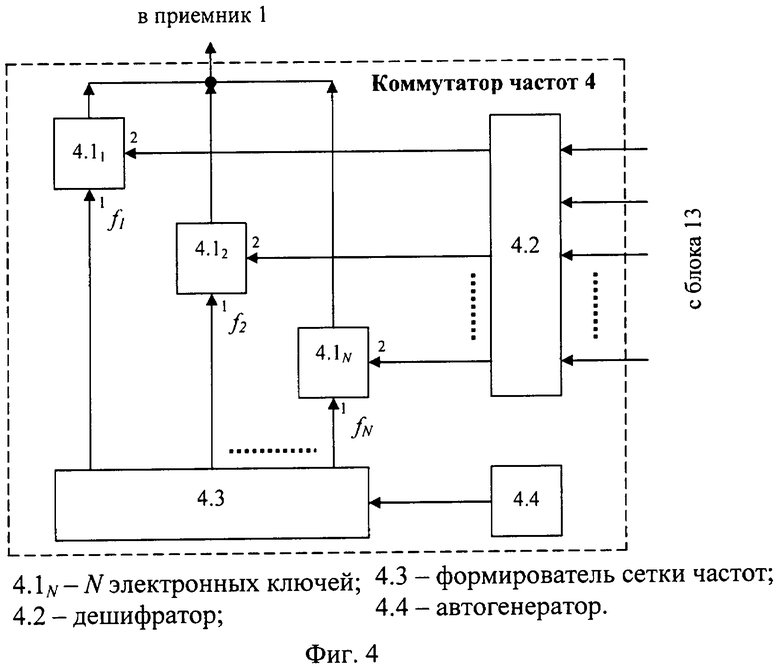

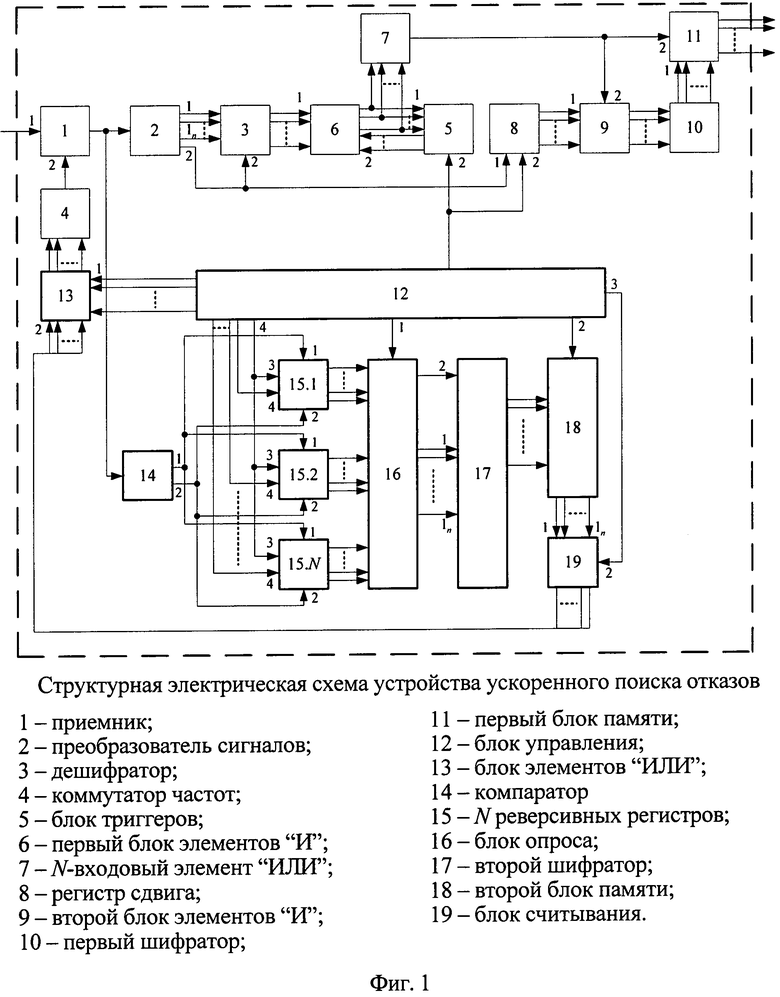

Заявленное устройство поясняется чертежами, на которых показано:

фиг.1 - общая структурная схема устройства;

фиг.2 - схема блока управления;

фиг.3 - схема блока опроса;

фиг.4 - схема коммутатора частот.

Устройство автоматического поиска каналов радиосвязи, показанное на фиг.1, содержит приемник 1, информационный вход которого является входом устройства. Выход приемника 1 подключен к входу преобразователя сигналов 2, информационные N выходы которого подключены к соответствующим информационным N входам дешифратора 3. Информационные N выходы дешифратора 3 подключены к соответствующим инверсным N входам первого блока элементов "И" 6, N выходов которого подключены к соответствующим входам N-входового элемента "ИЛИ" 7 и N входам сброса блока триггеров 5, N выходов которого подключены к информационным N входам первого блока элементов "И" 6. Управляющий выход преобразователя сигналов 2 подключен к управляющему входу дешифратора 3 и управляющему входу регистра сдвига 8, N выходов которого подключены к соответствующим N входам второго блока элементов "И" 9, N выходов которого подключены к соответствующим N входам первого шифратора 10, N выходов которого подключены к соответствующим N входам первого блока памяти 11, N выходов которого являются выходами устройства. Гетеродинный вход приемника 1 подключен к выходу коммутатора частот 4. Блок элементов "ИЛИ" 13, N выходов которого подключены к соответствующим N входам коммутатора частот 4, а первая и вторая группы информационных входов, по N входов каждая, блока элементов "ИЛИ" 13 подключены соответственно к N выходам блока считывания 19 и N информационным выходам блока управления 12, установочный выход которого подключен соответственно к установочному входу блока триггеров 5 и установочному входу регистра сдвига 8. Третий управляющий выход блока управления 12 подключен к управляющему входу блока считывания 19. Второй управляющий выход блока управления 12 подключен к управляющему входу второго блока памяти 18. Первый управляющий выход блока управления 12 подключен к управляющему входу блока опроса 16. Выход приемника 1 подключен к входу компаратора 14, суммирующий и вычитающий выходы которого подключены соответственно к суммирующим и вычитающим входам каждого из N реверсивных регистров 15. Четвертый управляющий выход блока управления 12 подключен к установочным входам N реверсивных регистров 15, а N синхронизирующих выходов блока управления 12 подключены к синхронизирующим входам соответствующих N реверсивных регистров 15, N выходы каждого из которых подключены к соответствующей группе из N входов блока опроса 16, N информационных выходов которого подключены к соответствующим N информационным входам второго шифратора 17, разрешающий вход которого подключен к разрешающему выходу блока опроса 16. N выходов второго шифратора 17 подключены к соответствующим N входам второго блока памяти 18, N выходов которого подключены к информационным N входам блока считывания 19.

Блок управления 12 предназначен для управления работой и подачи кодовых комбинаций (импульсов) в основные блоки устройства автоматического поиска каналов радиосвязи. Он может быть реализован различным способом, например показанным на фиг.2. Блок управления 12 состоит из кнопки «Пуск» 12.1, первый контакт которой подключен к источнику напряжения питания блока, а второй подключен к входу дифференцирующей цепи 12.2, выход которой является четвертым управляющим выходом блока, сигнальному входу первого генератора тактовых импульсов 12.3 и S входу RS-триггера 12.13, R вход которого является установочным выходом блока, подключен к первому входу второго счетчика 12.11 и выходу схемы сравнения 12.14, выход регистра 12.15 подключен к сигнальному входу схемы сравнения 12.14, к первому входу которой подключен выход первого электронного ключа 12.12, являющийся вторым управляющим выходом блока, первый вход первого электронного ключа 12.12 подключен к выходу второго счетчика 12.11 и первому входу второго электронного ключа 12.17, выход которого является третьим управляющим выходом блока, второй вход второго электронного ключа 12.17 подключен к входу второго генератора тактовых импульсов 12.16 и инверсному выходу RS-триггера 12.13, прямой выход которого подключен к второму входу первого электронного ключа 12.12, второй вход второго счетчика 12.11 подключен к выходу элемента "ИЛИ" 12.10, второй и первый входы которого подключены к выходам соответственно второго генератора тактовых импульсов 12.16 и второго умножителя частоты импульсов 12.9, выход которого является первым управляющим выходом блока, вход второго умножителя частоты импульсов 12.9 подключен к выходу N-входового элемента "И" 12.8 и вторым входам первого генератора тактовых импульсов 12.3 и первого счетчика 12.4, первый вход которого подключен к выходу первого генератора тактовых импульсов 12.3 и входу элемента задержки 12.6, выход которого подключен к входу первого умножителя частоты импульсов 12.7, выход которого подключен к управляющему входу каждого из группы N элементов "И" 12.5, N выходов первого счетчика 12.4 являются информационными N выходами блока и подключены к соответствующим N входам N-входового элемента "И" 12.8 и к N входам каждого из группы N элементов "И" 12.5, причем реверсивные и прямые входы блока N-входового элемента "И" 12.8 соединены соответственно с реверсивными и прямыми входами каждого из группы N элементов "И" 12.5, выходы группы N элементов "И" 12.5 являются синхронизирующими N выходами блока.

Блок опроса предназначен для регистрации кодовых комбинаций, поступающих с N реверсивных регистров, что позволяет осуществить последовательный опрос всех первых, вторых и т.д. выходов реверсивных регистров 15.1-15.N. Он может быть реализован различным способом, например показанным на фиг.3. Блок опроса 16 состоит из N блоков элементов "ИЛИ-НЕ" 16.4, N элементов "ИЛИ" 16.5, N RS-триггеров 16.6, элемента "ИЛИ-НЕ" 16.7, второго счетчика 16.2, инвертора 16.3 и первого счетчика 16.1, счетный вход которого является входом блока, а сигнальный подключен к соответствующему входу второго счетчика 16.2 и R входам каждого из N RS-триггеров 16.6, n-й инверсный выход первого счетчика 16.1, где n=1, 2, …, N, подключен к первому входу n-го элемента "ИЛИ-НЕ" 16.4, первый инверсный выход первого счетчика 16.1 подключен к входу инвертора 16.3, выход которого подключен к первому входу второго счетчика 16.2, n-й инверсный выход которого подключен к n-му входу каждого из N элементов "ИЛИ-НЕ" 16.4, третья группа из N входов n-го элемента "ИЛИ-НЕ" 16.4 является n-й группой из информационных N входов блока, N выходов n-го элемента "ИЛИ-НЕ" 16.4 подключены к соответствующим N входам n-го элемента "ИЛИ" 16.5, выход n-го элемента "ИЛИ" 16.5 подключен к n-му входу элемента "ИЛИ-НЕ" 16.7 и к S входу n-го RS-триггера 16.6, а также является n-м выходом из N выходов блока, выход n-го RS-триггера 16.6 подключен к четвертому входу n-го элемента "ИЛИ-НЕ" 16.4.

Коммутатор частот предназначен для формирования колебания соответствующей гетеродинной частоты, поступающего с блока элементов "ИЛИ" 13, для перестройки приемника 1 на частоту соответствующего канала. Он может быть реализован различным способом, например показанным на фиг.4. Коммутатор частот 4 состоит из N электронных ключей 4.1, выходы которых объединены и являются выходом коммутатора частот, первый и второй входы n-го электронного ключа 4.1, где n=1, 2, …, N, подключены к n-м выходам соответственно формирователя сетки частот 4.3 и дешифратора 4.2, N входов которого являются N входами коммутатора частот, а вход формирователя сетки частот 4.3 подключен к выходу автогенератора 4.4.

Приемник 1 предназначен для приема сообщений. В устройстве автоматического поиска каналов радиосвязи приемник 1 предназначен для приема сигналов на определенной частоте соответствующего канала в процессе предварительного контроля каналов связи.

Преобразователь сигналов 2 предназначен для преобразования сигнала, полученного с выхода приемника 1, в кодовую комбинацию.

Дешифратор 3 предназначен для преобразования кодовой комбинации в определенное количество "единиц", пропорциональное уровню помехи.

Блок триггеров 5 предназначен для записи определенного количества "единиц" и сброса в нулевое состояние.

Первый блок элементов "И" 6 предназначен для подачи импульса на блок триггеров 5 для сброса триггеров блока триггеров 5 в нулевое состояние, при числе "единиц" с выхода дешифратора 3 меньше числа "единиц", записанных в блоке триггеров 5.

N-входовый элемент "ИЛИ" 7 предназначен для подачи сигнала на второй блок элементов "И" 9 и первый блок памяти 11 при закрытом состоянии элементов "И" первого блока элементов "И" 6.

Регистр сдвига 8 предназначен для подачи импульса положительной полярности с блока управления 12 (на втором этапе поиска каналов) и кодовой комбинации с преобразователя сигналов 2 на второй блок элементов "И" 9.

Второй блок элементов "И" 9 предназначен для передачи импульса с выхода одного из элементов "И" блока (его номер соответствует номеру анализируемого канала) на шифратор 10.

Шифратор 10 предназначен для преобразования импульса, поступившего с второго блока элементов "И" 9, в двоичную кодовую комбинацию, содержащую информацию о номере оптимального канала из числа пересмотренных.

Первый блок памяти 11 предназначен для записи номера оптимального канала.

Блок элементов "ИЛИ" 13 предназначен для передачи кодовой комбинации с информационных выходов блока управления 12 на вход коммутатора 4, а также для подключения выходов блока считывания 19 с входами коммутатора частот.

Компаратор 14 предназначен для сравнения значений пороговых напряжений.

N реверсивных регистров 15 предназначены для записи информации об уровне помехи в каналах.

Второй шифратор 17 предназначен для преобразования сигнала, поступившего с блока опроса 16, и передачи его в виде двоичного кода о номере канала с минимальным уровнем помехи в соответствующие номеру канала ячейки памяти второго блока памяти 18.

Блок памяти 18 предназначен для записи кодов номеров каналов в порядке возрастания уровня помехи.

Блок считывания 19 осуществляет (по команде блока управления 12) подключение выходов первых ячеек памяти второго блока памяти 18 через блок элементов "ИЛИ" 13 к входам коммутатора 4.

Кнопка пуск 12.1 предназначена для подачи напряжения на дифференцирующую цепь 12.2, запуска первого генератора тактовых импульсов 12.3, а также для установки RS-триггера в состояние логической "единицы".

Дифференцирующая цепь 12.2 предназначена для формирования импульса (по перепаду напряжения), поступающего на установочные входы реверсивных регистров 15.1-15.N.

Первый генератор тактовых импульсов 12.3 предназначен для генерации импульсов, поступающих на первый счетчик 12.4 и элемент задержки 12.6.

Первый счетчик 12.4 осуществляет подсчет числа тактовых импульсов.

Группа N элементов "И" 12.5 предназначены для синхронизации работы N реверсивных регистров 15.

Элемент задержки 12.6 предназначен для задержки импульса на время перестройки приемника 1 на очередную частоту.

Первый умножитель частоты импульсов 12.7 предназначен для умножения частоты тактовых импульсов с коэффициентом умножения nT=0,5Nрр, где Nрр - число разрядов N реверсивных регистров 15.

N-входовый элемент "И" 12.8 предназначен для сброса в нулевое состояние первого счетчика 12.4, а также для остановки работы первого генератора тактовых импульсов 12.3.

Второй умножитель частот импульсов 12.9 предназначен для умножения частоты тактовых импульсов с коэффициентом умножения nT=Nрр.

Элемент "ИЛИ" 12.10 предназначен для передачи 2nT тактовых импульсов с выхода второго умножителя частоты импульсов 12.9, а также для передачи импульсов с выхода второго генератора тактовых импульсов 12.16 на информационный вход второго счетчика 12.11.

Второй счетчик 12.11 предназначен для подсчета числа тактовых импульсов.

Первый электронный ключ 12.12 предназначен для подачи кодовой комбинации с выхода второго счетчика 12.11 на второй блок памяти 18, а также для обеспечения подключения ячеек памяти второго блока памяти 18 к соответствующим выходам шифратора 17.

RS-триггер 12.13 предназначен для запуска второго генератора тактовых импульсов 12.16.

Схема сравнения 12.14 предназначена для сравнения сигнала с выхода первого электронного ключа 12.12 с сигналом, поступающим на информационный вход схемы сравнения с регистра 12.15, и передачи итогового сигнала на сигнальный вход второго счетчика 12.11 и сброса его в нулевое состояние, а также для перевода RS-триггера 12.13 в состояние логического "нуля".

Регистр 12.15 предназначен для подачи информации о числе 2nT, равном разрядности N реверсивных регистров 15, на информационный вход схемы сравнения 12.14.

Второй генератор тактовых импульсов 12.16 предназначен для генерации тактовых импульсов, подаваемых на блок считывания 19 через элемент "ИЛИ" 12.10, второй счетчик 12.11 и второй электронный ключ 12.17.

Второй электронный ключ 12.17 предназначен для передачи импульсов, период следования которых соответствует времени анализа каналов связи на втором этапе поиска, на управляющий вход блока считывания 19.

Первый счетчик 16.1 предназначен для установки уровня "ноль" на первых инверсных входах N блоков элементов "ИЛИ-НЕ" при поступлении тактовых импульсов с блока управления 12 на счетный вход счетчика.

Второй счетчик 16.2 предназначен для установки уровня "единица" на каждом втором входе второго, третьего и последующего элемента "ИЛИ-НЕ" N блоков элементов "ИЛИ-НЕ" 16.4 при подаче напряжения с кнопки "Пуск" 12.1.

Инвертор 16.3 предназначен для преобразования сигнала постоянного тока, поступающего с первого инверсного выхода первого счетчика 16.1, в сигнал переменного тока, который подается на первый вход второго счетчика 16.2.

N блоков элементов "ИЛИ-НЕ" 16.4 предназначены для передачи логической "единицы" либо "нуля" (в зависимости от сигналов на входах N блоков элементов "ИЛИ-НЕ") на соответствующие входы N элементов "ИЛИ".

N элементов "ИЛИ" 16.5 предназначены для передачи логической "единицы" на первый информационный вход второго шифратора 17 и для передачи логического "нуля" на второй и последующие информационные входы второго шифратора 17 с соответствующих выходов N блоков элементов "ИЛИ-НЕ" 16.4.

N RS-триггеры 16.6 предназначены для передачи уровня "единица" на все четвертые входы элементов "ИЛИ-НЕ" блоков элементов "ИЛИ-НЕ" 16.4 для исключения повторного выбора номера канала при тактах опроса.

Элемент "ИЛИ-НЕ" 16.7 предназначен для получения уровня "ноль" и подачи его на разрешающий вход второго шифратора 17 (при наличии номера выбранного канала на выходе элемента "ИЛИ-НЕ" 16.7).

N электронных ключей 4.1N предназначены для подачи (в зависимости от кодовой комбинации, поступающей с блока элементов "ИЛИ" 13) на гетеродинный вход приемника 1 колебания соответствующей гетеродинной частоты.

Дешифратор 4.2 предназначен для преобразования и передачи кодовой комбинации с выходов элементов "ИЛИ" 13 на вторые входы N электронных ключей 4.1N.

Формирователь сетки частот 4.3 предназначен для выделения с опорного колебания высших гармонических составляющих и образования гетеродинных сигналов на частотах f1, f2, …, fN соответствующих электронных ключей 4.11÷4.1N.

Автогенератор 4.4 предназначен для формирования опорного синусоидального колебания.

В целом, блоки 14÷18 предназначены для обеспечения предварительного этапа поиска каналов связи. Блоки 2÷11 предназначены для обеспечения второго этапа поиска каналов радиосвязи. Их конструктивное выполнение представлено в прототипе.

Заявленное устройство работает следующим образом.

Поиск радиоканалов радиосвязи и выбор оптимального из них (по критерию минимума шумов и помех в канале) осуществляется в два этапа. На первом этапе все каналы предварительно контролируются в течение времени τ значительно меньше среднего времени Т, необходимого для вынесения решения о качестве канала, то есть τ<<Т. Затем все каналы упорядочиваются в порядке возрастания уровня помех в них так, что в первые ячейки памяти будет записан номер канала с минимальным уровнем помех, во вторую ячейку - канал с несколько большим уровнем помех и т.д. Если при упорядочивании встречаются каналы с разными уровнями помех, то они упорядочиваются произвольно. На втором этапе все каналы контролируются в течение времени T в порядке записи их номеров в ячейках памяти.

Работа устройства автоматического поиска каналов радиосвязи делится на два этапа.

На первом этапе поиска каналов сигнал на установочном выходе блока управления 12 отсутствует, следовательно, на установочные входы блока 5 триггеров и регистр 8 сдвига импульс положительной полярности не подается и тракт выбора канала в составе блоков 6÷11 находится в состоянии покоя. С информационных выходов блока управления 12 через блок элементов "ИЛИ" 13 на вход коммутатора частот 4 поступает кодовая комбинация, соответствующая номеру первого канала. По команде, поступающей с четвертого управляющего выхода блока управления 12, регистры 15.1÷15.N блока N реверсивных регистров 15 устанавливаются в исходное состояние, при котором на триггерах данных регистров записано определенное число "единиц" (как правило, равное половине разрядности регистров 15.1÷15.N). С выхода приемника 1, настроенного на частоту первого канала, напряжение помехи UX1 подается на вход компаратора 14, где сравнивается с двумя значениями пороговых напряжений UA и UB, причем UA<UB.

Если напряжение помехи в канале превышает верхний порог, то есть UX1>UB, то положительное напряжение будет присутствовать на первом выходе компаратора 14, подключенного к суммирующим входам реверсивных регистров 15.1÷15.N блока N реверсивных регистров 15. В этом случае при поступлении тактовых импульсов на синхронизирующий вход регистра 15.1 число "единиц" в нем будет уменьшаться.

В случае если UA<UX1<UB, то положительное напряжение на выходах компаратора будет отсутствовать, а при поступлении тактовых импульсов на реверсивный регистр 15.1 число "единиц" на его выходах не изменится.

После поступления nT тактовых импульсов, частота следования которых и их количество nT определяют время (предварительного контроля канала), на вход первого реверсивного регистра 15.1, то есть после того как в реверсивном регистре 15.1 будет записана информация об уровне помехи в первом канале, происходит перенастройка частоты приемника на частоту второго канала. А именно: с информационных выходов блока управления 12 поступит кодовая комбинация на первую группу входов блока элементов "ИЛИ" 13 и с его выхода на коммутатор частот 4.

Коммутатор частот 4 работает следующим образом.

Формирователь сетки частот 4.3 выделяет с опорного колебания высшие гармонические составляющие и образует гетеродинные сигналы на частотах f1, f2, …, fN соответствующих электронных ключей 4.11÷4.1N, вторые входы которых подключены к выходам дешифратора 4.2. В зависимости от кодовой комбинации, поступающей с блока элементов "ИЛИ" 13 на вход дешифратора 4.2, будет открыт один из электронных ключей 4.1N. На гетеродинный вход приемника 1 поступит колебание соответствующей гетеродинной частоты, то есть приемник 1 перестроится на частоту второго канала для предварительного контроля. Результат сравнения напряжения помехи во втором канале UX2 с пороговыми уровнями UA и UB отобразится в определенном количестве "единиц" на выходе второго реверсивного регистра 15.2. Далее аналогичным образом контролируется третий и последующие каналы.

После предварительного анализа N-го канала с первого управляющего выхода блока управления 12 поступает импульс на счетный вход блока опроса 16.

Блок опроса 16 работает следующим образом. Напряжением с кнопки 12.1 "Пуск" счетчики 16.1, 16.2 устанавливаются в начальное состояние, a RS-триггеры 16.61-16.6N - в нулевое. При поступлении первого тактового импульса с первого управляющего выхода блока управления 12 на счетный вход первого счетчика 16.1 на первом инверсном выходе первого блока элементов "ИЛИ-НЕ" 16.4 вырабатывается уровень "ноль", а на остальных инверсных выходах первого счетчика 16.1, которые соединены со всеми первыми входами элементов "ИЛИ-НЕ" N блоков элементов "ИЛИ-НЕ" 16.41÷16.4N, также устанавливается уровень "ноль". На остальных инверсных выходах второго счетчика 16.2, которые соединены с каждым вторым входом второго, третьего и последующего элемента "ИЛИ-НЕ" N блоков элементов "ИЛИ-НЕ" 16.41÷16.4N соответственно, установится уровень "единица". На третьи входы элементов "ИЛИ-НЕ" N блоков элементов "ИЛИ-НЕ" 16.41÷16.4N подается информация с выходов N реверсивных регистров 15.1÷15.N (первый выход реверсивного регистра 15.1 соединен с первым входом третьей группы входов первого элемента "ИЛИ-НЕ" блока элементов "ИЛИ-НЕ" 16.41, второй - с третьим входом второго элемента "ИЛИ-НЕ" блока элементов "ИЛИ-НЕ" 16.41 и т.д.). Такая реализация блока 16 опроса позволяет осуществить последовательный опрос всех первых, вторых и т.д. выходов N реверсивных регистров 15.1-15.N.

Выход каждого RS-триггера 16.61÷16.6N соединен со всеми четвертыми входами элементов "ИЛИ-НЕ" каждого блока элементов "ИЛИ-НЕ" 16.41÷16.4N соответственно.

При отсутствии "единицы" на первом выходе какого-либо из N реверсивных регистров 15.1-15.N, например 15.1, что соответствует равенству нулю напряжения помехи в первом канале, то есть UX1=0 при первом такте (как было показано выше), на остальных входах первого элемента "ИЛИ-НЕ" блока элементов "ИЛИ-НЕ" 16.41 будет подан уровень "ноль". На выходе данного элемента "ИЛИ - НЕ" N блоков элементов "ИЛИ-НЕ" вырабатывается уровень "единица", на выходах остальных элементов "ИЛИ-НЕ" блока элементов "ИЛИ-НЕ" 16.41 вырабатывается уровень "ноль". Выходы этих элементов блока "ИЛИ-НЕ" 16.41 соединены со всеми входами блока элементов "ИЛИ" 16.51 соответственно. На его выходе вырабатывается уровень "единица", который поступит на RS-триггер 16.61 и установит его в единичное состояние. С выхода RS-триггера 16.61 уровень "единица" подается на все четвертые входы элементов "ИЛИ-НЕ" блока элементов "ИЛИ-НЕ" 16.41 и тем самым исключается повторный выбор номера канала при следующих тактах опроса. Набор выбранного канала (уровень "единица") поступает на первый информационный вход второго шифратора 17 (в данном случае с выхода блока элементов "ИЛИ" 16.51). На остальных выходах блоков элементов "ИЛИ" 16.51÷16.5N установится уровень "ноль", который поступает на входы второго шифратора 17. С выхода второго шифратора 17 информация в виде двоичного кода о номере канала с минимальным уровнем помехи, например первого, поступает в первые ячейки памяти второго блока памяти 18.

Все выходы блоков элементов "ИЛИ" 16.51÷16.5N соединены с N входами блока элементов "ИЛИ-НЕ" 16.7 соответственно. При наличии в выходном коде "единицы", то есть при наличии номера выбранного канала, на выходе блока элементов "ИЛИ-НЕ" 16.7 вырабатывается уровень "ноль", который подается на разрешающий вход второго шифратора 17. Таким образом, исключается возможность записи во второй блок памяти 18 нулевых комбинаций. После этого опрашивается первый выход реверсивного регистра 15.2 и т.д. После опроса, таким образом, всех первых выходов N реверсивных регистров 15 опрашиваются вторые и т.д. выходы N реверсивных регистров 15.1-15.N.

Такая реализация блока опроса 16 позволяет "различить" и последовательно записать во второй блок памяти 18 кодовые комбинации, соответствующие номерам каналов с равными уровнями помехи. Во втором блоке памяти 18, таким образом, будут записаны коды номеров каналов в порядке возрастания уровня помехи, причем код номера канала с минимальным уровнем помехи будет записан в первые ячейки памяти второго блока памяти 18, с несколько большим уровнем помехи - во вторые ячейки памяти второго блока памяти 18 и т.д. После этого начинается второй этап контроля и поиска оптимальных каналов.

По команде с блока управления 12 блок считывания 19 осуществляет подключение выходов первых ячеек памяти второго блока памяти 18 через блок элементов "ИЛИ" 13 к входам коммутатора частот 4. Приемник 1 настраивается на частоту, соответствующую каналу, признанному наилучшим на первом этапе контроля. Одновременно с началом второго этапа поиска с блока управления 12 поступает импульс в блок триггеров 5 и на установочный вход регистра сдвига 8.

Сигнал с выхода приемника 1 поступает на преобразователь 2, с выхода которого полученная кодовая комбинация поступает на вход дешифратора 3, преобразующего кодовую комбинацию в определенное количество "единиц", пропорциональное уровню помехи. Эти "единицы" поступают на инверсные входы элементов "И" первого блока элементов "И" 6. Вторые входы первого блока элементов "И" 6 соединены с выходами блока триггеров 5.

После анализа первого из записанных во второй блок памяти 18 канала приемник 1 настраивается на частоту канала, номер которого записан во вторых ячейках памяти второго блока памяти 18 и т.д.

Если уровень помехи в анализируемом канале окажется ниже уровней помех всех предыдущих каналов, то есть число "единиц" с выхода дешифратора 3 окажется меньше числа "единиц", записанных в блоке триггеров 5, то откроется такое количество элементов "И" первого блока элементов "И" 6, которое равно разности чисел, записанных в блоке триггеров 5, и поступающих с выхода дешифратора 3 "единиц". Импульсы с выходов первого блока 6, поступая на входы сброса блока триггеров 5, перебросят триггеры в нулевое состояние.

Если уровень помехи анализируемого канала не является самым низким среди всех пересмотренных каналов, то элементы "И" первого блока элементов "И" 6 не откроются.

Если уровень помехи в анализируемом канале окажется ниже, чем в пересмотренных каналах, то на первые входы элементов "И" второго блока элементов "И" 9 с выхода элемента "ИЛИ" 7, входы которого соединены с выходами элементов "И" первого блока элементов "И" 6, поступит импульс. Так как первые входы каждого из элементов "И" второго блока элементов "И" 9 соединены с выходами одного из триггеров регистра сдвига 8 соответственно, то с выхода одного из элементов "И" второго блока элементов "И" 9 (его номер соответствует номеру анализируемого канала) на первый шифратор 10 поступит импульс. Этот импульс преобразуется в двоичную кодовую комбинацию, содержащую информацию о номере оптимального канала из числа просмотренных, которая записывается в первый блок памяти 11.

Блок управления 12 работает следующим образом. При нажатии кнопки "Пуск" 12.1 напряжение подается на дифференцирующую цепь 12.2, формирующую по перепаду напряжения импульс, поступающий на установочные входы реверсивных регистров 15.1÷15.N. Кроме того, напряжением с кнопки "Пуск" 12.1 запускается первый генератор тактовых импульсов 12.3. Подсчет числа тактовых импульсов осуществляет первый счетчик 12.4, с выхода которого кодовая информация поступает на информационные выходы блока управления 12 и далее на первую группу входов блока элементов "ИЛИ" 13. Выходы первого счетчика 12.4 соединены также с соответствующими входами N элементов "И" группы N элементов "И" 12.51÷12.5N (по числу реверсивных регистров 15.1÷15.N). Импульс с выхода первого генератора тактовых импульсов 12.3 поступает также на элемент задержки 12.6 (для задержки на время перестройки приемника 1 на очередную частоту) и далее на первый умножитель частоты импульсов 12.7, коэффициент умножения nT которого равен половине числа разрядов N реверсивных регистров 15.1÷15.N. С выхода первого умножителя частоты импульсов 12.7 тактовые импульсы поступают на управляющий (первый) вход каждого из элементов "И" группы N элементов "И" 12.51÷12.5N. При этом откроется тот элемент "И" 12.5j (jє[1,N]), номер которого соответствует кодовой комбинации с выхода первого счетчика 12.4, и уже с открытого элемента "И" 12.5j группы N элементов "И" 12.51÷12.5N nT тактовых импульсов поступят на синхронизирующий вход соответствующего реверсивного регистра 15.1÷15.N.

При формировании N+1-го тактового импульса первым генератором тактовых импульсов 12.3 соответствующая кодовая комбинация откроет элемент "И" 12.8, прямые и инверсные входы которого соединены с соответствующими выходами первого счетчика 12.4. Импульс с выхода N-входового элемента "И" 12.8 поступит на второй вход первого генератора тактовых импульсов 12.3 (для его остановки) и первого счетчика 12.4 (для сброса в "нулевое" состояние), а также на вход второго умножителя частоты импульсов 12.9, коэффициент умножения 2nT которого равен числу разрядов N реверсивных регистров 15.1÷15.N. 2nT тактовых импульсов с выхода второго умножителя частоты импульсов 12.9 поступает на первый управляющий выход блока управления 12 и далее на счетный вход блока опроса 16, а также через элемент "ИЛИ" 12.10 на второй (информационный) вход второго счетчика 12.11. Кодовая комбинация с выхода второго счетчика 12.11 через открытый первый электронный ключ 12.12 поступает на второй управляющий выход блока управления 12 и далее на управляющий вход второго блока памяти 18, обеспечивая подключение соответствующих ячеек памяти к выходу шифратора 17. Первый электронный ключ 12.12 открывается при подаче напряжения с прямого выхода RS-триггера 12.13, устанавливаемого в состояние логической "единицы" напряжением, подаваемым на S-вход при нажатии кнопки "Пуск" 12.1.

Выходной сигнал первого электронного ключа 12.12 поступает также на сигнальный вход схемы сравнения 12.14, на информационный вход которой поступает информация с выхода регистра 12.15 о числе 2nT, равном разрядности N реверсивных регистров 15.1÷15.N. При появлении на выходе второго счетчика 12.11 кодовой комбинации, соответствующей числу 2nT, с выхода схемы сравнения 12.14 поступает сигнал на сигнальный вход второго счетчика 12.11 (для сброса его в "нулевое" состояние), на R вход RS-триггера 12.13 (для перевода его в состояние логического "нуля") и на установочные входы блока триггеров 5 и регистра сдвига 8.

Напряжение с инверсного выхода RS-триггера 12.13 запускает второй генератор тактовых импульсов 12.16. Импульсы, период следования которых Т соответствует времени анализа каналов связи на втором этапе поиска, с выхода генератора тактовых импульсов 12.16 через элемент "ИЛИ" 12.10 поступают на информационный вход второго счетчика 12.11, с выхода которого кодовая комбинация через открытый второй электронный ключ 12.17 поступает на третий управляющий выход блока управления 12 и далее на управляющий вход блока считывания 19. Открытое состояние второго электронного ключа 12.17 обеспечивается подачей напряжения на его второй вход с инверсного выхода RS-триггера 12.13. Таким образом, приемник будет перестраиваться на частоты в порядке убывания вероятностей их пригодности для ведения связи. Предлагаемое устройство реализует алгоритм двухэтапного поиска оптимальных каналов автоматами с линейной тактикой (в качестве которых выступают N реверсивных регистров 15.1÷15.N, подключенных к выходу компаратора 14), осуществляющими последовательную процедуру Вальда.

К примеру, Т - время полного анализа одного канала T=1 сек, τ - время предварительного анализа одного канала во много раз меньше времени полного анализа одного канала T τ=0,05 сек. При числе каналов N, например, N=10. Время их полного анализа прототипом будет равно 10 сек.

В разработанном устройстве время предварительного анализа этих каналов равно 0,5 сек. Для вынесения окончательного решения о качестве канала необходим второй этап контроля в течение времени T в уже установленном порядке возрастания напряжения помехи. Общее время, необходимое для нахождения оптимального канала, составляет не более 1,5 сек. Итак прототип "находит" оптимальный канал за 10 сек, а разработанное устройство - за 1,5 сек. В среднем, данная процедура поиска позволяет уменьшить время поиска оптимальных каналов в 1,5…2,4 раза по сравнению с устройствами, реализующими последовательный просмотр каналов. Устройство обеспечивает увеличение достоверности выбора оптимального канала за счет двухэтапного анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2014 |

|

RU2563145C1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОТКЛОНЕНИЙ ПАРАМЕТРОВ ПРИ ДОПУСКОВОМ КОНТРОЛЕ | 2016 |

|

RU2617982C1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАДИОЭЛЕКТРОННЫХ ОБЪЕКТОВ | 2009 |

|

RU2413977C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| Устройство для измерения температуры | 1985 |

|

SU1315831A1 |

| Устройство для программного управления позиционного типа | 1983 |

|

SU1158976A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

Изобретение относится к технике передачи дискретной информации, радиотехнике и может использоваться в радиостанциях. Техническим результатом является повышение быстродействия выбора оптимального канала связи путем двухэтапного контроля резервных каналов. Устройство автоматического поиска каналов радиосвязи состоит из приемника, преобразователя сигналов, дешифратора, коммутатора частот, блока триггеров, первого блока элементов "И", N-входового элемента "ИЛИ", регистра сдвига, второго блока элементов "И", первого шифратора и первого блока памяти. Новыми в устройстве автоматического поиска каналов радиосвязи являются блок управления, блок элементов "ИЛИ", компаратор, N реверсивных регистров, блок опроса, второй шифратор, второй блок памяти и блок считывания. Устройство реализует алгоритм двухэтапного поиска оптимальных каналов. В устройстве время предварительного анализа этих каналов равно 0,5 сек. Для вынесения окончательного решения о качестве канала необходим второй этап контроля в течение времени Т в уже установленном порядке возрастания напряжения помехи. Общее время, необходимое для нахождения оптимального канала, составляет не более 1,5 сек. В среднем, данная процедура поиска позволяет уменьшить время поиска оптимальных каналов в 1,5…2,4 раза по сравнению с устройствами, реализующими последовательный просмотр каналов. Устройство обеспечивает увеличение достоверности выбора оптимального канала за счет двухэтапного анализа. 3 з.п. ф-лы, 4 ил.

1. Устройство автоматического поиска каналов радиосвязи, содержащее приемник, информационный вход которого является входом устройства, а выход подключен к входу преобразователя сигналов, информационные N выходы которого подключены к соответствующим информационным N входам дешифратора, информационные N выходы которого подключены к соответствующим инверсным N входам первого блока элементов И, N выходов которого подключены к соответствующим входам N-входового элемента ИЛИ и N входам сброса блока триггеров, N выходов которого подключены к информационным N входам первого блока элементов И, управляющий выход преобразователя сигналов подключен к управляющему входу дешифратора и управляющему входу регистра сдвига, N выходов которого подключены к соответствующим N входам второго блока элементов И, N выходов которого подключены к соответствующим N входам первого шифратора, N выходов которого подключены к соответствующим N входам первого блока памяти, N выходов которого являются выходами устройства, гетеродинный вход приемника подключен к выходу коммутатора частот, отличающееся тем, что дополнительно введен блок элементов ИЛИ, N выходов которого подключены к соответствующим N входам коммутатора частот, а первая и вторая группы информационных входов, по N входов каждая, блока элементов ИЛИ подключены соответственно к N выходам блока считывания и N информационным выходам блока управления, установочный выход которого подключен соответственно к установочному входу блока триггеров и установочному входу регистра сдвига, третий управляющий выход блока управления подключен к управляющему входу блока считывания, второй управляющий выход блока управления подключен к управляющему входу второго блока памяти, первый управляющий выход блока управления подключен к управляющему входу блока опроса, выход приемника подключен к входу компаратора, суммирующий и вычитающий выходы которого подключены соответственно к суммирующим и вычитающим входам каждого из N реверсивных регистров, четвертый управляющий выход блока управления подключен к установочным входам N реверсивных регистров, а N синхронизирующие выходы блока управления подключены к синхронизирующим входам соответствующих N реверсивных регистров, N выходы каждого из которых подключены к соответствующей группе из N входов блока опроса, N информационных выходов которого подключены к соответствующим N информационным входам второго шифратора, разрешающий вход которого подключен к разрешающему выходу блока опроса, N выходов второго шифратора подключены к соответствующим N входам второго блока памяти, N выходов которого подключены к информационным N входам блока считывания.

2. Устройство по п.1, отличающееся тем, что блок управления состоит из кнопки «Пуск», первый контакт которой подключен к источнику напряжения питания блока, а второй подключен к входу дифференцирующей цепи, выход которой является четвертым управляющим выходом блока, сигнальному входу первого генератора тактовых импульсов и S входу RS-триггера, R вход которого является установочным выходом блока, подключен к первому входу второго счетчика и выходу схемы сравнения, выход регистра подключен к сигнальному входу схемы сравнения, к первому входу которой подключен выход первого электронного ключа, являющийся вторым управляющим выходом блока, первый вход первого электронного ключа подключен к выходу второго счетчика и первому входу второго электронного ключа, выход которого является третьим управляющим выходом блока, второй вход второго электронного ключа подключен к входу второго генератора тактовых импульсов и инверсному выходу RS-триггера, прямой выход которого подключен к второму входу первого электронного ключа, второй вход второго счетчика подключен к выходу элемента ИЛИ, второй и первый входы которого подключены к выходам соответственно второго генератора тактовых импульсов и второго умножителя частоты импульсов, выход которого является первым управляющим выходом блока, вход второго умножителя частоты импульсов подключен к выходу N-входового элемента И и вторым входам первого генератора тактовых импульсов и первого счетчика, первый вход которого подключен к выходу первого генератора тактовых импульсов и входу элемента задержки, выход которого подключен к входу первого умножителя частоты импульсов, выход которого подключен к управляющему входу каждого из группы N элементов И, N выходов первого счетчика являются информационными N выходами блока и подключены к соответствующим N входам N-входового элемента И и к N входам каждого из группы N элементов И, причем реверсивные и прямые входы блока N-входового элемента И соединены соответственно с реверсивными и прямыми входами каждого из группы N элементов И, выходы группы N элементов И являются синхронизирующими N выходами блока.

3. Устройство по п.1, отличающееся тем, что блок опроса состоит из N блоков элементов ИЛИ-НЕ, N элементов ИЛИ, N RS-триггеров, элемента ИЛИ-НЕ, второго счетчика, инвертора и первого счетчика, счетный вход которого является входом блока, а сигнальный подключен к соответствующему входу второго счетчика и R входам каждого из N RS-триггеров, n-й инверсный выход первого счетчика, где n=1, 2, …, N, подключен к первому входу n-го элемента ИЛИ-НЕ, первый инверсный выход первого счетчика подключен к входу инвертора, выход которого подключен к первому входу второго счетчика, n-й инверсный выход которого подключен к n-му входу каждого из N элементов ИЛИ-НЕ, третья группа из N входов n-го элемента ИЛИ-НЕ является n-й группой из информационных N входов блока, N выходов n-го элемента ИЛИ-НЕ подключены к соответствующим N входам n-го элемента ИЛИ, выход n-го элемента ИЛИ подключен к n-му входу элемента ИЛИ-НЕ и к S входу n-го RS-триггера, а также является n-ым выходом из N выходов блока, выход n-го RS-триггера, подключен к четвертому входу n-го элемента ИЛИ-НЕ.

4. Устройство по п.1, отличающееся тем, что коммутатор частот состоит из N электронных ключей, выходы которых объединены и являются выходом коммутатора частот, первый и второй входы n-го электронного ключа, где n=1, 2, …, N, подключены к n-ым выходам соответственно формирователя сетки частот и дешифратора, N входов которого являются N входами коммутатора частот, а вход формирователя сетки частот подключен к выходу автогенератора.

| RU 2007149423 А, 10.07.2009 | |||

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА СИГНАЛОВ РАДИОСТАНЦИЙ, СМЕНЯЮЩИХ РАБОЧИЕ ЧАСТОТЫ | 2005 |

|

RU2308151C1 |

| RU 99115980 A, 10.05.2001 | |||

| EP 1858168 A1, 21.11.2007. | |||

Авторы

Даты

2012-05-10—Публикация

2011-07-12—Подача