Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств,

Известны усилители считывания, поэволяющие осуществить съем сигнала и

его выделецие при протекании тока по одной разрядной линии l . 2.

Наиболее близким по технической суи аости к данному изобретению является усилитель, содержащий последовательно соединенные ключ и генератор тока, к вы ходу которого подключен эмиттерный п о&торитель, выход эмиттерногоповте итепя подключен к дифференцирующему элементу, и дефференциальный каскад.

Целью изобретения является повышение быстродействая усилителя путем уменьше.ния динамического сопротивления выходной цепи.

Поставленная цель достигается тем, что усилитель считывания содержит ускоряющий элемент, включенный между эмиттерным повторителем и дифференциальным каскадом; кроме .ого ускоряющий элемент -выполнен в виде управляемого, диоднса о моста с разделительными конденсаторами.

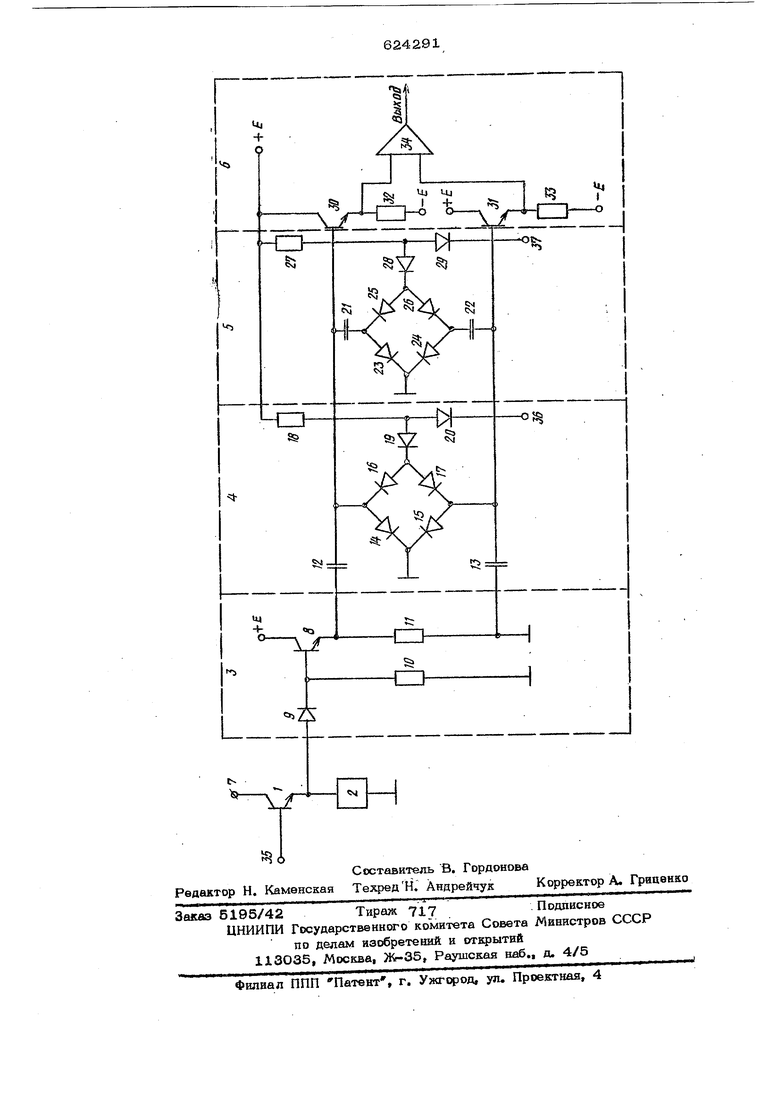

Усилитель считывания показан на чертеже.

Он состоит из последовательно соединенных ключа 1 и генератора тока 2, эмиттернпго повторителя 3, дифференцирующего элемента 4, ускоряющего элемета 5, дифференциальнсмго каскада 6. Разрядная совмещенная щина подключается к входу 7.

Змиттерный повторитель 3 имеет тра зистор 8, диод 9, резисторы 10, 11. Диффере1щируютий элемент 4 состоит из конденсаторов 12, 13, моста на диодах 14, 15, 16, 17 исхемы управления диодным мостом, содержащей резистор 18 и диоды 19 и 2О.

Ускоряющий элемент 5 состоит из разделительнь1Х конденсаторов 21, 22, управляемого моста на диодах 23, 24, 25, 26 в схемы управления диодным мостом, состоящей из резистора 27 и диодов 28, 29. Дифферешдаальный каскад 6 состоит иа эмиттерных повторителей, которые содержат транзисторы 30, 31, и резисторов 32, 33 и дифференцишшного усилителя 34. Усилитель работает следующим образом. При протекании тока по разрядной цеп пощслючелной к входу 7, ток протекает через ключ 1, открытый сигналом по входу 35, и генератор 2. При этом на генераторе тока образуется напряжение от разрядного тока (пьедестал) и выделяется сигнал с ферритового сердечника, при протекании через него адресного тока. Сш-нал ни помехе типа пьедестал поступает через эмиттерпьи повторитель иа схему дифферегщяровашш. . Время диф ферещировапия пьедестала зависит от постоянной времени ди фэренцируюшей це ПК,Величина постоянной, .времени путем подклгочения ускоряющего элемента може быть уме}1ьшена в два и более раз. Емкости 21 и 22 являются разделительным имеют 6onbiL jio величину и поэтому мало сопротивление иа фронте диффереццирова ния пьедестала. Сопротивление открььтых диодов 23, 24, 25, 26 при дифференцировании 1 ьедестала м/зло По окончании диффёренщфованяя на входы 36, 37 подается у11ра.йпя1ощий сиг нал и-диоды 14 - 17, 23 20 запираю ся на время прохолодения полезного сигнала с (|)ерритового сердечника, постоянная резко вазрастает, 11опезны без дифферегщировашш проходит на диф крегщиальный каскад. Введение дополяительных ускоряющих элементов уменьшает динамическое сопротивление цепи дифференцирования помехи типа пье дестап, тем самым уменьшается постояй ная времени, а следовательно, уменьшает ся время выборки и амплитуда помех. Применение предлагаемого усилителя позволяет ПОВЫСИТЬ быстродействие оперативных запоминающих устройств, выполненных по системе 2.5 U/2W. Формула изобретения 1.Усилитель считывания ддя оперативного запоминающего устройства, содер жащий последовательно соединенные ключ и генератор тока, к выходу которого подключен эмиттерный повторитель, выход эмиттерного повторителя подключен к дифференднруюшему элементу, и диффэрекциальный каскад, отличаювдийс я тем, что, с целью повышения быстро действия усилителя путем уменьшения динамического сопротивления выходной цепи, он содержит ускоряющий элемент, включенный между эмиттерным повторителем и ди4)4юренциальным каскадом. 2.Усилительпо п. 1, отличаюct н и с я тем, что ускоряющий элемент выполнен в видеуправляемого диодного моста с разделительными конденсаторами. Источники информации, принятые во внимание при экспертизе: 1.Патент США № 3663887, кл, 330-13, 1972. 2.Заявка N 2336262 f24, JKJU Q 11 С 7/02, .18,03.76, ito которой принято, решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания для магнитногоОпЕРАТиВНОгО зАпОМиНАющЕгО уСТРОйСТВА | 1976 |

|

SU803007A2 |

| Усилитель считывания для магнитного оперативного запоминающего устройства | 1976 |

|

SU739644A1 |

| Устройство для считывания информации | 1979 |

|

SU809356A1 |

| Устройство считывания информации для доменной памяти | 1990 |

|

SU1751813A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Повторитель сигнала переменного и постоянного напряжения | 2022 |

|

RU2776256C1 |

| Блок считывания информации для магнитного запоминающего устройства | 1980 |

|

SU953665A1 |

| Расширитель импульсов | 1977 |

|

SU687575A1 |

| Регулятор температуры | 1989 |

|

SU1780083A1 |

| Способ искробезопасного дистанционного питания и устройство для его осуществления | 1985 |

|

SU1305398A1 |

Авторы

Даты

1978-09-15—Публикация

1976-11-12—Подача