Изобретение относится к вычислительной технике и может быть исполь вано в запоминающих устройствах на ферритовых сердечниках. Известно устройство для,считывани информации в оперативных запомингиощих устройствах на ферритовых сердеч никах с совмещенной разрядной обмоткой. Оно содержит эмиттерный повторитель, ускоряющий элемент, диффере цируюЕ(ий каскад и днфференцигшьный усилитель. Ускоряющий элемент и управляемый резистор в дифференцирующем каскаде выполнены с использовани ем диодного моста ij . Недостатком усилителя считывания является низкое быстродействие, опре деляемое тем, что процесс запирания диодов моста имеет большую длительность. Наиболее близким по технической сущности к предлагаемому является устройство, содержащее управляемый ключ на двух полевых транзисторах, стоки которых соединены с входгики дифференциального усилителя и через конденсаторы с выходами предваритель ного усилителя, истоки - с земляной шиной, а затворы соединены с управля ющей шиной 2 . Недостатком такого устройства является низкое быстродействие, определяемое малым соотношением постоянных времени трактов прохоящения полезного сигнала и сигнала помехи. Условие малого исхгикеиия полезного сигнала определяет выбор конденсаторов с большой емкостью при использовании дифференциапь{шх усилителей в интегральном исполнении, входное сопротивление которых составляет единицы килоом. Это приводит X увеличению постоянной времени в тракте прохождении сигнала помехи. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство дпя считывания информёщии, содержащее предварительный усилитель, входы соединены с соответствующими входными шинами устройства, два накопительных элемента, первые ш хводы котсчрых соединены с соответствующими выходами предварительного усилителя, управляемой ключ, первый вход которого соединен с шинсЛ управления, второй вход - с шиной нулевого потенциала, первый выход c вторым выводом первого накопительного элемента, второй выход - с вторым выводом второго накопительного элемента, и дифференциальный усилител выходы которого соединены с соответ -. ствующими выходными шинами устройства введены два согласующих элемента, первый вывод первого иэ которых подключен к первому выходу ключа, а второй вывод к первому входу дифференциального усилителя, первый вывод второго согласукя11его элемента подключен к второму выходу ключа, а второй вывод к второму входу дифференциального усилителя.

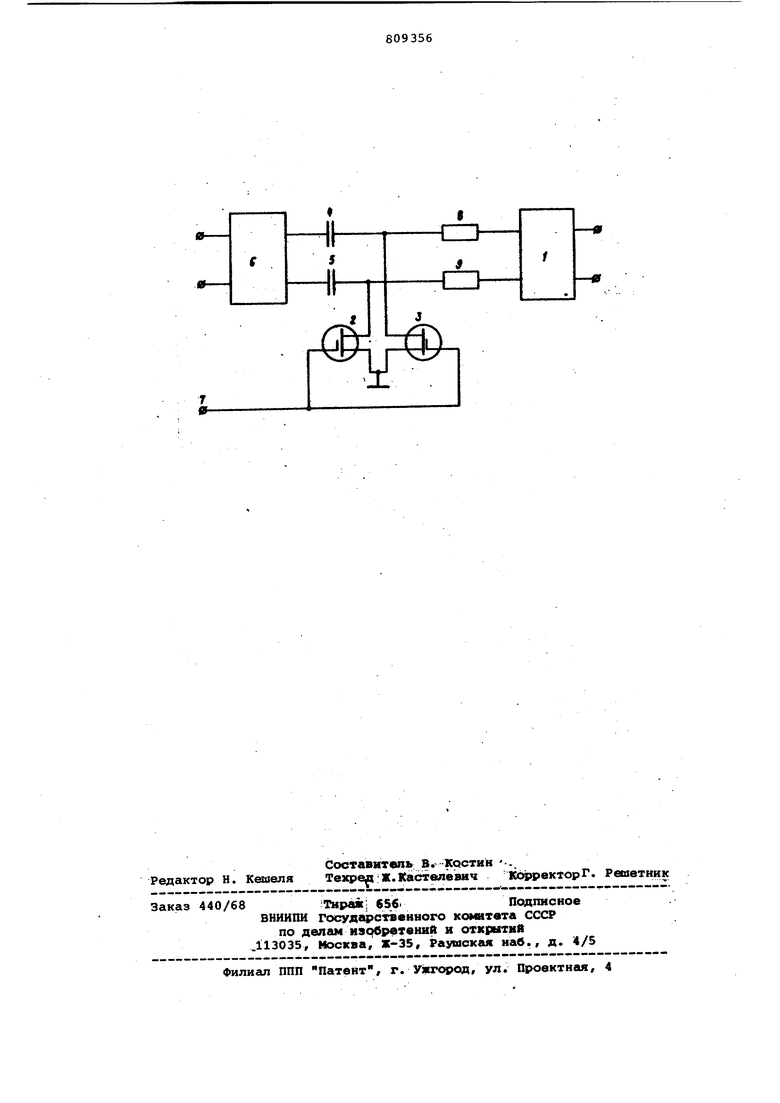

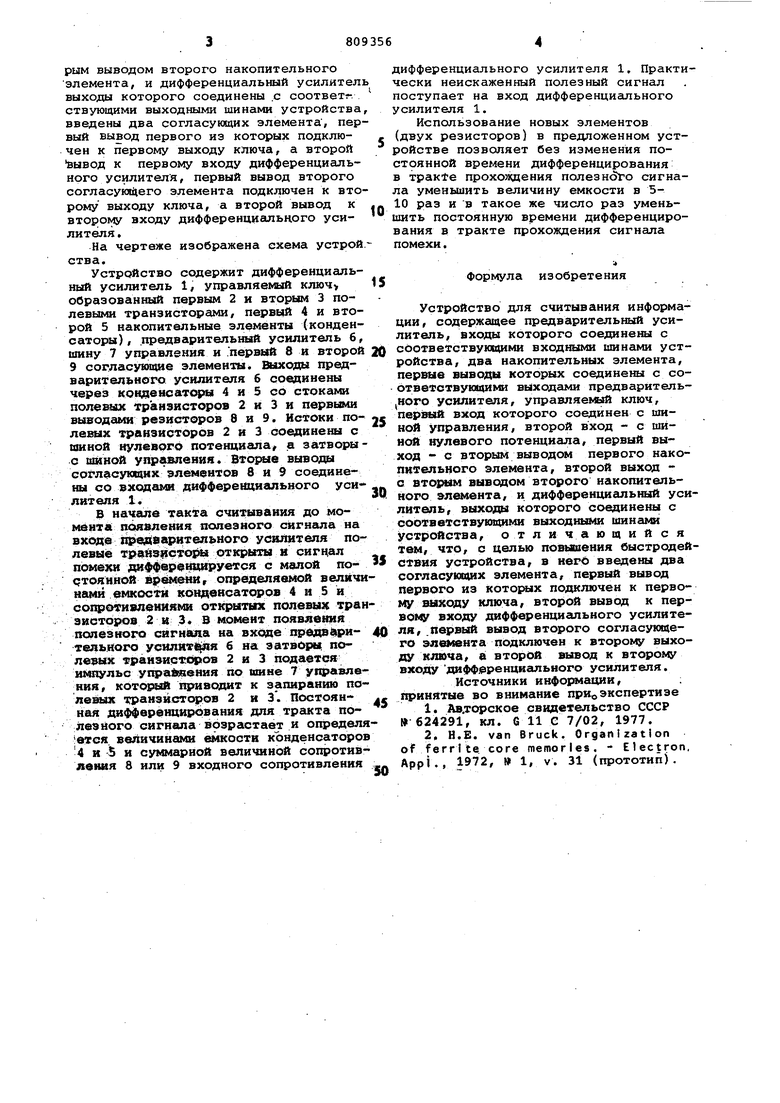

На чертеже изображена схема устройства.

Устройство содержит дифференциальный усилитель 1, управляемый ключ образованный первым 2 и вторым 3 полевыми транзисторами, первый 4 и второй 5 накопительные элементы (конденсаторы) , .предварительный усилитель б, шину 7 управления и .перзаЛ 8 и второй 9 согласующие элементы. Выходы предварительного усилителя б соединены через ко1щемсаторы 4 и 5 со стоками ПОПОВЫХ Фраиэисторов 2 и 3 и первыми выводами резисторов 8 и 9. Истоки полевых транзисторов 2 и 3 соединены с шиной нулевохо потенциала а затворы с шиной управления. Вторые выводы согласующих элементов 8 и 9 соединены со входами дифференциального уси лителя 1.

В начале такта считывания до момента яояаления полезного сигнала на входе 10 едааритеяьного усилителя полевые т9а з|1стой: открыты и сигнал помехи диффврейвирувтся с малой по ;тоянной BpeMeitttr определяемой величинами емкости конденсаторов 4 и 5 и сотфсйтвяениями открытых полевых транэистброа 2 tt 3. В момент появления полезного сигн1ша на вхоще предалительного уснлиФ1 11я 6 на затворы; по левых транзистсзров 2 и 3 подается икшульс у1фай ения по шине 7 управления, кОто1 аШ приводит К запиранию попеваж транзисторов 2 и 3. Постоянная дифференцирования для тракта полезного сигнала В1Озрастает и определя|ется величинами емкости конденсаторов 4 к 5 и суммарной величиной сопротивления 8 или 9 входного сопротивления

дифференциального усилителя 1, Практически неискаженный полезный сигнал поступает на вход дифференциального усилителя 1.

Использование новых элементов (двух резисторов) в предложенном устройстве позволяет без изменения пострянной времени дифференцирования в прохождения полезного сигнала уменьшить величину емкости в 510 раз и в такое же число раз уменьшить постоянную времени дифференцирования в тракте прохождения сигнала помехи.

4

Формула изобретения

Устройство для считывания информации, содержащее предварительный усилитель, входы которого соединены с соответствующими входными шинами устройства, два накопительных элемента, первые выводы которых соединены с собтветствующими выходами предваритель ного усилителя, управляемый ключ, пер}вый вход которого соединен с шиной управления, второй вход - с шиной нулевого потенциала, первый выход - с вторым выводом первого накопительного элемента, второй выход с вторым выводом второго накопительного элшвента, и дифференциальный усилитель, выходы которого соединены с соответствующими выходными шинами Устройства, отличающийся тем, что, с целью повышения быстродействия устройства, в него введе 1Ш два согласукхоих элемента, первый вывод первого из которых подключен к первому выходу ключа, второй вывод к первому входу дифференцисшьного усилителя, первый вывод второго согласующего элемента подключен к второму выходу ключа, а второй вывод к второму входу дифф эренциального усилителя.

Источники информации, : принятые во внимание при экспертизе

1.Ав.торское свидетельство СССР №624291, кл. G 11 С 7/02, 1977.

2.Н.Б. van Bruck. Organization of ferrite core memories. - Electron, Appi., 1972, 1, V. 31 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из накопителя доменной памяти | 1986 |

|

SU1515943A1 |

| Компаратор напряжения | 1989 |

|

SU1653149A1 |

| Ультразвуковой расходомер | 2024 |

|

RU2838625C1 |

| Устройство для считывания информации из доменной памяти | 1988 |

|

SU1558226A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Тензометрическое устройство | 1979 |

|

SU870965A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU830582A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU943853A1 |

Авторы

Даты

1981-02-28—Публикация

1979-06-14—Подача