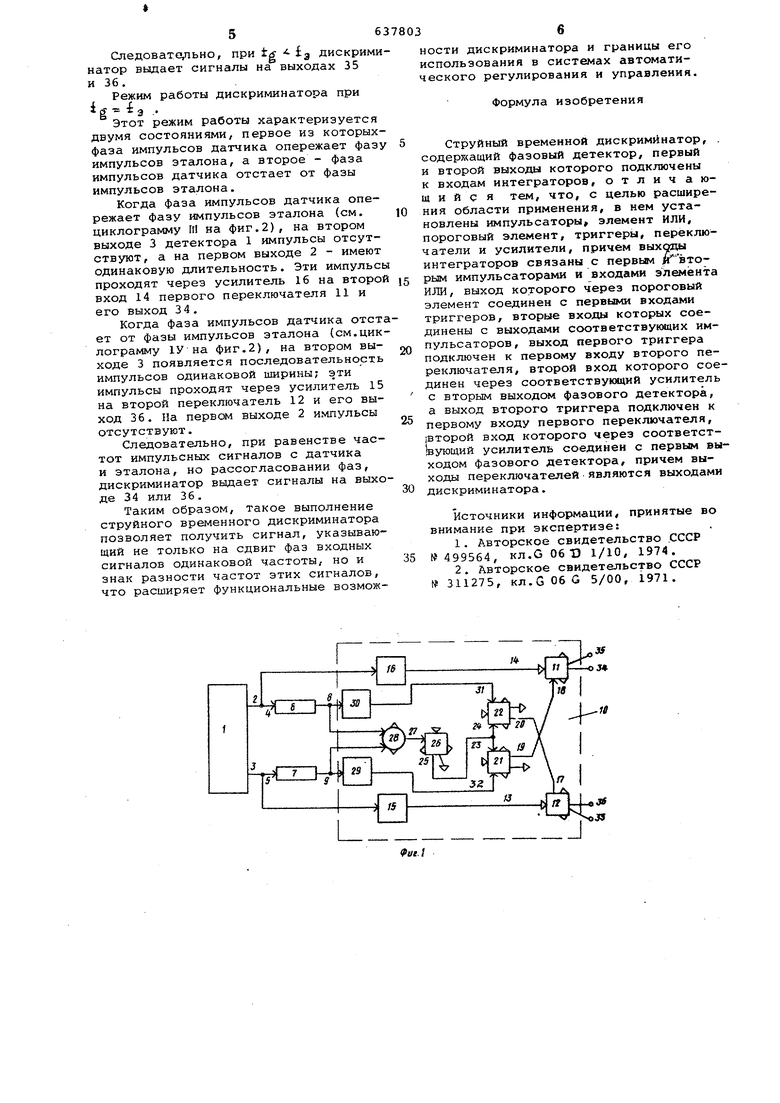

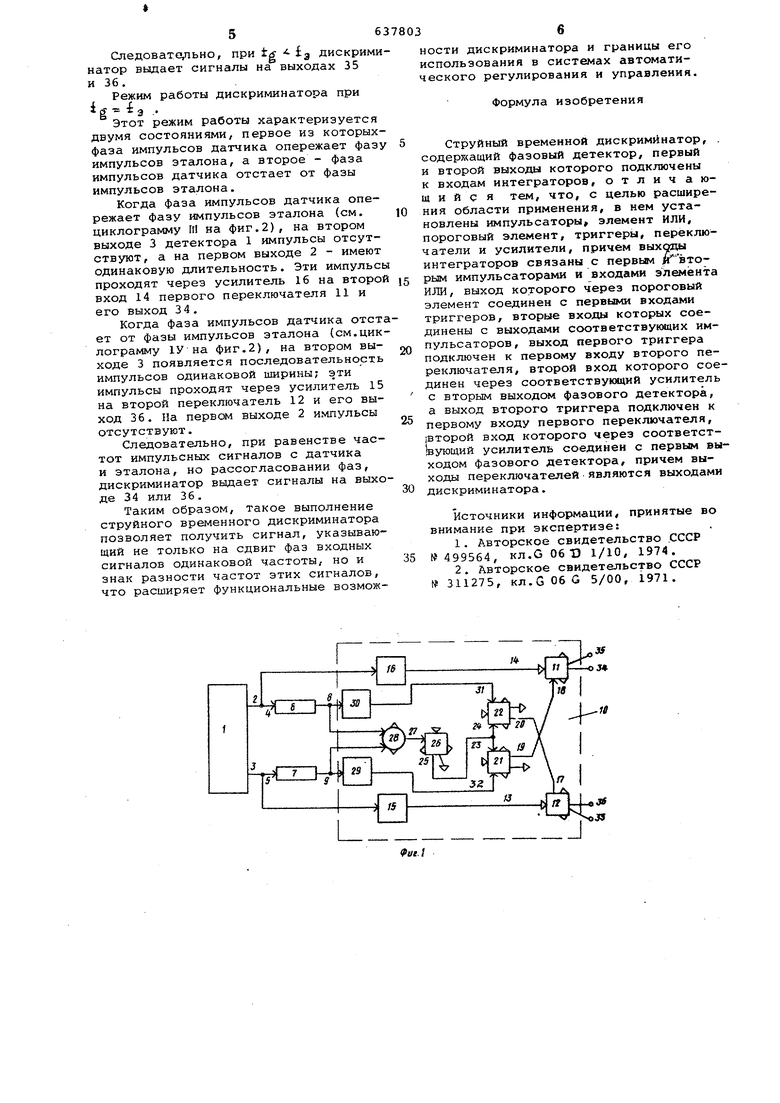

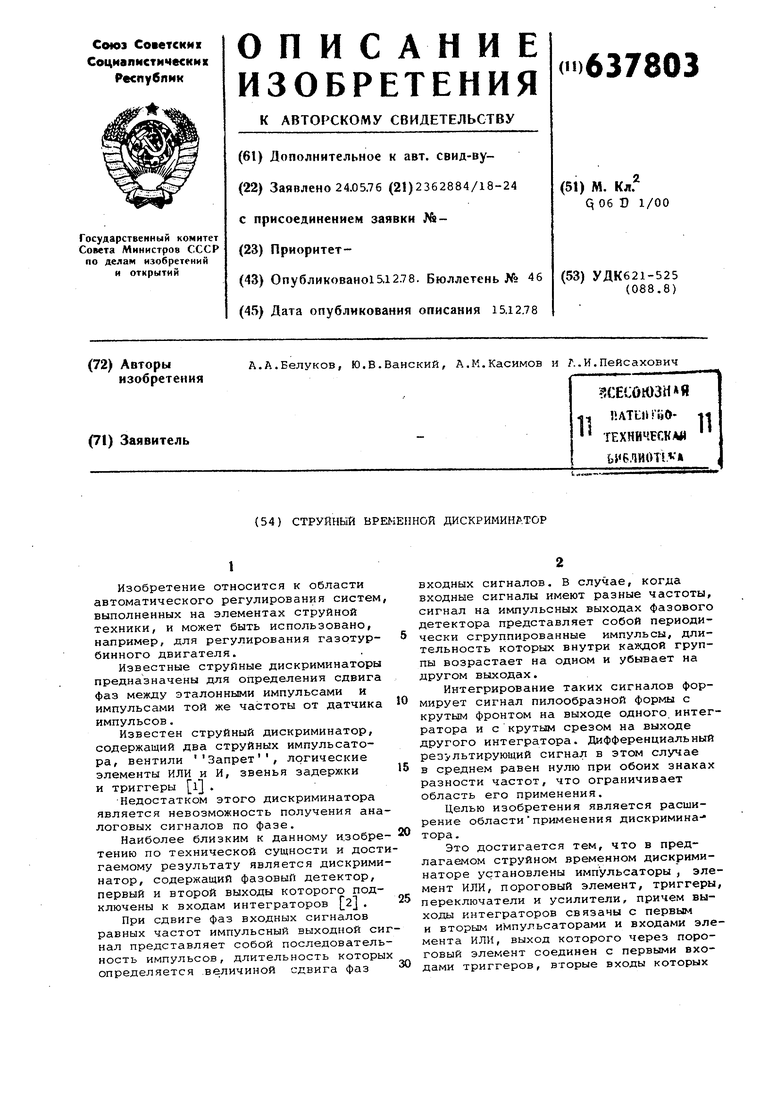

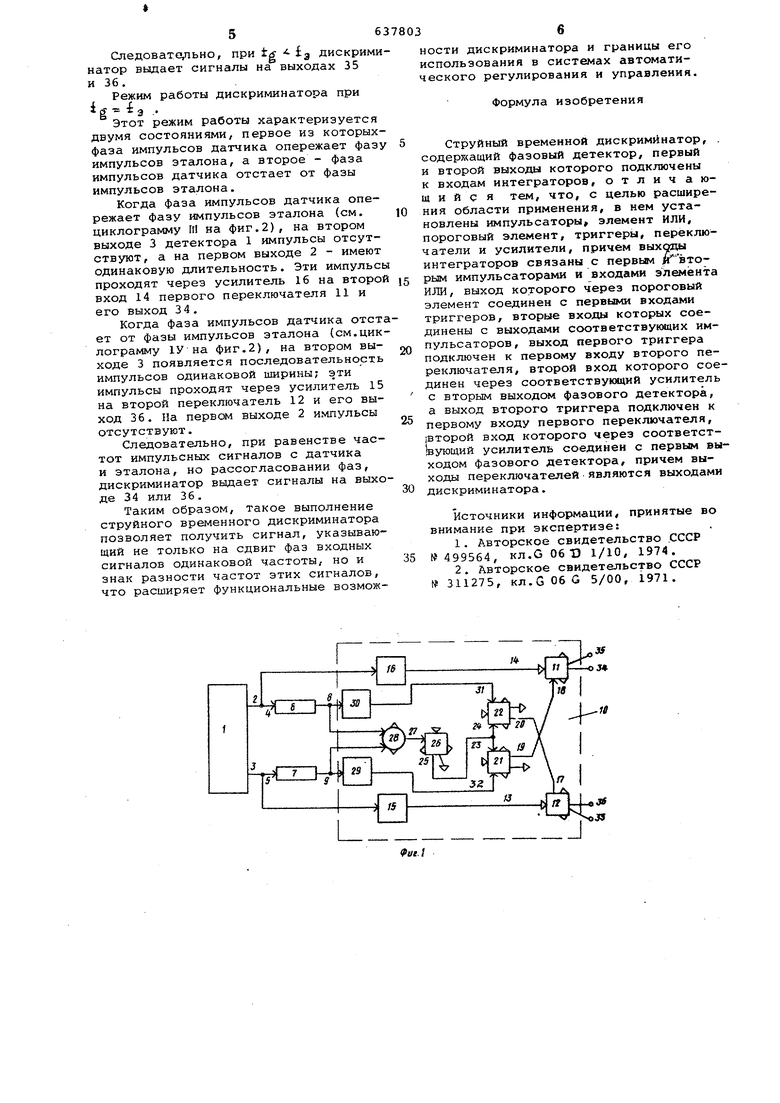

соединены с выходами соответствующих импульсаторов, выход первого триггера подключен к первому входу второго переключателя, второй вход которого сое динен через соответствующий усилитель с вторым выходсм фазового детектора, а выход второго триггера подключен к первому входу первого переключателя, второй вход которого через соответствующий усилитель соединен с пер вым выходом фазового детектора, причем выходы переключателей являются выходами дискриминатора. На фиг.1 показан схема струйного временного дискриминатора;на фиг.2 циклограмма его работы на различных режимах, где I - циклограмма работы дискриминатора при частоте датчикаf больше частоты этaлoнaiз(f Ig) 11 - при ig-i э ; W - , но фаза импульсов датчика опережает фаз импул.сов эталона; 1У - при ig э но фаза импульсов датчика отсйет от фазы импульсов эталона. Струйный временной дискриминатор содержит фазовый детектор 1, первый и второй 3 выходы которого подклкгчен к входам 4, 5 интеграторов 6 и 7. Выходы 8 и 9 интеграторов б и 7 подключены к блоку 10 коммутации детект ра 1, выполненного, в виде первого ii и второго 12 переключателей р вторые входы 13 и 14 которых связаны через усилители 15 и 16 с первым 2 и вторы 3 выходами фазового детектора 1. Первые входы 17 и 18 переключателей 12 и 11 соответственно соединены с выходами 19, 20 второго 21 и перво го 22 триггеров, первые входы 23 и 2 которых подключены к выходу 25 порогового элемента 26, а вход 27 через элемент ИЛИ 2.8 - к выходам 8 и 9 интеграторов б и 7; последние подклю чены через второй 29 и первый 30 импульсаторы к вторым входам 31 и 32 триггеров 22 и 21. Входы 33, 34 и 35,36 переключателей 11,12 являются выходами дискриминатора. Струйный дискриминатор работает в следующих четырех режимах. Рехсим работы .дискриминатора при {см. фиг.2, циклограмма 1). В исходном состоянии в момент t длительность импульсов на первом 2 и втором 3 выходах фазового детектора и сигналы на выходах 8 и 9 интеграто ров 6 и 7 минимальны, следовательно, уровень сигнала на входе 27 меньше порога срабатывания элемента 26, и сигнал с выхода 25 проходит на первы входы 23 и 24 триггеров 21 и 22, при чем сигналы на первых входах 17, 18 переключателей 12 и 11 и выходах 19, 20 триггеров 21 и 22 отсутствуют. В последующие моменты времени на первом 2 и втором 3 выходах фазового детектора 1 поочередно появляются периодически сгруппированные импульс .причем вначале появляется группа импульсов нарастающей длительности на первом выходе 2, а затем - группа имульсов убывающей длительности на втором выходе 3. Импульсы с первого выхода 2 через усилитель 16 проходят во второй вход 14 первого переключателя 11 следовательно, на выход 34 дискриминатора. Такие же импульсы интегратора 7 преобразуются в нарастающий сигнал пилообразной формы с крутым задним фронтом, который. проходя через первый импульсатор 30, формирует на втором входе 31 первого триггера 22 импульс, переключающий его струю питания на выход 20. Поэтому,когда импульсы на первом выходе 2 фазового детектора 1 исчезают, а на втором 3 - появляются, они через усилитель 15 проходят на второй вход 13 второго переключателя 12, выходной сигнал под воздействием импульса на выходе 20 первого триггера 22,пришеда1его на первый вход 17 второго переключателя 12,появляется на выходе 33 дискриминатора, а на выходе 34 сигнал исчезает. Следовательно, при л ig дискриминатор выдает сигналы на выходах 33 и 34. Каждый следующий цикл начинается с исходного состояния t . Режим работы дискриминатора при itf -i. fg (см. фиг.2, циклограмма II). Исходное состояние дискриминатора (момент tg ) аналогично состоянию дискриминатора в первом режиме работы. В последующие моменты времени на первом 2 и втором 3 выходах фазового детектора 1 поочередно появляются периодически сгруппированные импульсы, причем вначале появляется группа импульсов нарастающей длительности на втором выходе 3,а затем - группа импульсов убывающей длительности на первом выходе 2. Импульсы со второго выхода 3 через усилитель 15 проходят на второй вход 13 второго переключателя 12, и,следовательно, на выход 36 дискриминатора. Эти же импульсы интегратора б преобразуются в нарастающий сигнал пилообразной формы с крутым задним фронтом, который, проходя через второй импульсатор 29 формирует на втором входе 32 второго триггера 21 импульс,переключающий струю питания на выход 19. Поэтому, когда импульсы на втором выходе 3 исчезают, а на первом выходе 2 появляются, они через усилитель 16 проходят во второй вход 14 переключателя 11; выходной сигнал под воздействием импульса на выходе 19 второго триггера 21, прищедшего на первый вход 18 переключателя 11, появляется на выходе 35 дискриминатора, а на выходе 36 сигнал исчезает. Затем процесс работы повторяется. Следовате/1ьно, при tg «. 3 дискрим натор вьщает сигналы на выходах 35 и 36. Режим работы дискриминатора при g - i 3 . Этот режим работы характеризуется двумя состояниями, первое из которых фаза импульсов датчика опережает фаз импульсов эталона, а второе - фаза импульсов датчика отстает от фазы импульсов эталона. Когда фаза импульсов датчика опережает фазу импульсов эталона (см. циклограмму Ш на фиг.2), на втором выходе 3 детектора 1 импульсы отсутствуют, а на первом выходе 2 - имеют одинаковую длительность. Эти импульс проходят через усилитель 16 на второ вход 14 первого переключателя 11 и его выход 34. Когда фаза импульсов датчика отст ет от фазы импульсов эталона (см.цик лограмму 1У на фиг.2), на втором выходе 3 появляется последовательность импульсов одинаковой ширины; эти импульсы проходят через усилитель 15 на второй переключатель 12 и его выход 36. На первом выходе 2 импульсы отсутствуют. Следовательно, при равенстве частот импульсных сигналов с датчика и эталона, но рассогласовании фаз, дискриминатор выдает сигналы на выхо де 3 4 или 36. Таким образом, такое выполнение струйного временного дискриминатора позволяет получить сигнал, указывающий не только на сдвиг фаз входных сигналов одинаковой частоты, но и знак разности частот этих сигналов, что расширяет функциональные возможности дискриминатора и границы его использования в системах автоматического регулирования и управления. Формула изобретения Струйный временной дискриминатор, . содержащий фазовый детектор, первый и второй выходил которого подключены к входам интеграторов, о т л и ч а ющ и и с я тем, что, с целью расширения области применения, в нем установлены импульсаторы элемент ИЛИ, пороговый элемент, триггеры, переключатели и усилители, причем выходы интеграторов связаны с первым к вторым импульсаторами и входами элемента ИЛИ, выход которого через пороговый элемент соединен с первыми входами триггеров, вторые входы которых соединены с выходами Соответствующих импульсаторов, выход первого триггера подключен к первому входу второго переключателя, второй вход которого соединен через соответствукмдий усилитель с вторым выходом фазового детектора, а выход второго триггера подключен к первому входу первого переключателя, :второй вход которого через соответстЬующий усилитель соединен с первым выходом фазового детектора, причем выходы переключателейявляются выходами дискриминатора. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство .СССР №499564, кл.00613 1/10, 1974. 2.Авторское свидетельство СССР № 311275, кл.С 06 G 5/00, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Струйный временный диксриминатор | 1977 |

|

SU691837A1 |

| Струйный фазовый дискриминатор | 1982 |

|

SU1013933A1 |

| Струйный временной дискриминатор | 1977 |

|

SU631910A1 |

| Струйное управляющее устройство | 1980 |

|

SU941927A1 |

| Устройство для подавления помех | 1983 |

|

SU1095419A1 |

| КОМПЛЕКСНЫЙ ИЗМЕРИТЕЛЬ ДАЛЬНОСТИ | 1992 |

|

RU2018861C1 |

| Струйный временной дискриминатор | 1974 |

|

SU499564A1 |

| Устройство контроля комбинационных составляющих сигнала нелинейного четырехполюсника | 1985 |

|

SU1264111A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для воспроизведения с носителя магнитной записи | 1988 |

|

SU1624517A1 |

/

Авторы

Даты

1978-12-15—Публикация

1976-05-24—Подача