Изобретение относится к электронной технике и может быть использовано в производстве вакуумных интегральных схем (ВИС).

Известная вакуумная интегральная схема, содержащая две диэлектрические подложки, на первой из которых выполнены катодно-подогревательные, а на второй - анодно-сеточные элементы, причем во второй подложке внутри углублений имеются консольные навесы, на которых в местах расположения активных элементов выполнены пленочные щелевые сетки, а аноды и пассивные элементы размещены в одной плоскости на дне углублений. Такая конструкция ВИС позволяет создавать логические цифровые схемы с активными элементами диодного и триодного типов.

К существенным недостаткам рассматриваемой конструкции ВИС следует отнести сложность построения на ее основе линейных схем, в частности, операционных усилителей, широкополосных усилителей, усилителей постоянного тока и других устройств, обусловленную отсутствием в конструкции схемы микроприборов тетродного и пентодного типов, что значительно ограничивает функциональные возможности ВИС такой конструкции.

Цель изобретения - расширение функциональных возможностей схемы.

Это достигается тем, что в предлагаемой схеме на подложке в катодно-подогревательными элементами напротив консольных навесов по краям сквозных щелей выполнены дополнительные пленочные щелевые сетки. Кроме того, на подложке с анодно-сеточными элементами под анодами выполнены дополнительные пленочные сетки.

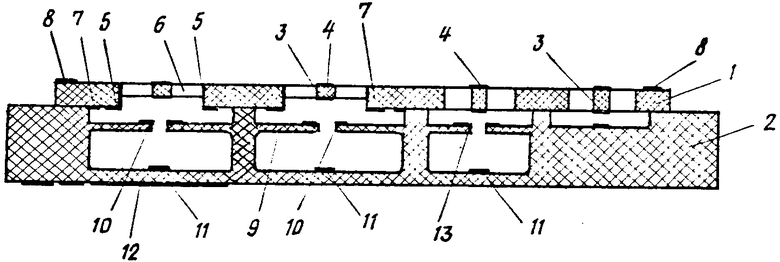

На чертеже изображена предлагаемая схема.

Вакуумная интегральная схема содержит две диэлектрические подложки 1 и 2, наложенные непосредственно друг на друга. На подложке 1 размещены термокатоды с пленочным керном 3 и активным покрытием, пленочные подогреватели 4, дополнительные пленочные управляющие щелевые сетки 5, расположенные по краям сквозных щелей 6, изолирующих катоды косвенного накала с локальными зонами разогрева от массива подложки, резисторы 7 и проводящие пленочные дорожки 8. На подложке 2 на консольных навесах 9 внутри углублений подложки в местах расположения микротетродов и микропентодов размещены пленочные экранирующие щелевые сетки 10, на дне углублений - пленочные аноды 11, в том числе и аноды микротриодов и микродиодов.

На противоположной стороне подложки непосредственно под анодами в местах расположения микропентодов размещены пленочные антидинатронные сетки 12. Кроме того, на подложке 2 выполнены пленочные управляющие щелевые сетки 13 микротриодов, размещенные на соответствующих консольных навесах. При наложении подложек 1 и 2 друг на друга и соединении их шпильками через сквозные отверстия в подложках, например, методом пайки, две сетки совместно с катодом и анодом образуют объемные микротетродные ячейки, а три сетки совместно с катодом и анодом - объемные пентодные микроячейки. Вакуумная интегральная схема, представленная на чертеже содержит по одному микротетроду и микропентоду.

Из чертежа видно, что во избежание возможного запыления продуктами распыления катода вертикальных сеток той части углублений в подложке 2, которая расположена под консольными навесами, и образования в результате этого паразитной проводимости между управляющей и экранирующей сетками, участки подложки 1, на которых сформированы пленочные управляющие щелевые сетки, размещены над углублениями в подложке 2, образуя защитные козырьки над вертикальными стенками углублений.

Наличие сквозных щелей в подложке 1 способствует увеличению резистивной развязки между катодом и управляющей сеткой микротетродов и микропентодов.

Для осуществления коммутации сеток и анодов микротетродов и микропентодов через токопроводящие пленочные покрытия с их контактными площадками и с соответствующими пассивными элементами схемы, последние, так же, как и контактные площадки, размещаются либо в плоскости анода, либо в плоскости соответствующих сеточных электродов. Вся схема вакуумируется в общем корпусе.

Предлагаемый ВИС может использоваться, например, в качестве согласующего усилителя постоянного тока и работает по его принципу.

Такое конструктивное выполнение ВИС позволяет повысить качество и существенно расширить функциональные возможности схем за счет построения объемных тетродных и пентодных микроячеек, существенно снизить величины межэлектродных емкостей активных элементов ВИС и повысить тем самым коэффициент усиления, широкополосность, а также предельную частоту усиления повысить в несколько раз степень интеграции элементов схем в результате построения объемных многоэлектродных структур микроприборов на двух диэлектрических подложках.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВАКУУМНАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1976 |

|

SU602040A2 |

| ВАКУУМНАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1974 |

|

SU529687A1 |

| СПОСОБ ПОЛУЧЕНИЯ ДИЭЛЕКТРИЧЕСКИХ ПОДЛОЖЕК | 1974 |

|

SU524440A1 |

| ЭЛЕКТРОВАКУУМНЫЙ ПРИБОР | 1972 |

|

SU434861A1 |

| ГИБРИДНОЕ ИНТЕГРАЛЬНОЕ ВАКУУМНОЕ МИКРОПОЛОСКОВОЕ УСТРОЙСТВО | 1994 |

|

RU2073936C1 |

| АВТОЭЛЕКТРОННЫЙ МИКРОТРИОД И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2006 |

|

RU2360321C2 |

| Способ изготовления катодного узла микротриода с трубчатым катодом из нанокристаллической алмазной пленки (варианты) | 2022 |

|

RU2794423C1 |

| МИКРОПРОФИЛЬ СТРУКТУРЫ ВАКУУМНОЙ ИНТЕГРАЛЬНОЙ СВЧ-СХЕМЫ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2009 |

|

RU2404481C1 |

| КАСКАДНЫЙ УСИЛИТЕЛЬ СВЧ | 2016 |

|

RU2634185C1 |

| КАСКАДНЫЙ РАСПРЕДЕЛЁННЫЙ УСИЛИТЕЛЬ СВЧ | 2016 |

|

RU2634186C1 |

Авторы

Даты

1994-08-15—Публикация

1977-04-04—Подача