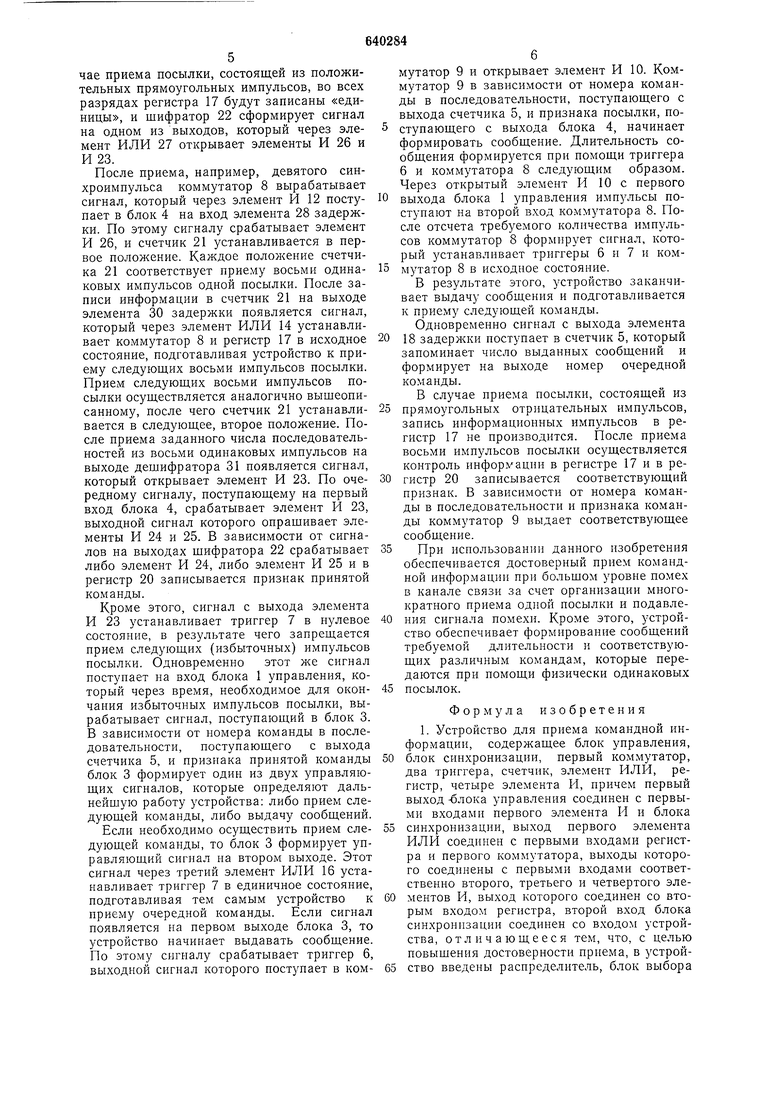

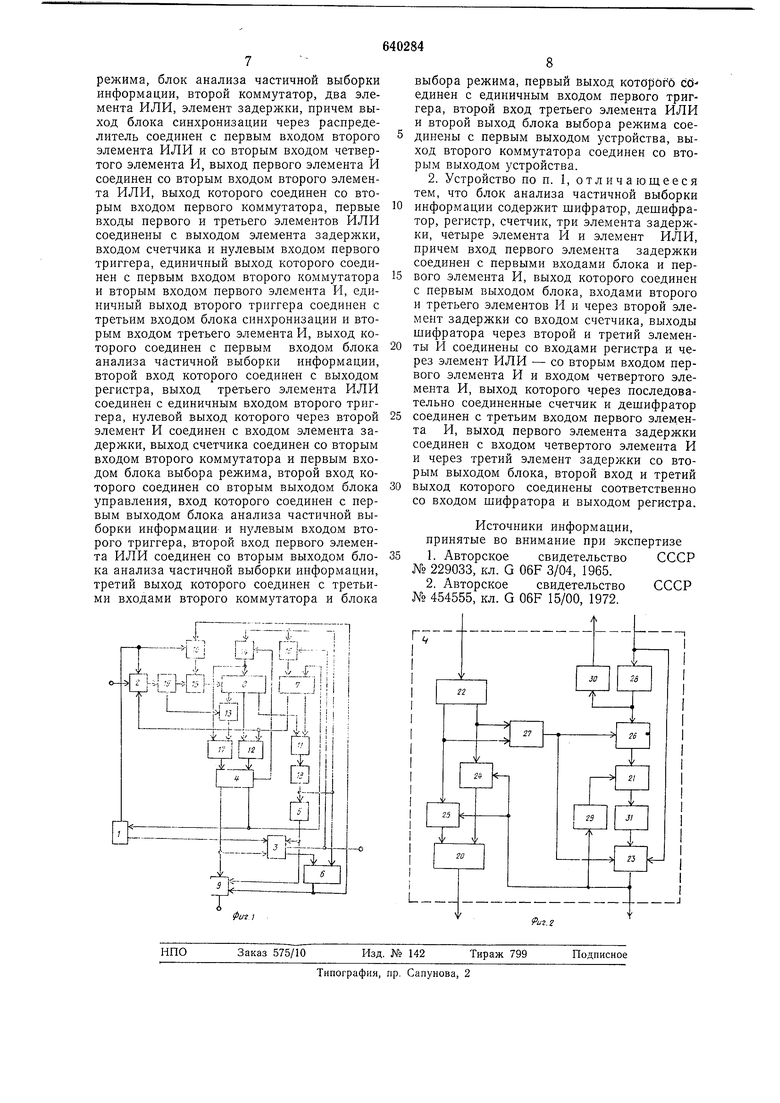

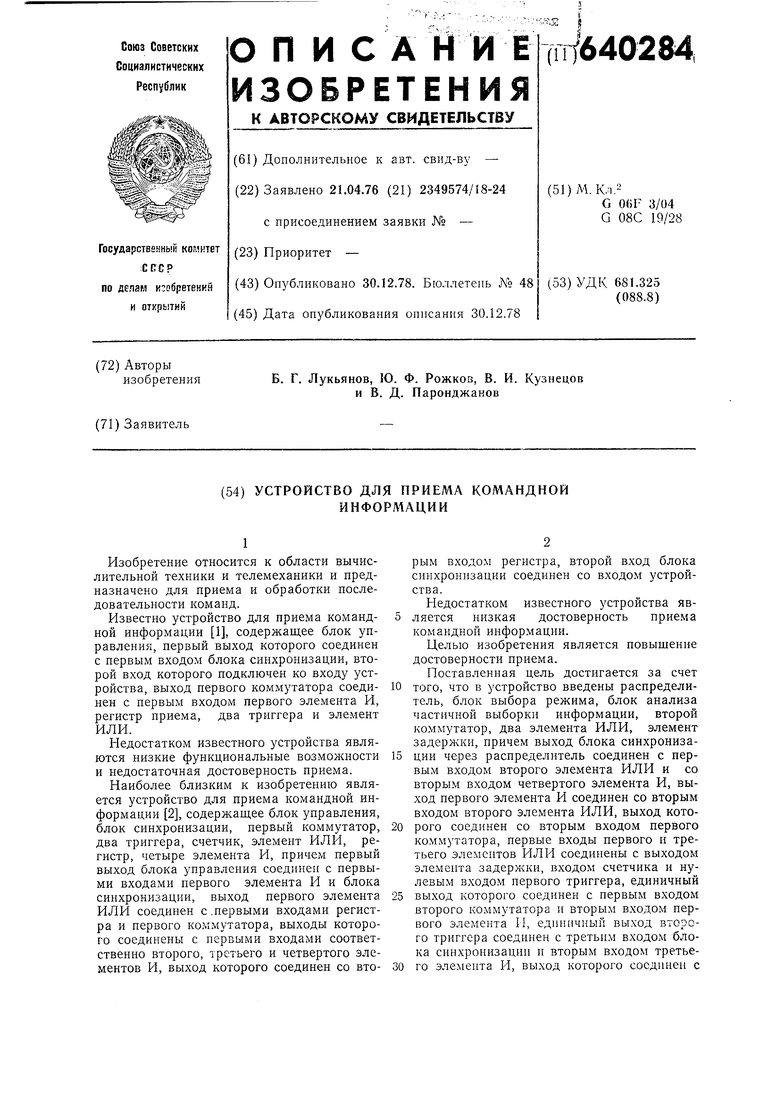

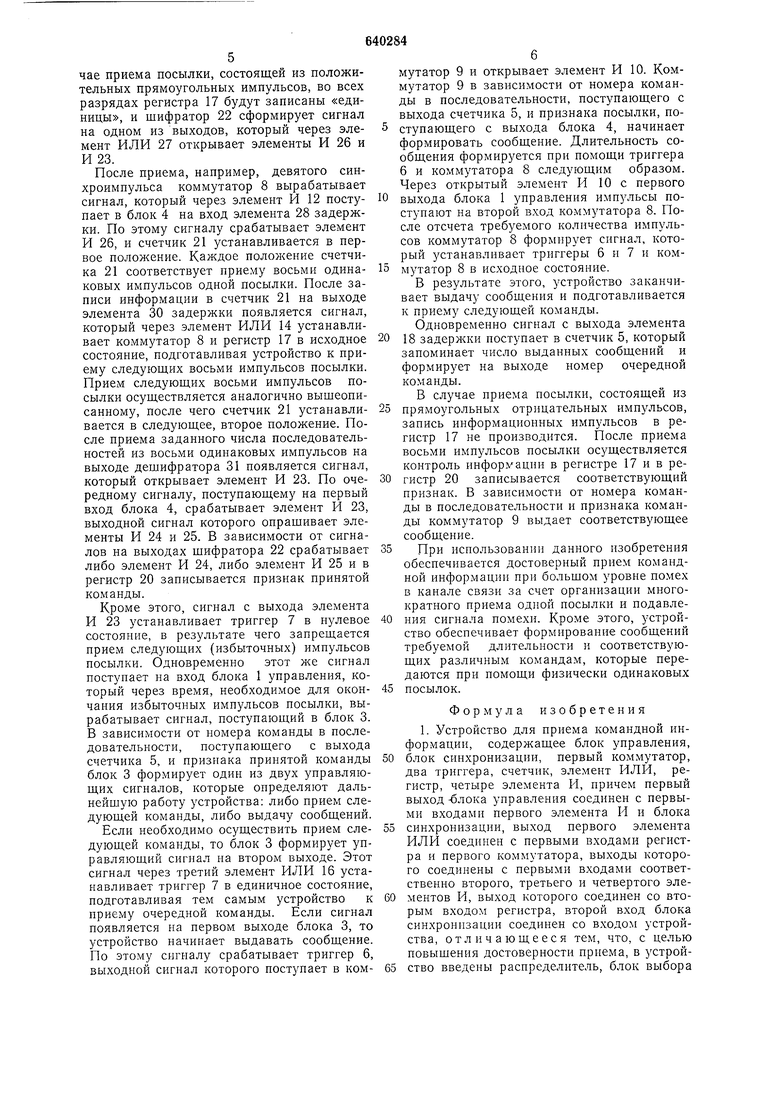

первым входом блока анализа частичной выборки информации, второй вход которого соединен с выходом регистра, выход третьего элемента ИЛИ соединен с единичным входом второго триггера, нулевой выход 5 которого через второй элемент И соединен с входом элемента задержки, выход счетчика соединен со вторым входом второго коммутатора и первым входом блока выбора режима, второй вход которого соединен со Ю вторым выходом блока управления, вход которого соединен с первым выходом блока анализа частичной выборки информации и нулевым входом второго триггера, второй вход первого элемента ИЛИ соединен со 15 вторым выходом блока анализа частичной выборки информации, третий выход которого соединен с третьими входами второго коммутатора и блока выбора режима, первый выход которого соединен с единичным 20 входом первого триггера, второй вход третьего элемента ИЛИ и второй выход блока выбора режима соединены с первым выходом устройства, выход второго коммутатора соединен со вторым выходом устройства, и 25 тем, что, блок анализа частичной выборки информации содержит шифратор, дешифратор, регистр, счетчик, три элемента задержки, четыре элемента И и элемент ИЛИ, причем вход первого элемента задержки 30 соединен с первыми входами блока и первого элемента И, выход которого соединен с первым выходом блока, входами второго и третьего элементов И и через второй элемент задержки со входом счетчика, выходы 35 шифратора через второй и третий элементы И соединены со входами регистра и через элемент ИЛИ - со вторым входом первого элемента И и входом четвертого элемента И, выход которого через последовательно 40 соединенные счетчик и дешифратор соедийен с третьим входом первого элемента И, выход первого элемента задержки соединен с входом четвертого элемента И и через третий элемент задержки со вторым 45 выходом блока, второй вход и третий выход которого соединены соответственно со входом шифратора и выходом регистра. Блок-схема устройства приведена на фиг. 1. Структурная схема блока анализа 50 частичной выборки информации приведена на фиг. 2. Устройство для приема командной информации содержит блок 1 управления, блок 2 синхронизации, блок 3 выбора ре- 55 жима, блок 4 анализа частичной выборки информации, счетчик 5, триггеры 6, 7, коммутаторы 8, 9, элементы И 10... 13, элементы ИЛИ 14... 16, регистр 17, элемент 18 задержки и распределитель 19.60 Блок 4 анализа частичной выборки информации содержит регистр 20, счетчик 21, шифратор 22, элементы И 23... 26, элемент ИЛИ 27, элементы 28... 30 задержки, дешифратор 31. 65 Устройство работает следующим образом. На вход устройства поступает последовательность команд. Информация, содержащаяся в каждой команде, закодирована, вопервых, номером команды в последовательности и, во-вторых, видом посылки, с помощью которой передается эта команда. (Посылка есть последовательность импульсов одинаковой формы. Количество видов посылок определяется количеством используемых форм импульсов). Количество импульсов одинаковой формы в посылке выбирается в зависимости от уровня помех в канале связи. Перед началом работы триггер 7 устанавливается в единичное состояние, а триггер 6 и элементы памяти, содержащиеся в блоке 1 управления, блоке 2 синхронизации. блоке 3 выбора режима, счетчики 5 и 21, коммутатор 8, регистры 17 и 20 устанавливаются в нулевое положение (цепи установки элементов памяти на фиг. 1 и фиг. 2 не показаны). Работа устройства начинается с момента прихода импульсов посылки на второй вход блока 2 синхронизации, который служит для привязки поступающих импульсов к внутренней частоте. С выхода блока 2 синхронизации импульсы поступают на вход распределителя 19, который служит для анализа формы входного сигнала. В зависимости от формы входного сигнала распределитель 19 формирует импульсы на соответствующих выходах. Так, например, при поступлении на вход распределителя 19 импульсов отрицательной полярности, импульсы появляются только на первом выходе. В случае приема посылки, состоящей из прямоугольных положительных импульсов, на обоих выходах распределителя 19 появляются импульсы (на втором выходе - информационные импульсы, а на первом - синхроимпульсы). Синхроимпульсы через элемент ИЛИ 15 поступают на вход коммутатора 8, который служит для подсчета количества импульсов, поступающих в устройство и управляет записью информации в регистр 17. При поступлении первого синхроимпульса коммутатор 8 вырабатывает сигнал, который открывает элемент И 13 и первый информационный импульс, сформированный на втором выходе распределителя 19, записывается в первый разряд регистра 17. При поступлении второго синхроимпульса элемент И 13 срабатывает таким образом, что второй информационный импульс записывается во второй разряд регистра 17. Аналогично осуществляется запись в регистр 17 следующих импульсов посылки, поступающей на вход устройства. Информация, содержащаяся в регистре 17 поступает в блок 4 анализа частичной выборки информации на вход шифратора 22. В сл}чае приема посылки, состоящей из положительных прямоугольных импульсов, во всех разрядах регистра 17 будут записаны «единицы, и шифратор 22 сформирует сигнал на одном из выходов, который через элемент ИЛИ 27 открывает элементы И 26 и И 23.

После приема, например, девятого синхроимпульса коммутатор 8 вырабатывает сигнал, который через элемент И 12 поступает в блок 4 на вход элемента 28 задержки. По этому сигналу срабатывает элемент И 26, и счетчик 21 устанавливается в первое положение. Каждое положение счетчика 21 соответствует приему восьми одинаковых импзльсов одной посылки. После записи информации в счетчик 21 на выходе элемента 30 задержки появляется сигнал, который через элемент ИЛИ 14 устанавливает коммутатор 8 и регистр 17 в исходное состояние, подготавливая устройство к приему следующих восьми импульсов посылки. Прием следующих восьми импульсов посылки осуществляется аналогично вышеописанному, после чего счетчик 21 устанавливается в следующее, второе положение. После приема заданного числа последовательностей из восьми одинаковых импульсов на выходе дешифратора 31 появляется сигнал, который открывает элемент И 23. По очередному сигналу, поступающему на первый вход блока 4, срабатывает элемент И 23, выходной сигнал которого опрашивает элементы И 24 и 25. В зависимости от сигналов на выходах шифратора 22 срабатывает либо элемент И 24, либо элемент И 25 и в регистр 20 записывается признак принятой команды.

Кроме этого, сигнал с выхода элемента И 23 устанавливает триггер 7 в пулевое состояние, в результате чего запрещается прием следующих (избыточных) импульсов посылки. Одновременно этот же сигнал поступает на вход блока 1 управления, который через время, необходимое для окончания избыточных импульсов посылки, вырабатывает сигнал, поступающий в блок 3. В зависимости от номера команды в последовательности, поступающего с выхода счетчика 5, и признака принятой команды блок 3 формирует один из двух управляющих сигналов, которые определяют дальнейшую работу устройства: либо прием следующей команды, либо выдачу сообщений.

Если необходимо осуществить прием следующей команды, то блок 3 формирует управляющий сигнал на втором выходе. Этот сигнал через третий элемент ИЛИ 16 устанавливает триггер 7 в единичное состояние, подготавливая тем самым устройство к приему очередной команды. Если сигнал появляется на первом выходе блока 3, то устройство начинает выдавать сообщение. По этому сигиалу срабатывает триггер 6, выходной сигнал которого поступает в коммутатор 9 и открывает элемент И 10. Коммутатор 9 в зависимости от номера команды в последовательности, поступающего с выхода счетчика 5, и признака посылки, поступающего с выхода блока 4, начинает формировать сообщение. Длительность сообщения формируется при помощи триггера 6 и коммутатора 8 следующим образом. Через открытый элемент И 10 с первого

выхода блока 1 управления импульсы поступают на второй вход коммутатора 8. После отсчета требуемого количества импульсов коммутатор 8 формирует сигнал, который устанавливает триггеры 6 и 7 и коммутатор 8 в исходное состояние.

В результате этого, устройство заканчивает выдачу сообщения и подготавливается к приему следующей команды. Одновременно сигнал с выхода элемента

18 задержки поступает в счетчик 5, который запоминает число выданных сообщений и формирует на выходе номер очередной команды.

В случае приема посылки, состоящей из

прямоугольных отрицательных импульсов, запись информационных импульсов в регистр 17 не производится. После приема восьми импульсов посылки осуществляется контроль инфоруацни в регистре 17 и в регистр 20 записывается соответствующий признак. В зависимости от номера команды в последовательности и признака команды коммутатор 9 выдает соответствующее сообщение.

При использовании данного изобретения обеспечивается достоверный прием командной информации при большом уровне помех в канале связи за счет организации многократного приема одной посылки и подавления сигнала помехи. Кроме этого, устройство обеспечивает формирование сообщений требуемой длительности и соответствующих различным командам, которые передаются при помощи физически одинаковых

посылок.

Формула изобретения

1. Устройство для приема командной информации, содерл ащее блок управления,

блок синхронизации, первый коммутатор, два триггера, счетчик, элемент ИЛИ, регистр, четыре элемента И, причем первый выход -блока управления соединен с первыми входами первого элемента И и блока

синхронизации, выход первого элемента ИЛИ соединен с первыми входами регистра и первого коммутатора, выходы которого соединены с первыми входами соответственно второго, третьего и четвертого элементов И, выход которого соединен со вторым входом регистра, второй вход блока синхронизации соединен со входом устройства, отличающееся тем, что, с целью повышения достоверности приема, в устройство введены распределитель, блок выбора

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Способ вызова объектов и устройство для его осуществления | 1987 |

|

SU1550563A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1396147A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1992 |

|

RU2032938C1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Устройство для подготовки информации на перфоленте | 1977 |

|

SU684549A1 |

| Устройство для передачи и приема информации | 1984 |

|

SU1185365A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

Авторы

Даты

1978-12-30—Публикация

1976-04-21—Подача